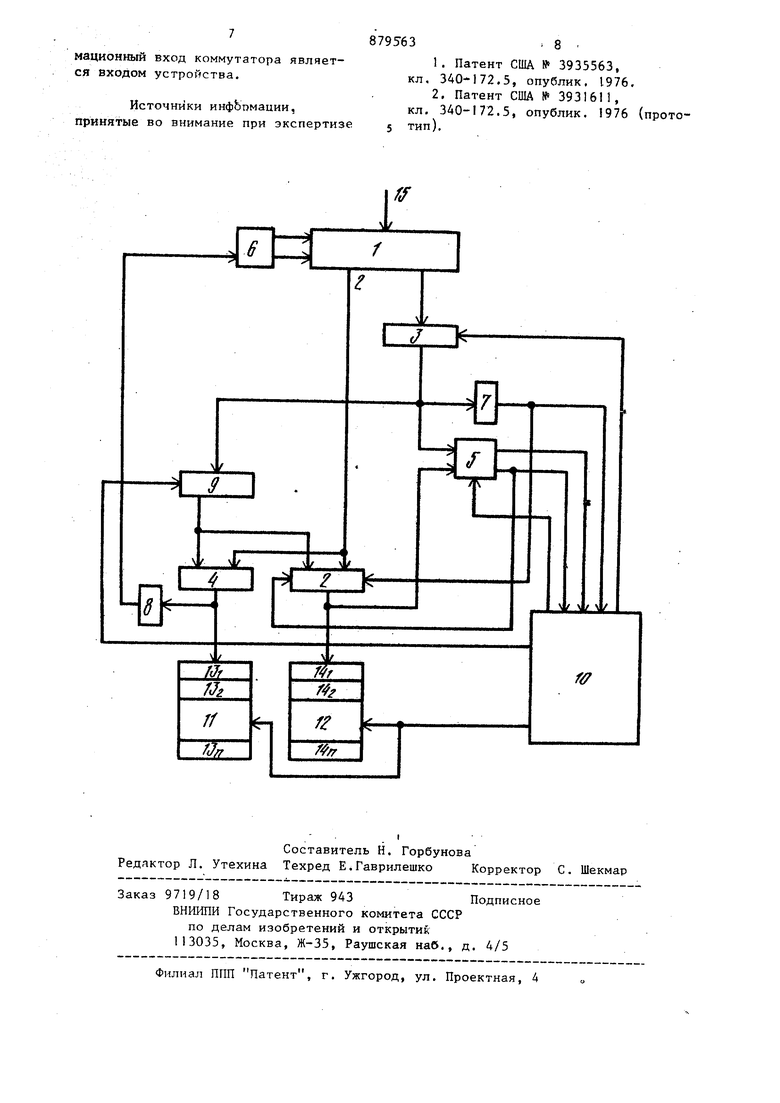

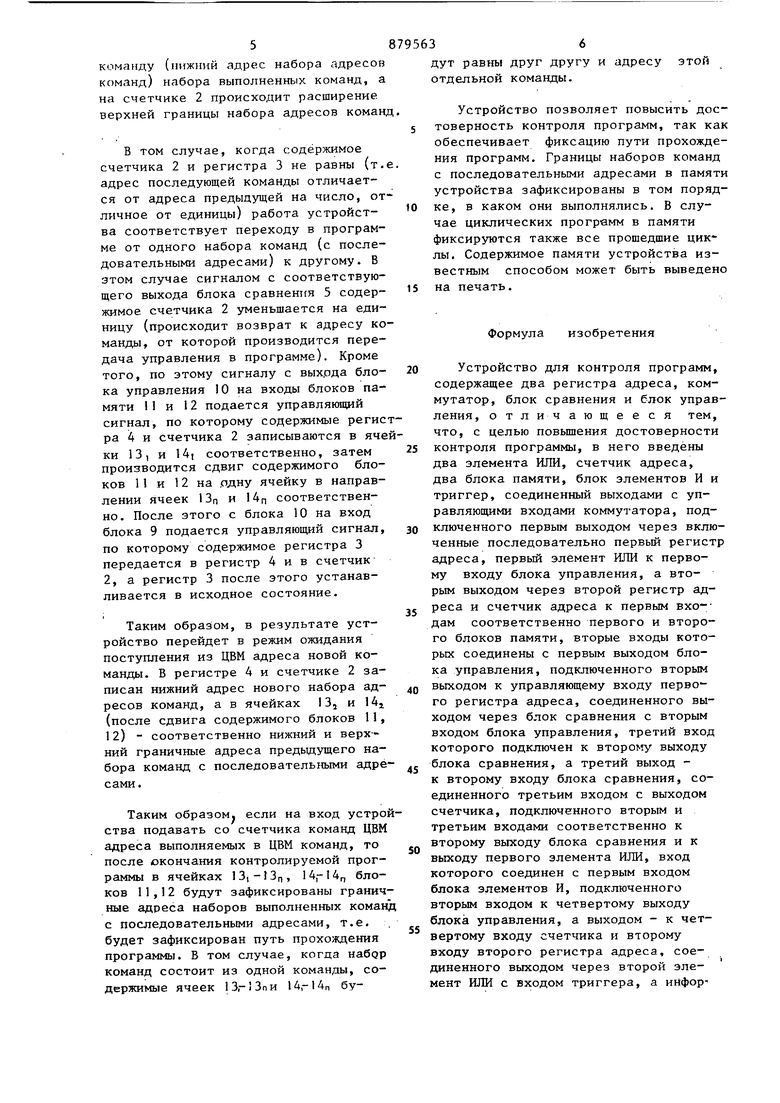

Изобретение относится к области вычислительной техники, в частности к организации контроля и отладки программ. Известно устройство для контроля прохождения программ l , в котором зонная память состоит из трех основ ных частей: быстродействующего запоминающего блока для хранения адре сов , схем селекции и хранения адресов, схем считывания и визуального выврда зафиксированных адресов. Недостаток устройства - малая достоверность контроля программ. Наиболее близким техническим решением к изобретению является устройство 2 . Система обработки содержи главную память,блок команд, блок кон роля памяти, блок канала, блок исполн ния, пульт управления и устройство состоящее из коммутатора, регистра верхней границы адресов, регистра нижней границы адресов, регистра нижнего адреса программы, регистра количества адресов, используемых в системе, от нижнего адреса программы до верхнего адреса программы, блоков сравнения границ адресов, логической схемы и распределителя импульсов. Недостаток прототипа заключается в малой достоверности контроля программ, так как устройство не позволяет фиксировать путь прохождения программы. Устройство проверяет, входят ли адреса выполняемых команд в разрешен- ный диапазон адресов, но адреса использованных в программах команд с учетом переходов и циклических участков не фиксирутотся. Целью изобретения является повышение достоверности контроля программ. Поставленная цель достигается тем, что в устройство для контроля программ, содержащее два региЬтра, коммутатор, блок сравнения и блок уп 38 равления, введены два элемента ИЛИ, счетчик (адреса), два блока памяти, блок элементов И и триггер, соединенный выходами с первыми входами коммутатора, подключенного первым выходом через включенные последовательно первый регистр адреса и первый элемент ИЛИ к первому входу бло ка управления, а вторым входом через второй регистр адреса и счетчик адреса - к первым входам соответственно первого и второго блоков памяти, вторые входы которых соединены с пер вым входом блока управления, подключенного вторым входом ко второму ВХО ду первого регистра, соединенного выходом через блок сравнения со вторым входом блока управления. Третий вход последнего подключен ко второму выходу блока сравнения, а третий выход - ко второму входу блока сравнения, соединенного третьим входом с выходом счетчика, подключенного вторым и третьим входами соответственно ко второму выходу блока сравнения и к выходу первого элемента ИЛИ, вход которого соединен с первым входом блока элементов И, подключенного вторым входом к четвертому выходу блока управления, а выходом к четвертому входу счетчика и ко втором входу второго регистра адреса, соединенного выходом через второй элемент ИЛИ со входом триггера. Инфор«мационный вход коммутатора является входом устройства. На чертеже дана функциональная схема устройства. Устройство содержит коммутатор 1 счетчик адреса 2, первый 3 и второй 4 регистры адреса, блок сравнения 5 триггер 6, первый 7 и второй 8 элементы ИЛИ, блок элементов И 9, блок управления 10, первый 11 и второй 12 блоки памяти и ячейки памяти 13, 13п и 14,- 14п. Устройство работает следующим об разом. В исходном состоянии (цепи установки узлов устройства в исходном с тоянии на чертеже не показаны) все регистры, счетчик, ячейки блоков па мяти не содержат информации, тригге 6 находится в состоянии О, а бло управления - в состоянии ожидания сигнала с выхода триггера 6. Блок подключает вход 15 устройства ко вх ду регистра 4 и счетчика 2. Алрес начальной команды програмы (нижняя граница набора адресов коанд) по сигналу изменения адреса оманды записываются в счетчик 2 и егистр 4. После того, как адрес наальной команды запишется в регистр , сигнал с выхода элемента ИЛИ 8 становит триггер 6 в состояние 1. результате коммутатор отключает ход 15 от входов регистра 4 и счетика 2 и подключает его к входу регистра 3. Такое состояние триггера 6 сохраняется до тех пор, пока устойство не будет установлено в исход ное состояние. После этого устройсто находится в режиме ожидания изенения адреса команды на счетчике команд ЦВМ. Адрес следующей команды, к выполнению которой приступила ЦВМ, по сигналу изменения команды, через блок 1 записывается в регистр 3. В результате сигнал с выхода элемента ИЛИ 7 увеличивает на единицу содержимое счетчика 2 и поступает на вход блока управления 10, который в ответ на него подает управляющий сигнал на вход блока сравнения 5. Блок сравнения 5 сравнивает содержимое регистра 3 и счетчика 2, т.е. сравнивает адреса новой команды с увеличенным на единицу адресом предьщущей команды. В зависимости от результата этого сравнения реализуются два режима работы устройства. Если содержимое регистра 3 равно содержимому счетчика 2 (адреса предыдущей и последующей команд отличаются на единицу, т.е. в ЦВМ выполняются команды с последовательными адресами), то блок управления 10 по сигналу с соответствующего выхода блока сравнения 5 производит гашение регистра 3, и устройство переходит в режим ожидания изменения выполняемой в ЦВМ команды (блок 10 ожидает сигнал с элемента 7). При поступлении на регистр 3 адреса новой команды добавляется 1 в счетчик 2 и сравниваются содержимые регистра 3 и счетчика 2. Если они равны, то вновь производится гашение регистра 3 и переход к ожиданию изменения команды в ЦВМ. Работа устройства в данном случае соответствует выполнению в ЦВМ непрерывной цепочки команд с последовательными адресами. При этом содержимое регистра 4 определяет первую

команду (нижний адрес набора адресов команд) набора выполненных команд, а на счетчике 2 происходит расширение, верхней границы набора адресов коман

В том случае, когда содержимое счетчика 2 и регистра 3 не равны (т. адрес последующей команды отличается от адреса предыдущей на число, отличное от единицы) работа устройства соответствует переходу в программе от одного набора команд (с последовательными адресами) к другому. В этом случае сигналом с соответствующего выхода блока сравнения 5 содержимое счетчика 2 уменьшается на единицу (происходит возврат к адресу команды, от которой производится передача управления в программе). Кроме того, по этому сигналу с выхрда блока управления 10 на входы блоков памяти 11 и 12 подается управляющий сигнал, по которому содержимые регисра 4 и счетчика 2 записываются в ячеки 13, и 14i соответственно, затем производится сдвиг содержимого блоков 11 и 12 на рдну ячейку в направлении ячеек 13п и 14п соответственно. После этого с блока 10 на вход блока 9 подается управляющий сигнал, по которому содержимое регистра 3 передается в регистр 4 и в счетчик 2, а регистр 3 после этого устанавливается в исходное состояние.

Таким образом, в результате устройство перейдет в режим ожидания поступления из ЦВМ адреса новой команды. В регистре 4 и счетчике 2 записан нижний адрес нового набора адресов команд, а в ячейках 13j и 14 (после сдвига содержимого блоков 11, 12) - соответственно нижний и верх-ний граничные адреса предыдущего набора команд с последовательными адре сами.

Таким образом, если на вход устройства подавать со счетчика команд ЦВМ адреса выполняемых в ЦВМ команд, то после окончания контролируемой программы в ячейках 13,-13п, 14,-14г, блоков 11,12 будут зафиксированы граничные адреса наборов выполненных команд с последовательными адресами, т.е. будет зафиксирован путь прохождения программы. В том случае, когда набор команд состоит из одной команды, содержимые ячеек 13,- Зп и 14,- 4п будут равны друг другу и адресу этой отдельной команды.

Устройство позволяет повысить достоверность контроля программ, так как обеспечивает фиксацию пути прохождения программ. Границы наборов команд с последовательными адресами в памяти устройства зафиксированы в том порядке, в каком они выполнялись. В случае циклических программ в памяти фиксируются также все прошедшие циклы. Содержимое памяти устройства известным способом может быть выведено на печать.

Формула изобретения

Устройство для контроля программ, содержащее два регистра адреса, коммутатор, блок сравнения и блок управления, отличающееся тем, что, с целью повьш1ения достоверности контроля программы, в него введены два элемента ИЛИ, счетчик адреса, два блока памяти, блок элементов И и триггер, соединенный выходами с управляющими входами коммутатора, подключенного первым выходом через включенные последовательно первый регистр адреса, первый элемент ИЛИ к первому входу блока управления, а вторым выходом через второй регистр адреса и счетчик адреса к первым вхо-дам соответственно первого и второго блоков памяти, вторые входы которых соединены с первым выходом блока управления, подключенного вторым выходом к управляющему входу первого регистра адреса, соединенного выходом через блок сравнения с вторым входом блока управления, третий вход которого подключен к втopo ry выходу блока сравнения, а третий выход к второму входу блока сравнения, соединенного третьим входом с выходом счетчика, подключенного вторым и третьим входами соответственно к второму выходу блока сравнения и к выходу первого элемента ИЛИ, вход которого соединен с первым входом блока элементов И, подключенного вторым входом к четвертому выходу блока управления, а выходом - к четвертому входу счетчика и второму входу второго регистра адреса, соединенного выходом через второй элемент ИЛИ с входом триггера, а информационный вход коммутатора является входом устройства. Источники инфЬпмации, принятые во внимание при экспертизе 879563. 8 1.Патент США № 3935563, кл, 340-172.5, опублик. 1976. 2.Патент США № 3931611, кл. 340-172.5, опублик. 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1980 |

|

SU879564A1 |

| Устройство для контроля хода программ | 1979 |

|

SU983712A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для контроля хода программ | 1980 |

|

SU1057949A1 |

| Устройство для ввода информации от датчиков | 1980 |

|

SU981981A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для защиты памяти | 1980 |

|

SU942162A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Адаптер канал-канал | 1982 |

|

SU1067492A1 |

У I

ff

1

/ т

f f

fff

Авторы

Даты

1981-11-07—Публикация

1980-01-31—Подача