(5) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программ | 1979 |

|

SU983712A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для контроля хода программ | 1980 |

|

SU1057949A1 |

| Устройство для контроля программ | 1980 |

|

SU879563A1 |

| Устройство для контроля программ | 1980 |

|

SU879564A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

1

Изобретение относится к запоминающим устройствам, в частности к организации защиты памяти программ.

Известно устройство, которое содержит последовательно соединенные дешифратор адресов зон и блок сравнения, входы которого подключены к первому и второму входам устройства ГОНедостаток данного устройства состоит в том, что при его использовании мала вероятность выявления ошибочных или несанкционированных обращений, к памяти, так как оно обеспечивает фиксацию отклонения от определяемой программой последовательности обращений к памяти программ лишь в том случае, когда отклонение выходит за пределы зоны разрешенных адресов.

Наиболее близким по технической сущности к предлагаемому является устройство для защиты памяти, содержащее адресный регистр, М регистров первой группы (где М - число различных областей памяти, к которым программа имеет право доступа), в каждый из которых записывается нижняя граница определенной зоны разрешенных адресов, М регистров второй группы, из которых в каждый записывается верхняя граница зоны разрешенных адресов, М блоков сравнения текущего адреса с нижней границей адресов, М блоков сравнения текущего адреса с верхней границей адресов, М элеtoментов И, а также элемент ИЛИ, причем выход каждого регистра первой группы соединен с первым входом соответствующего ему блока сравнения текущего адреса с нижней границей ад15ресов, выход каждого регистра второй группы соединен с первым входом блока сравнения текущего адреса с верхней границей адресов, вторые входы всех блоков сравнения соединены с вы20ходами адресного регистра, вход которого является входом устройства, входы каждого элемента И соединены с выходами блоков сравнения текуще39

го адреса с верхней и нижней границами одной из разрешенных зон адресов, выходы элементов И соединены с соответствующим входом элемента ИЛИ 121.

Основным недостатком известного устройства является то, что при его использовании мала вероятность выявления ошибочных или несанкционированных обращений к памяти, так как они обеспечивают фиксацию отклонения от определяемой программой последовательности обращений к памяти программ лишь в трех случаях, когда отклонение выходит за пределы зоны разрешенных адресов, что снижает надежность устройства.

Цель изобретения - повышение надежности устройства за счет увеличения вероятности выявления ошибочных или несанкционированных обращений, к памяти программ.

Указанная цель достигается тем, что в устройство для защиты памяти, содержащее регистр адреса, первый элемент ИЛИ, первую группу последо;вательно соединенных регистров адреса , выходы которых подключены к первым входам соответствующих схем сравнения выходы которых соединены с первыми входами элементов И группы, вторую группу последовательно соединенных регистров адреса, выходы которых подключены к вторым входам элемен-. тов И группы, введены счетчи-к текущего адреса, регистр числа, второй элемент ИЛИ, триггер, первую и вторую дополнительные схемы сравнения, блок местного управления, дополнительные группы элементов И и группу элементов ИЛИ, входы которых подкЛючены к выходам элементов И группы, а выходы - к входу регистра числа, выход которого соединен с первым входом первой дополнительной схемы сравнения, выходы элементов И первой дополнительной группы подключены к одним из входов элементов И второй и третьей дополнительных групп, другие входы которых соединены с выходами триггера, а выходы - с входом регистра адреса и первым входом счетч ика текущего адреса, второй вход которого подключен к выходам элементов И четвертой дополнительной группы элементов И, выход счетчика текущего адреса подключен к входам второго элемента ИЛИ, к первому входу второй

24

дополнительной схемы сравнения, входам элементов И пятой дополнительной группы, выходы которых соединены с вторыми входами схем сравнения, выход регистра адреса подключен к вторым входам дополнительных схем сравнения, входам элементов И четвертой дополнительной группы и входам первого элемента ИЛИ, выход которого

0 соединен с одним из входов блока местного управления, другие входы которого подключены к выходам дополнительных схем сравнения, а выходы соединены с управляющими входами регистра адреса, регистра числа, дополнительных схем сравнения, счетчика текущего адреса и элементов И четвертой и пятой дополнительных групп, выход второго элемента ИЛИ

0 подключен к одному из входов триггера.

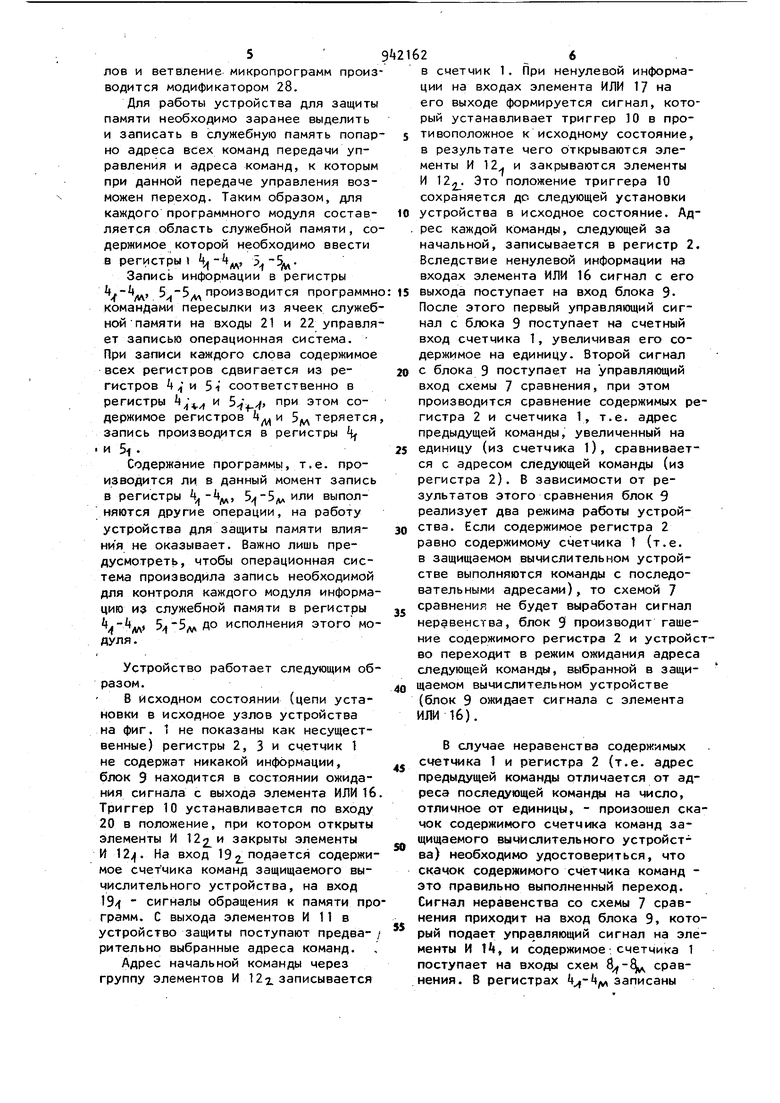

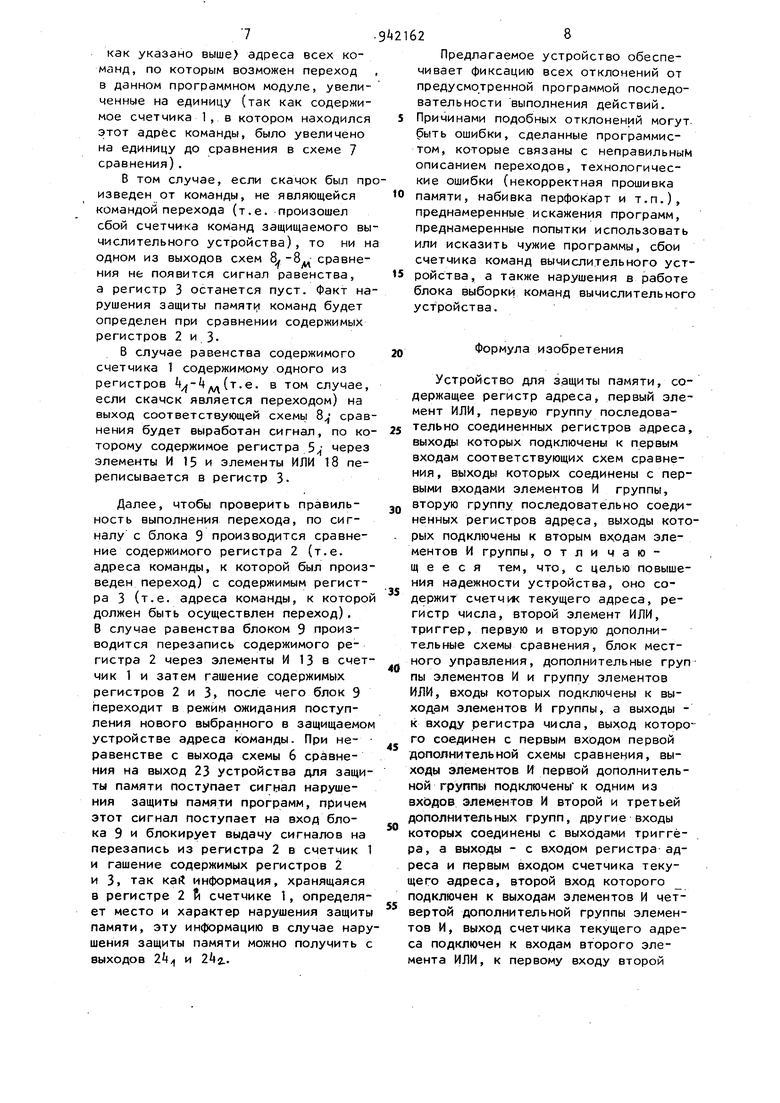

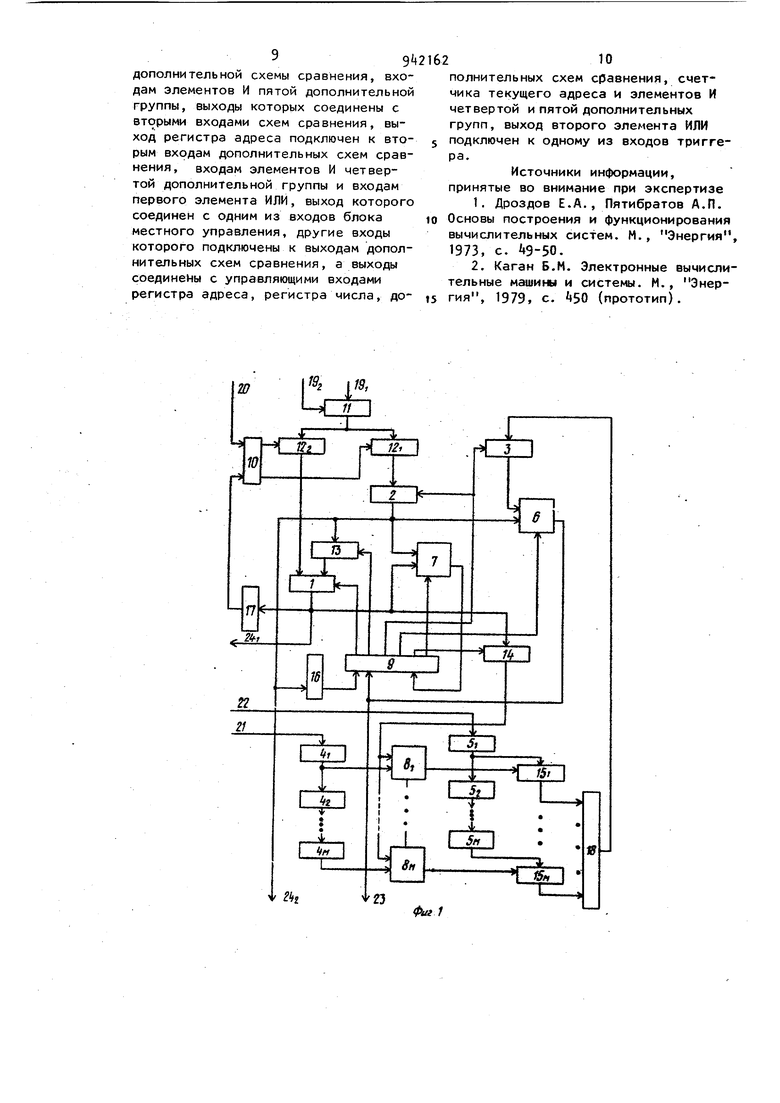

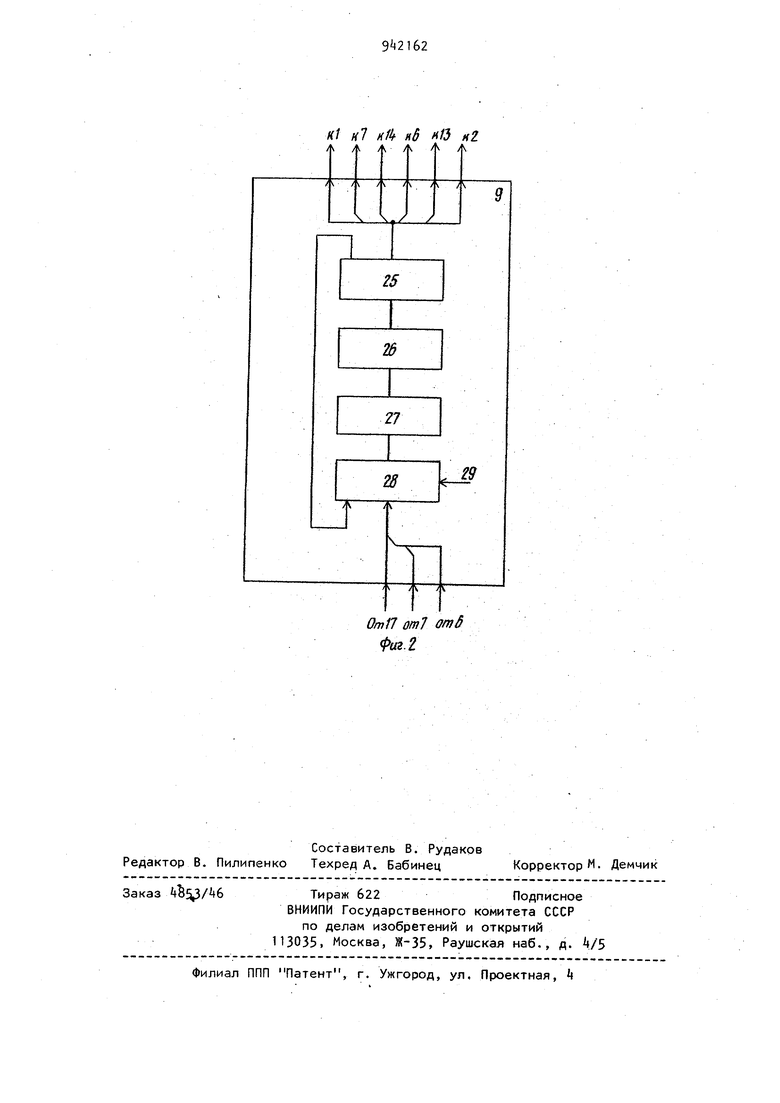

На фиг. 1 приведена функциональная схема устройства для защиты памяти; на фиг. 2 - функциональная схема возможного варианта построения блока местного управления.

Устройство (фиг. 1) состоит из счетчика 1 текущего адреса, регистР ра 2 адреса, регистра 3 числа, первой группы регистров адреса, второй группы регистров адреса, первой 6 и второй 7 дополнительных схем сравнения, схем сравнения, блока 9 местного управления, триггера 10, первой 11, второй 12, третьей 12, четвертой 13 и пятой 14 дополнительных групп элементов И, группы элементов И 15/(1 первого 16 и второго 17 элементов ИЛИ, группы элементов ИЛИ 18.

Устройство имеет входы 19 информации, 192. управляющий, 20 установки в исходное состояние, 21 и 22 записи служебной информации, выходы 23 нарушения защиты, 2k и 2 информации о нарушении защиты.

Блок 9 местного управления(фиг.2) может быть реализован на основе

микропрограммного способа управления. Он состоит из блока 25 постоянной памяти, дешифратора 26 адреса микрокоманд, регистра 27 адреса микрокоманд, модификатора 28, имеющего вход

29 начальной установки. Блок 9 работает в соответствии с микропрограммой, записанной в блоке 25 постоянной памяти, а анализ внешних сигналов и ветвление микропрограмм производится модификатором 28.

Для работы устройства для защиты памяти необходимо заранее выделить и записать в служебную память попарно адреса всех команд передачи управления и адреса команд, к которым при данной передаче управления возможен переход. Таким образом, для каждого программного модуля составляется область служебной памяти, содержимое которой необходимо ввести в регистры) Ц-, 5 5длЗапись информации в регистры ij.-, 5.-5д производится программно командами пересылки из ячеек служебной памяти на входы 21 и 22 управляет записью операционная система. При записи каждого слова содержимое всех регистров сдвигается из регистров 5i соответственно в

регистры и Р ° держимое регистров д, и 5дд теряется запись производится в регистры

и Sf .

Содержание программы, т.е. производится ли в данный момент запись в регистры , 5у -5ддили выполняются другие операции, на работу устройства для защиты памяти влияния не оказывает. Важно лишь предусмотреть, чтобы операционная система производила запись необходимой для контроля каждого модуля информацию из служебной памяти в регистры yf vw до исполнения этого модуля .

Устройство работает следующим образом.

В исходном состоянии (цепи установки в исходное узлов устройства на фиг. 1 не показаны как несущественные) регистры 2, 3 и счетчик 1 не содержат никакой информации, блок 9 находится в состоянии ожидания сигнала с выхода элемента ИЛИ 16 Триггер 10 устанавливается по входу 20 в положение, при котором открыты элементы И закрыты элементы И . На вход 192. подается содержимое счетчика команд защищаемого вычислительного устройства, на вход 19/f сигналы обращения к памяти программ. С выхода элементов И 11 в устройство защиты поступают предва- / рительно выбранные адреса команд.

Адрес начальной команды через группу элементов И 122. записывается

в счетчик 1. При ненулевой информации на входах элемента ИЛИ 17 на его выходе формируется сигнал, который устанавливает триггер 10 в противоположное к исходному состояние, в результате чего открываются элементы И 12, и закрываются элементы И 122. Это положение триггера 10 сохраняется до следующей установки

0 устройства в исходное состояние. Ад. рее каждой команды, следующей за начальной, записывается в регистр 2. Вследствие ненулевой информации на входах элемента ИЛИ 16 сигнал с его

5 выхода поступает на вход блока 9После этого первый управляющий сигнал с блока 9 поступает на счетный вход счетчика 1, увеличивая его содержимое на единицу. Второй сигнал

0 с блока 9 поступает на управляющий вход схемы 7 сравнения, при этом производится сравнение содержимых регистра 2 и счетчика 1, т.е. адрес предыдущей команды, увеличенный на

5 единицу (из счетчика 1), сравнивается с адресом следующей команды (из регистра 2). В зависимости от результатов этого сравнения блок 9 реализует два режима работы устройства. Если содержимое регистра 2 равно содержимому счетчика 1 (т.е. в защищаемом вычислительном устройстве выполняются команды с последовательными адресами), то схемой 7 сравнения не будет выработан сигнал неравенства, блок 9 производит гашение содержимого регистра 2 и устройство переходит в режим ожидания адреса следующей команда, выбранной в защищаемом вычислительном устройстве (блок 9 ожидает сигнала с элемента ИЛИ 16).

В случае неравенства содержимых счетчика 1 и регистра 2 (т.е. адрес предыдущей команды отличается от адреса последующей команды на число, отличное от единицы, - произошел скачок содержимого счетчика команд защищаемого вычислительного устройства) необходимо удостовериться, что скачок содержимого счётчика команд это правильно выполненный переход. Сигнал неравенства со схемы 7 сравнения приходит на вход блока 9, который подает управляющий сигнал на элементы И f, и содержимое счетчика 1 поступает на входы схем сравнения. В регистрах записаны как указано выше) адреса всех команд, по которым возможен переход в данном программном модуле, увеличенные на единицу (так как содержимое счетчика 1, в котором находился этот адрес команды, было увеличено на единицу до сравнения в схеме 7 сравнения). В том случае, если скачок был пр изведен от команды, не являющейся командой перехода (т.е. произошел сбой счетчика команд защищаемого вы числительного устройства), то ни н одном из выходов схем 8/-8.-сравнения не появится сигнал равенства, а регистр 3 останется пуст. Факт на рушения защиты памяти команд будет определен при сравнении содержимых регистров 2 и 3В случае равенства содержимого счетчика 1 содержимому одного из регистров t -tдд(т.е. в том случае, если скачек является переходом) на выход соответствующей схемы 8 срав нения будет выработан сигнал, по ко торому содержимое регистра через элементы И 15 и элементы ИЛИ 18 переписывается в регистр 3. Далее, чтобы проверить правильность выполнения перехода, по сигналу с блока 9 производится сравнение содержимого регистра 2 (т.е. адреса команды, к которой был произ веден переход) с содержимым регист ра 3 (т.е. адреса команды, к которо должен быть осуществлен переход), В случае равенства блоком 9 производится перезапись содержимого регистра 2 через элементы И 13 в счет чик 1 и затем гашение содержимых регистров 2 и 3, после чего блок 9 переходит в режим ожидания поступления нового выбранного в защищаемо устройстве адреса команды. При неравенстве с выхода схемы 6 сравнения на выход 23 устройства для защи ты памяти поступает сигнал нарушения защиты памяти программ, причем этот сигнал поступает на вход блока 9 и блокирует выдачу сигналов на перезапись из регистра 2 в счетчик и гашение содержимых регистров 2 и 3, так кай информация, хранящаяся в регистре 2 ft сметчике 1, определя ет место и характер нарушения защит памяти, эту информацию в случае нар шения защиты памяти можно получить выходов 2 и .. 28 Предлагаемое устройство обеспечивает фиксацию всех отклонений от предусмотренной программой последовательности выполнения действий. Причинами подобных отклонений могут, быть ошибка, сделанные программистом, которые связаны с неправильным описанием переходов, технологические ошибки (некорректная прошивка памяти, набивка перфокарт и т.п.), преднамеренные искажения программ, преднамеренные попытки использовать или исказить чужие программы, сбои счетчика команд вычислительного устройства, а также нарушения в работе блока выборки команд вычислительного устройства. Формула изобретения Устройство для защиты памяти, содержащее регистр адреса, первый элемент ИЛИ, первую группу последовательно соединенных регистров адреса, выходы которых подключены к первым входам соответствующих схем сравнения, выходы которых соединены с первыми входами элементов И группы, вторую группу последовательно соединенных регистров адреса, выходы которых подключены к вторым входам элементов И группы, отли чающееся тем, что, с целью повышения надежности устройства, оно содержит c4eT4kK текущего адреса, регистр числа, второй элемент ИЛИ, триггер, первую и вторую дополнительные схемы сравнения, блок местного управления, дополнительные груп пы элементов И и группу элементов ИЛИ, входы которых подключены к выходам элементов И группы, а выходы к входу регистра числа, выход которого соединен с первым входом первой дополнительной схемы сравнения, выходы элементов И первой дополнительной группы подключены к одним из входов элементов И второй и третьей дополнительных групп, другие входы которых соединены с выходами триггера, а выходы - с входом регистра адреса и первым входом счетчика текущего адреса, второй вход которого подключен к выходам элементов И четвертой дополнительной группы элементов И, выход счетчика текущего адреса подключен к входам второго элемента ИЛИ, к первому входу второй 99 дополнительной схемы сравнения, входам элементов И пятой дополнительной группы, выходы которых соединены с вторыми входами схем сравнения, выход регистра адреса подключен к вторым входам дополнительных схем сравнения, входам элементов И четвертой дополнительной группы и входам первого элемента ИЛИ, выход которого соединен с одним из входов блока местного управления, другие входы которого подключены к выходам дополнительных схем сравнения, а выходы соединены с управляющими входами регистра адреса, регистра числа, до10полнительных схем сравнения, счетчика текущего адреса и элементов И четвертой и пятой дополнительных групп, выход второго элемента ИЛИ подключен к одному из входов триггера. Источники информации, принятые во внимание при экспертизе 1.Дроздов Е.А., Пятибратов А.П, Основы построения и функционирования вычислительных систем. Н., Энергия, 1973, с. . 2.Каган Б,М. Электронные вычислительные машины и системы. М., Энер1979. с. «SO (прототип).

Kf н1 к1 я6 Л/3 н2

ч ./ /

29

V

м /V 1

ОтП от отд Фиг.г

Авторы

Даты

1982-07-07—Публикация

1980-12-12—Подача