1

Изобретение относится к вычислительной технике, в частности к организации контроля программ.

Известно устройство для контроля Прохождения программ, содержащее зонную память, состоящую из трех основных частей: быстродействующего запоминающего блока для хранения адресов, схем селекции и хранения адресов, схем считывания или визуального вывода зафиксированных адресов (1.

Однако в устройстве по типу обращения к памяти вьщеляются определенные контрольные точки, которые фиксируются в запоминающем блоке устройстB i. По факту прохождения программы через контрольные точки .делается вывод о том, что весь участок программы между крнтрольными точками вьшолнен, что не всегда верно. Поэтому устройство не гарантирует контроля программ в части полноты использования команд в программе.

На1{более близким к изобретению по технической сущности- является,устройство, содержащее главную память, блок команд, блок контроля памяти; блок канала, блок исполнения и пульт управления, устройство, состоящее из . регистра верхней гранииы адресов, регистра границы адресов, pierHCTpa нижнего адреса программы, регистра количества адресов используемых в системе, от нижнего ашреса программы до верхнего адреса программы, первый, .второй, третий и четвертый блоки сравнения нижней и верхней границ адресов, нижнего адреса программы и верх- ней границы адресов, верхнего адреса

10 программы и нижней границы адресов, нижнего и верхнего адресов программы, логическую схему, вырабатывающую сигнал записи программных событий, распределитель импульсов, причем выход

is регистра нижней границы адресов соединен с первым входом блока сравнения и с вторым входом третьего блока сравнения, выход регистра верхней границы.адресов соединен с вторым

20 входом первого блока сравнения и с вторым входом второго блока сравнения, выход рег.истра нижнего адреса программы соединен с первыми входами второго, третьего и четвёртого бло25ков сравнения, выход регистра колич,ества адресов соединен с третьим входом третьего блока сравнения и с вторым входом четвертого блока сравнения, выходы блока сравнения соединены с входом логической схемы 2

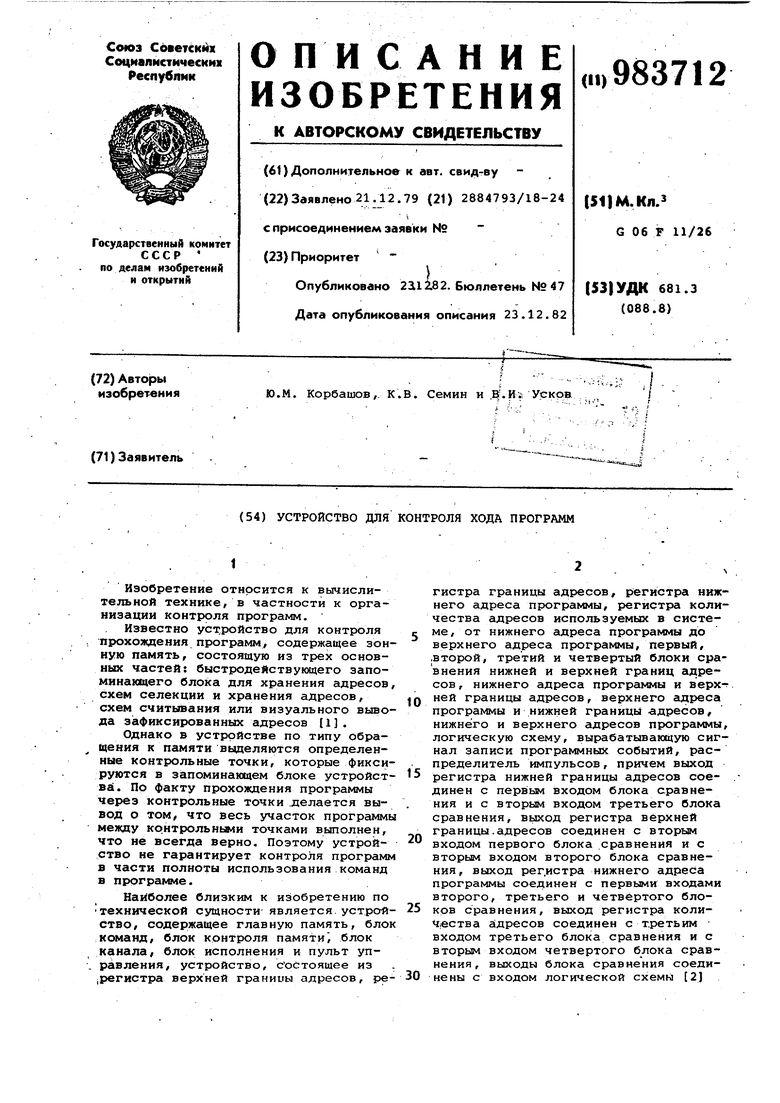

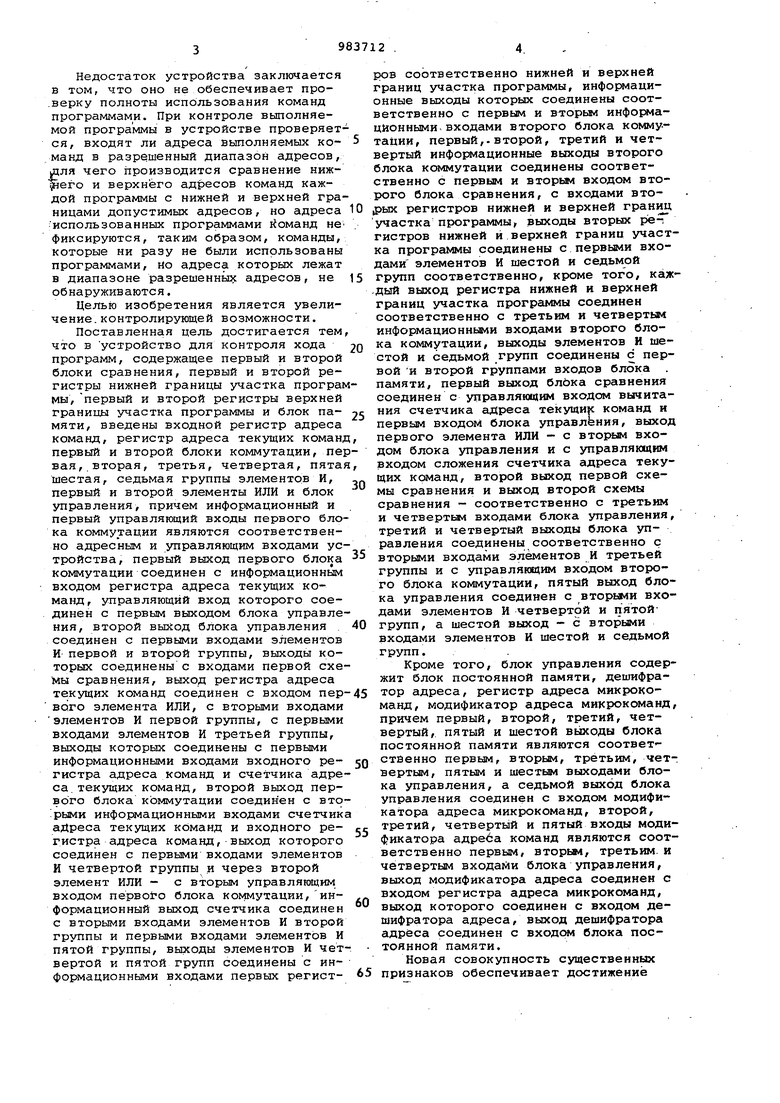

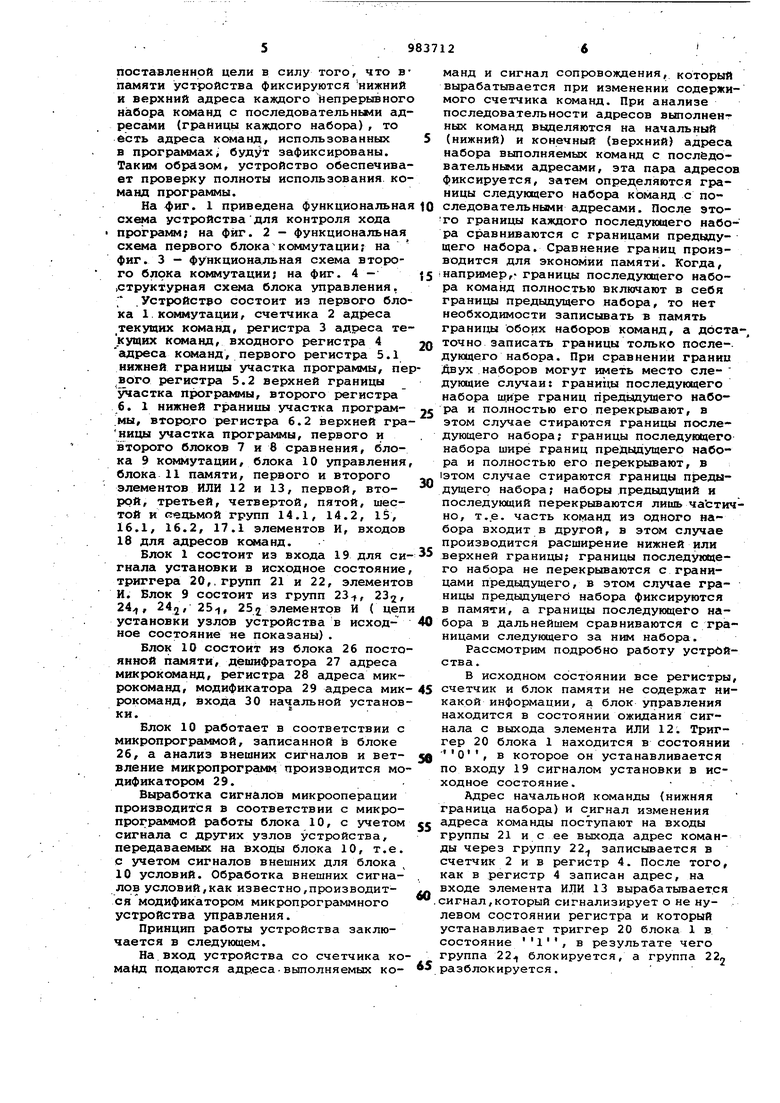

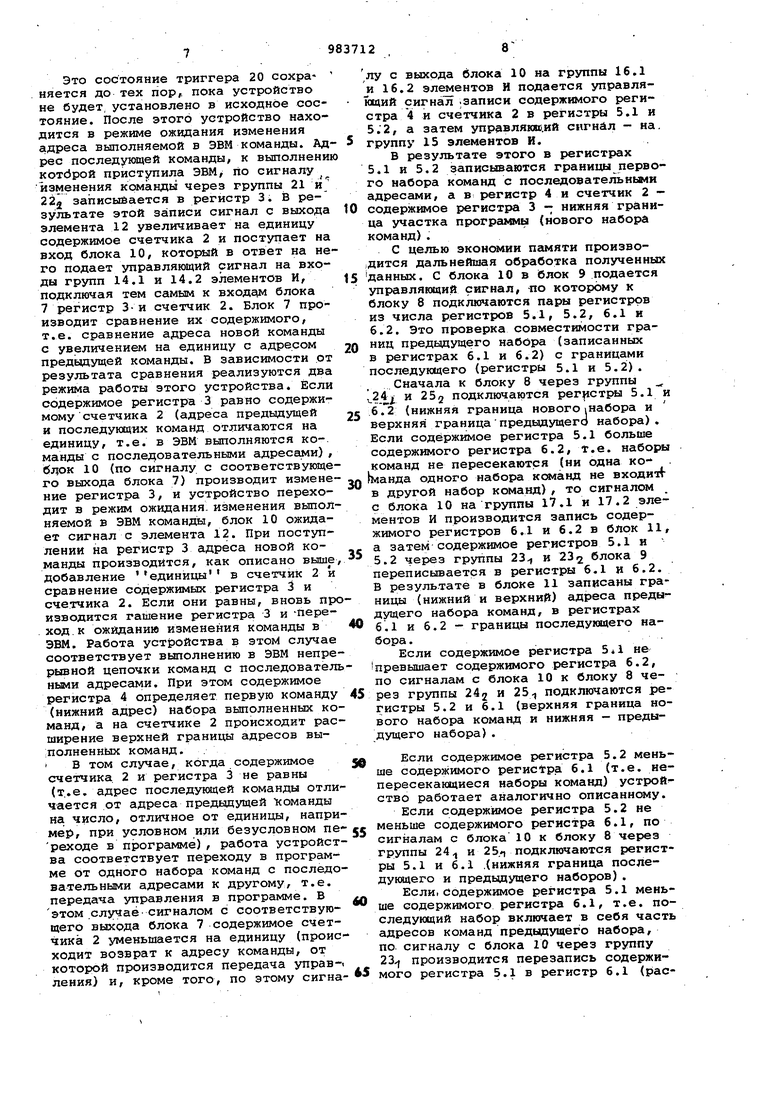

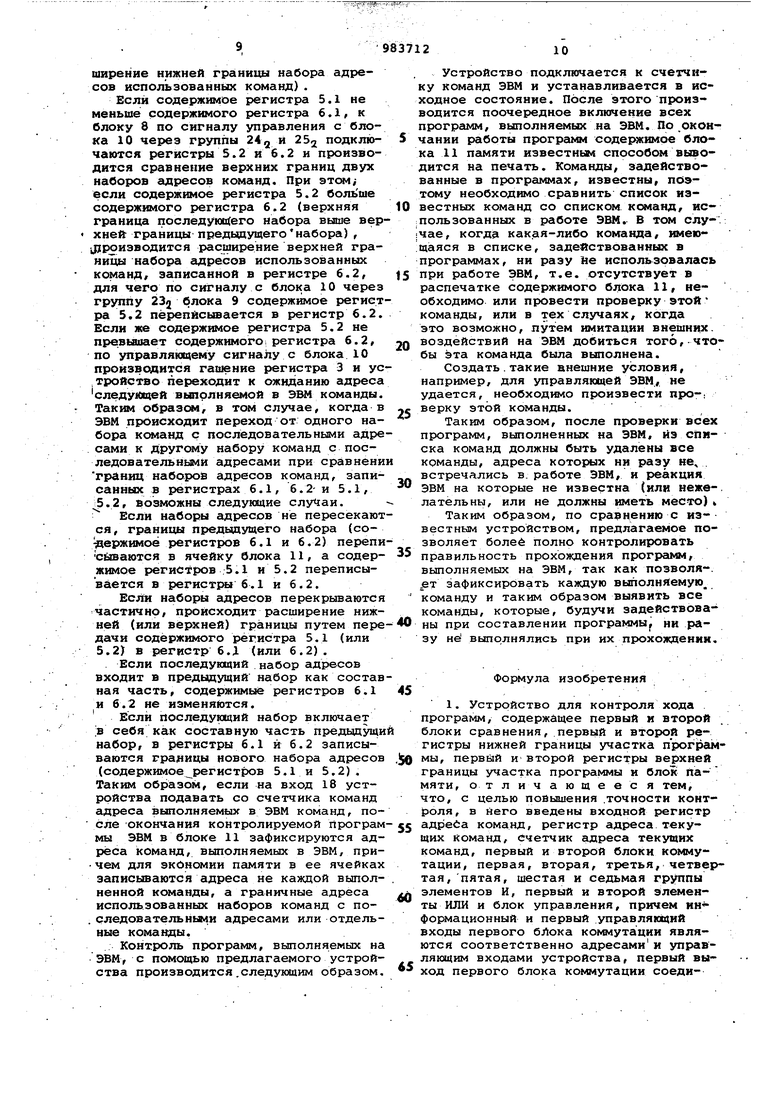

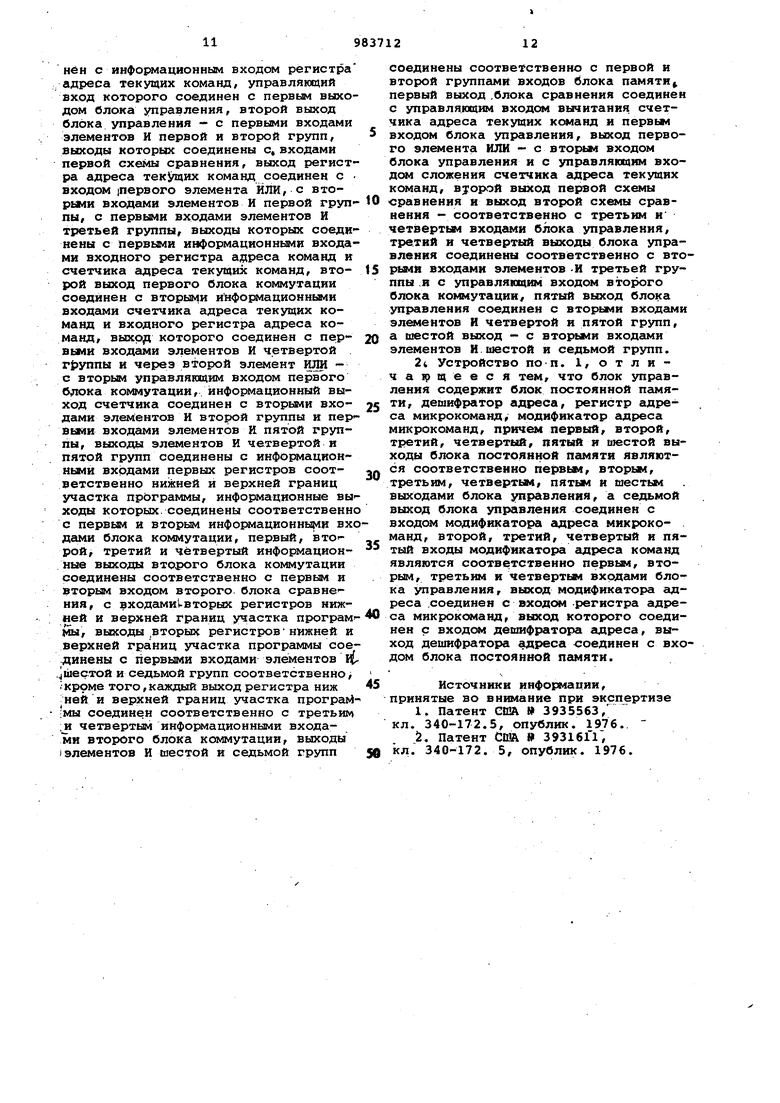

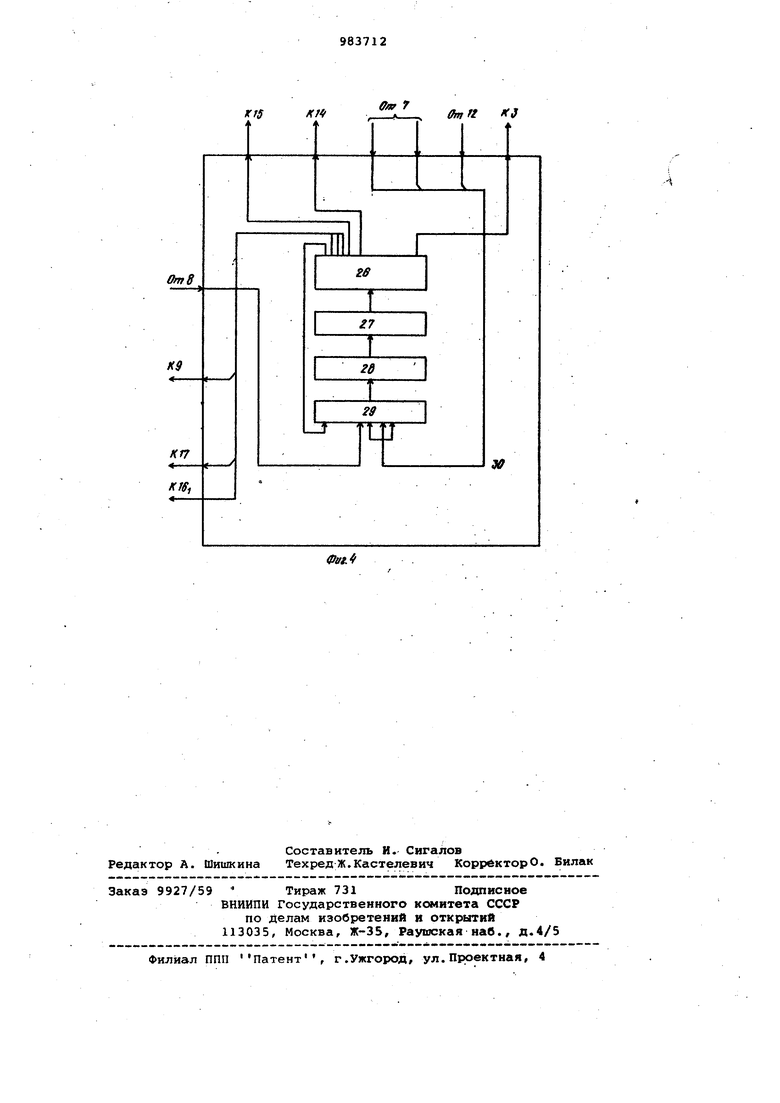

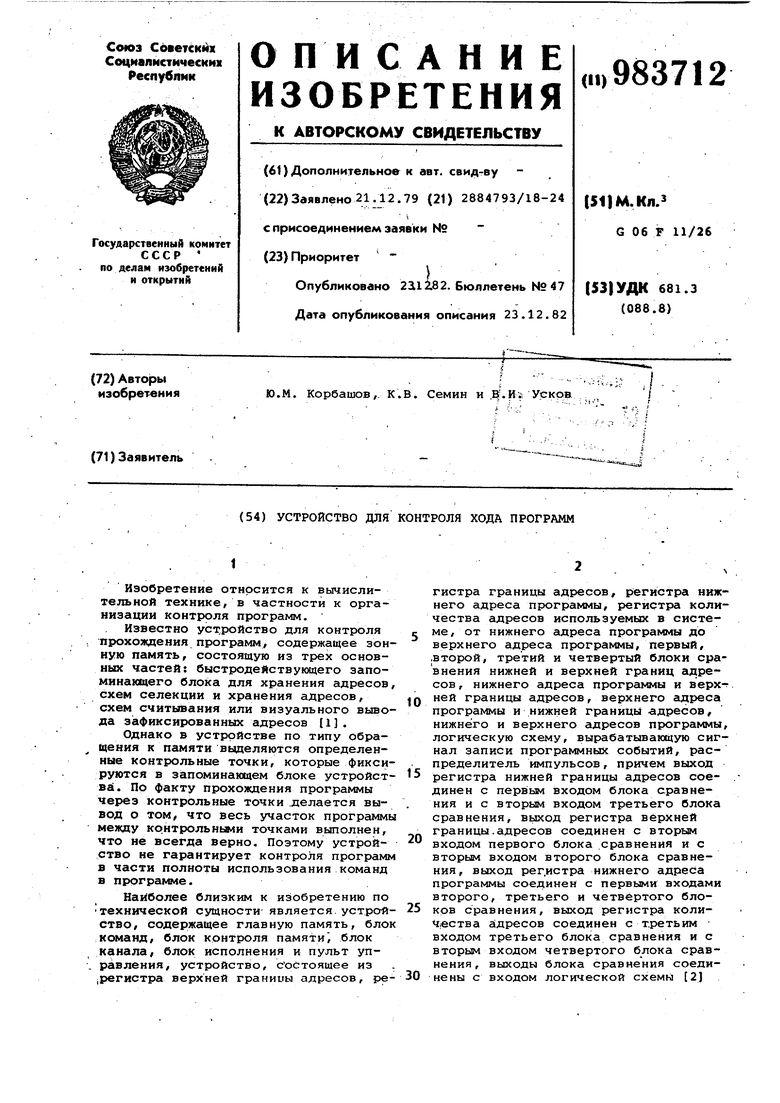

30 Недостаток устройства заключается в том, что оно не обеспечивает про.верку полноты использования команд программами. При контроле выполняемой программы в устройстве проверяет ся, входят ли адреса выполняемых команд в разрешенный диапазон адресов, для чего производится сравнение и верхнего адресов команд каждой программы с нижней и верхней границами допустимых адресов, но адреса использованных программами йоманд не фиксируются, таким образом, команды, которые ни разу не были использованы программами, мо адреса которых лежат в диапазоне разрешенных адресов, не обнаруживаются. Целью изобретения является увеличение, контролирующей возможности. Поставленная цель достигается тем что в устройство для контроля хода программ, содержащее первый и второй блоки сравнения, первый и второй регистры нижней границы участка програм мы, первый и второй регистры верхней границы участка программы и блок памяти, введены входной регистр адреса команд, регистр адреса текущих команд первый и второй блоки коммутации, пер вая,, вторая, третья, четвертая, пятая шестая, седьмая группы элементов И, первый и второй элементы ИЛИ и блок управления, причем информационный и первый управляющий входы первого блока коммутации являются соответственно адресным и управляющим входами устройства, первый выход первого блока коммутации соединен с информационным входом регистра адреса текущих команд, управляющий вход которого соединен с первым выходом блока управления, второй вьйод блока управления соединен с первыми входами элементов И первой и второй группы, выходы которых соединены с входами первой схемы сравнения, выход регистра адреса текущих команд соединен с входом первото элемента ИЛИ, с вторыми входами элементов И первой группы, с первыми входами элементов И третьей группы, выходы которых соединены с первыми информационными входами входного регистра адреса команд и счетчика адреса, текущих команд, второй выход первЬго блока коммутации соединен с вто:рыми информационными входами счетчика адреса текущих команд и входного регистра адреса команд, выход которого соединен с первыми входами элементов И четвертой группы .и через второй элемент ИЛИ - с вторым управляющим входом первого блока коммутации,информационный выход счетчика соединен с вторыми входами элементов И второй группы и первыми входами элементов И пятой группы, выходы элементов И четвертой и пятой групп соединены с информационными входами первых регистров соответственно нижней и верхней границ участка программы, информационные выходы которых соединены соответственно с первым и вторьм информационными входами второго блока коммутации, первый,, второй, третий и четвертый информационные выходы второго блока кснувдутации соединены соответственно с первым и вторьм входом второго блока сравнения, с входами вторых регистров нижней и верхней гранад участка программы, выходы вторых ре гистров нижней и верхней границ участка программы соединены с первыми входами элементов И шестой и седьмой групп соответственно, кроме того, каждый выход регистра нижней и верхней границ участка программы соединен соответственно с третьим и четвертьм информационньми входами второго блока коммутации, выходы элементов И шестой и седьмой групп соединены с первой И второй группами входов блока . памяти, первый выход блока сравнения соединен с управляющим входом вычитания счетчика адреса текущих команд и первым входом блока управления, выход первого элемента ИЛИ - с вторым входом блока управления и с управляющим входом сложения счетчика адреса текущих команд, второй выход первой схемы сравнения и выход второй схемы сравнения - соответственно с третьим и четвертьм входами блока управления, третий и четвертый выходы блока управления соединены соответственно с вторыми входами элементов И третьей группы и с управляющим входом второго блока коммутации, пятый выход блока управления соединен с вторили входами элементов И четвертой и пятойгрупп, а шестой выход - с вторыми входами элементов И шестой и седьмой групп. Кроме того, блок управления содержит блок постоянной памяти, дешифратор адреса, регистр адреса микрокоманд, модификатор адреса микрокоманд, причем первый, второй, третий, четвертый, пятый и шестой вьЬсоды блока постоянной памяти являются соответственно первым, вторьм, третьим, четвертым, пятым и шестьил выходами блока управления, а седьмой выход блока управления соединен с входом модификатора адреса микрокоманд, второй, третий, четвертый и пятый входы модификатора адреба команд являются соответственно первым, вторым, третьим, и четвертым входами блока управления, выход модификатора адреса соединен с входом регистра адреса микрокоманд, выход которого соединен с входом дешифратора адреса, выход дешифратора адреса соединен с входом блока постоянной памяти. Новая совокупность существенных признаков обеспечивает достижение поставленной цели в силу того, что в памяти устройства фиксируются нижний и верхний адреса каждого непрерывного набора команд с последовательными адресами (границы каждого набора), то есть адреса команд, использованных в программах будут зафиксированы. Таким образом, устройство обеспечивает проверку полноты использования ко маид программы. На фиг. 1 приведена функциональна схема устройствадля контроля хода программ; на фиг. 2 - функциональная схема первого блока коммутации; на фиг. 3 - функциональная схема второго блока коммутации; на фиг. 4 - ,струк урная схема блока управления. ; Устройство состоит из первого бло ка 1. коммутации, счетчика 2 адреса текущих команд, регистра 3 адреса те кущих ксячанд, входного регистра 4 адреса команд, первого регистра 5.1 нижней границы участка программы, пе вого регистра 5.2 верхней границы участка прогргиу|мы, второго регистра 6. 1 нижней границы участка програм мы, второ.го регистра 6.2 верхней гра иицы участка программы, первого и iaTOporo блоков 7 и 8 сравнения, блока 9 коммутации, блока 10 управления блока 11 памяти, первого и второго элементов ИЛИ 12 и 13, первой, второй, третьей, четвертой, пятой, шестой и седьмой групп 14.1, 14.2, 15, 16.1, 16.2, 17.1 элементов И, входов 18 для адресов команд. Блок 1 состоит из входа 19 для си гнала установки в исходное состояние триггера 2О,, групп 21 и 22, элементо И. Блок 9 состоит из групп 23-f, 23, 24,, 242, 25, 25 j элементов И (цеп установки узлов устройства в исходное состояние не показаны). Блок 10 состоит из блока 26 посто янной памяти, дешифратора 27 адреса микрокоманд, регистра 28 адреса микрокоманд, модификатора 29 адреса мик рокоманд, входа 30 начальной установ ки. Блок 10 работает в соответствии с микропрограммой, записанной в блоке 26, а анализ внешних сигналов и ветвление микропрограмм производится мо дификатором 29. Выработка сигналов микрооперации производится в соответствии с микропрограммой работы блока 10, с учетом сигнала с других узлов устройства, передаваемых на входы блока 10, т.е. с учетом сигналов внешних для блока 10 условий. Обработка внешних сигналов условий,как известно,производится модификатором микрюпрограммного устройства управления. Принцип работы устройства заключается в следующем. На вход устройства со счетчика ко маНд подаются адреса.выполняемых ко манд и сигнал сопровождения, который вырабатывается при изменении содержимого счетчика команд. При анализе последовательности адресов выполнент ных команд выделяются на начальный (нижний) и конечный (верхний) адреса набора выполняемых команд с последовательными адресами, эта пара адресов фиксируется, затем определяются границы следующего набора команд с последовательными адресами. После этого границы каждого последующего набора сравниваются с границами предыдущего набора. Сравнение границ производится для экономии памяти. Когда, например,« границы последующего набора команд полностью включают в себя границы предыдущего набора, то нет необходимости записывать в память границы обоих наборов команд, а достаточно записать границы только после-, дующего набора. При сравнении границ Двух наборов могут иметь место еледующие случаи: границы последующего набора шире границ пред ыдушего набора и полностью его перекрывают, в этом случае стираются границы последующего набора; границы последующегонабора шире границ предьщущего набора и полностью его перекрывают, в 1ЭТОМ случае стираются границы п редыдущегр набора; наборы предыдущий и последующий пер екрьтаются лишь частично, т.е. часть команд из одного набора входит в другой, в этом случае производится расширение нижней или верхней границы; границы последующего набора не перекрываются с границами предьщущего, в этом случае грани1да предыдущего) набора фиксируются в памяти, а границы последующего набора в дальнейшем сравниваются с границами следующего за ним набора. Рассмотрим подробно работу устрййства. В исходном состоянии все регистры, счетчик и блок памяти не содержат никакой информации, а блок управления находится в состоянии ожидания сигнала с выхода элемента ИЛИ 12. Триггер 20 блока 1 находится в состоянии О, в которое он устанавливается по входу 19 сигналом установки в исходное состояние. Адрес начальной команды (нижняя граница набора) и с игнал изменения адреса команды поступают на входы группы 21 и с ее выхода адрес команды через группу 22 записывается в счетчик 2 и в регистр 4. После того, как в регистр 4 записан адрес, на входе элемента ИЛИ 13 вырабатывается сигнал,который сигнализирует о не нулевом состоянии регистра и который устанавливает триггер 20 блока 1 в в результате чего состояние группа 22 блокируется, а группа 222 разблокируется.

Это состояние триггера 20 сохраняется до тех пор, пока устройство не будет, установлено в исходное состояние. После этого устройство находится в режиме ожидания изменения адреса выполняемой в ЭВМ команды. Адрес последующей команды, к выполнению котброй приступила ЭВМ по сигналу изменения команды через группы 21 и 222 записывается в регистр 3; В результате этой записи сигнал с выхода элемента 12 увеличивает на единицу содержимое счетчика 2 и поступает на вход блока 10, который в ответ на него подает управляющий сигнал на входы групп 14.1 и 14.2 элементов И, подключая тем самым к входам блока 7 регистр 3-й счетчик 2. Блок 7 производит сравнение их содержимого, т.е. сравнение адреса новой команды с увеличением на единицу с адресом предыдущей команды. В зависимости от результата сравнения реализуются два режима работы этого устройства. Если содержимое регистра 3 равно содержимому счетчика 2 (адреса предыдущей и последующих команд отличаются на единицу, т.е. в ЭВМ выполняются ко-, манды с послед;овательными адресами) , блок 10 (по сигналу с соответствующего выхода блока 7) производит изменение регистра 3, и устройство переходит в режим ожидания, изменения выполняемой в ЭВМ команды, блок 10 ожидает сигнал с элемента 12. При поступлении на регистр 3 адреса новой команды производится, как описано выше, добавление единицы в счетчик 2 и сравнение содержимых регистра 3 и счетчика 2. Если они равны, вновь производится гашение регистра 3 и -переход, к ожиданию изменения команды в ЭВМ. Работа устройства в этом случае соответствует выполнению в ЭВМ непрерывной цепочки команд с последователь нкми адресами. При этом содержимое регистра 4 определяет первую команду (нижний адрес) набора выполненных команд, а на счетчике 2 происходит расширение верхней границы адресов вы;полненных команд. .

В том случае, когда содержимое счетчика. 2 и регистра 3 не равны (т..е. адрес последующей команды отличается от адреса предыдущей команды на число, отличное от единицы, например, при условном или безусловном переходе в программе), работа устройства соответствует переходу в программе от одного набора команд с последовательными адресами к другому, т.е. передача управления в программе. В этом случае-сигналом с соответствующего выхода блока 7 содержимое счетчика 2 уменьшается на единицу (происходит возврат к адресу команды, от которой производится передача управ-ления) и, кроме того, по этому сигналу с выхода блока 10 на группы 16.1 и 16.2 элементов И подается управляющий сигна ;записи содержимого регистра 4 и счетчика 2 в регистры 5.1 и 5;2, а затем управляют.ий снгнйл - на. группу 15 элементов И.

В результате этого в регистрах

5.1и 5.2 записываются границы первого набора команд с последовательньми адресами, а в регистр 4 и счетчик 2 - содержимое регистра 3 - нижняя граница участка программы (нового набора команд).

С целью ЭКОНСЯ4ИИ памяти произво дится дальнейшая обработка полученных данных. С блока 10 в блок 9 подается управляющий сигнал, -по которому к блоку 8 подключаются пары регистров из числа регистров 5.1, 5.2, 6.1 и 6.2. Это проверка совместимости границ предыдущего набора (записанных в регистрах 6.1 и 6.2) с границами последующего (регистры 5.1 и 5.2).

Сначала к блоку 8 через группы х. 2 подключаются рег стрял 5.1 и .6.2 (нижняя граница нового 1набора и верхняя границапредыдущего набора). Если содержимое регистра 5.1 больше содержимого регистра 6.2, Т.е. наборы команд не пересекаются (ни одна команда одного набора ксяланд не вxoдитf в другой набор команд), то сигналом . с блока 10 на группы 17.1 и 17.2 элементов И производится запись содержимого регистров 6.1 и 6.2 в блок 11, а затем содержимое регистров 5.1 и

5.2через группы 23-, и 232 блока 9 переписывается в регистры 6.1 и 6.2. В результате в блоке 11 записаны границы (нижний и верхний) адреса преды дущего набора команд/ в регистрах 6.1 и 6.2 - границы последующего набора.

Если содержимое регистра не (превышает содержимого регистра 6.2, по сигналам с блока 10 к блоку 8 через группы 242 и 25 подключаются регистры 5.2 и 6.1 (верхняя граница нового набора команд и нижняя - предыдущего набора).

Если содержимое регистра 5.2 меньше содержимого регистра 6.1 (т.е. непересекакщиеся наборы команд) устройство работает аналогично описанному.

Если содержимое регистра 5.2 не меньше содержимого регистра 6.1, по сигналам с блока 10 к блоку 8 через группы 24 и 2 5.f подключаются регистры 5.1 и 6.1 .(нижняя граница посдедукидего и предыдущего наборов) .

Если, содержимое регистра 5.1 меньше содержимого регистра 6.1, т.е. последующий набор включает в себя часть адресов команд предьшущего набора, по сигналу с блока 10 через группу 23-J производится перезапись содержимого регистра 5.1 в регистр 6.1 (расширение нижней гранищ2 набора адресов использованных команд).

Если содержимое регистра 5.1 не меньше содержимого регистра 6.1, к блоку 8 по сигналу управления с блока 10 через группы 24 и 25 подключаются регистры 5.2 и 6.2 и производится сравнение верхних границ двух наборов адресов команд. При этом; если содержимое регистра 5.2 больше содержимого регистра 6.2 (верхняя граница последуюо его набора выше верхней границы предыдущегонабора), J3 poизвoдитcя расширение верхней границы набора адресов использованных команд, записанной в регистре 6.2, для чего по сигналу с блока 10 через группу 232 блока 9 содержимое регистра 5.2 пёрепйсьшается в регистр 6.2. Если же содержимое регистра 5.2 не превышает содержимого, регистра 6.2, по управляющему сигнаhy с блока 10 производится гашение регистра 3 и ус,тройство переходит к ожиданию адреса следующей выполняемой в ЭВМ команды. Таких образом, в том случае, когда в ЭВМ происходит переход от одного набора команд с последовательными адресами к другсшу набору команд с последовательными адресами при сравнении границ наборов адресов команд, записанных в регистрах 6.1, 6.2-и 5.1, 5.2, возможны следующие случаи. - Если наборы адресов не пересекаются, границы предыдущего набора (содержимое регистров 6.1 и 6.2) перепис ышаются в ячейку блока 11, а содержимое регист|юв 5.1 и 5.2 переписывается в регистры 6.1 и 6.2.

Если наборы адресов перекрываются частично, происходит расширение нижней (или верхней) границы путем передачи содержимого регистра 5.1 (или 5.2) в регистр 6.Д (или 6.2) .

Если последующий набор адресов входит в предыдущий набор как составная часть, содержимые регистров 6.1 и 6.2 не изменяются.

Если последукхций набор включает в себя как составную часть предыц5тций набор, в регистры 6.1 и 6.2 записываются нового набора адресов (содержимое регист юв 5.1 и 5.2). Таким образом, если на вход 18 устройства подавать со счетчика команд с1дреса выполняемых в ЭВМ команд, после окончания контролируемой программы ЭВМ в блоке 11 зафиксируются адреса команд, выполняемых в ЭВМ, причем для экономии памяти в ее ячейках записываются адреса не каждой вьшол- . ненной команды, а граничные адреса использованных наборов команд с по. следовательными адресами или отдельные кома1шы.

Контроль программ, выполняемых на ЭВМ, с помощью предлагаемого устройства производится.следующим образом.

Устройство подключается к счетгчику команд ЭВМ и устанавливается в исходное состояние. После этого производится поочередное включение всех программ, выполняемых на ЭВМ. По окончании работы программ блока 11 памяти известньм способом выводится на печать. Команды, задействованные в программах, известны, поэтому необходимо сравнить список из0вестных команд со списком, команд, ис- :пользованных в работе ЭВМ. В том слу|чае, когда какая-либо команда, имею.щаяся в списке, задействованных в программах, ни разу lie использовалась при работе ЭВМ, т.е. отсутствует в

s распечатке содержимого блока 11, необходимо или провести проверку этой команды, или в тех случаях, когда это возможно, путем имитации внешних. воздействий на ЭВМ добиться того, что0бы эта команда была выполнена.

Создать.такие внешние условия, например, для управляющей ЭВМ, не удается, необходимо произвести про-, верку этой команды.

5

Таким образом, после проверки всех программ, выполненных на ЭВМ, из списка команд должны быть удалены все команды, адреса которых ни разу не встречались в. работе ЭВМ, и реакция

0 ЭВМ на которые не известна (или нежв-. лательны, или не должны иметь место)

Таким образом, по сравнению с известным устройством, предлагаемое позволяет более полно контролировать

5 правильность прохождения прогргиим, выполняемых на ЭВМ, так как позволя-. .ет зафиксировать каждую выполняемую команду и таким образом выявить все команды, которые, будучи задействова0ны при составлении программы, ни разу не выполнялись при их прохождении.

Формула изобретения

1. Устройство для контроля хода программ, содержащее первый и второй блоки сравнения, первый и второй регистры нижней границы участка программы, первЕай и второй регистры верхней границы участка программы и блок Памяти, отличающее с я тем, что, с целью повышения .точности контроля, в него введены входной регистр адрейа команд, регистр адреса текущих команд. Счетчик адреса текущих команд, первый и второй блоки коммутации, первая, вторая, третья,, четвертая, пятая, шестая и седьмая группы элементов И, первый и второй з лементы ИЛИ и блок управления, причем информационный и первый управляющий входы первого бЛока коммутации являются соответственно адресами и управяющим входами устройства, первый выход первого блока коммутации соединён с информационным входом регистра адреса текущих команд, управляющий вход которого соединен с первым выходом блока управления, второй выход блока управления - с первыми входами элементов И первой и второй гр5шп, выходы которых соединены с, входами первой схемы сравнения, выход регистра адреса текущих команд соединен с . входс 1 |первого элемента ИЛИ, с вторьми входами элементов И первой группы, с первыми входами элементов И третьей группы, выходы которых соединены с первыми информационными входами входного регистра адреса команд и счетчика текущих команд, второй выход первого блока коммутации соединен с вторыми информационными входгми счетчика адреса текущих команд и входного регистра адреса команд, выхр{ц которого соединен с первьми входами элементов И четвертой группы и через второй элемент ИЛИ - с вторым управляющим входом первого блока коммутации, информационный выход счетчика соединен с вторыми входами элементов И второй группы и первыми входами элементов И пятой группы, выходы элементов И четвертой и пятой групп соединены с информацион ными входами первых регистров соответственно нижней и верхней границ участка программы, информационные выходы которых, соединены соответственно с первым и вторым информационнн14и входами блока коммутации, первый, вто

,рой, третий и четвертый информацион ные выходы второго блока коммутации соединены соответственно с первым и вторым входом второго блока сравнения, с входами -вторых регистров нижней и верхней границ участка програм;Йз1, выходы .вторых регистров нижней и верхней границ участка программы соединены с первыми входгиУ1и элементов li, .шес.той и седьмой групп соответственно кррме того,каждый выход регистра ниж ней и верхней границ участка програМ|мы соединен соответственно с третьим к четвертым инфopv aциoнньilми входами второго блока коммутации, выходы iэлементов И шестой и седьмой групп

соединены соответственно с первой и второй группами входов блока памяти первый выход .блока сравнения соединен с управляющим входом вычитания счетчика адреса текущих команд и первьм входом блока управления, выход первого элемента ИЛИ - с вторж входом блока управления и с управляющим вхоДСЯ4 сложения счетчика адреса текущих команд, BJopvOй выход первой схемы сравнения и выход второй схемы сравнения - соответственно с третьим и четвертым входгши блока управления, третий и четвертый выходы блока управления соединены соответственно с вторыми входами элементов -И третьей группы .я с управляющим входом второго блока коммутации, пятый выход блока управления соединен с вторьми входгими элементов И четвертой и пятой групп, а шестой выход - с вторыми входами элементов И.шестой и седьмой групп. 2t Устройство по п. 1, отлича19Щееся тем, что блок управления содержит блок постоянной Пс1МЯти, дешифратор адреса, регистр гшреса микрокоманд, модификатор адреса микрокоманд, причем первый, второй, третий, четвертый, пятый и шестой выходы блока постоянной памяти являются соответственно , вторым, третьим, четвертым, пятьм и шестых выходами блока управления, а седьмой выход блока управления соединен с входом модификатора адреса микроко манд, второй, третий, четвертый и пятый входы модификатора адреса команд являются соответственно первым, вторым, третьим и четвертьм входами блока управления, выход модификатора адреса соединен с входом регистра адреса микрокоманд, выход которого соединен с входсм дешифратора гщреса, выход дешифратора адреса ;оединен с входом блока постоянной пгмяти.

Источники информации, принятые во внимание при экспертизе

1.Патент США 3935563,

кл. 340-172.5, опублик. 1976..

2.Патент США 393161 , кл. 340-172. 5, опублик. 1976.

983.712

i ,r.

r I

bl

I J t

ij

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программ | 1980 |

|

SU1057949A1 |

| Адаптер канал-канал | 1987 |

|

SU1425694A1 |

| Устройство для контроля программ | 1983 |

|

SU1136172A1 |

| Устройство приоритетного доступа к магистрали | 1990 |

|

SU1839249A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для сопряжения ЭВМ с синхронным каналом передачи данных | 1986 |

|

SU1424023A1 |

| Устройство для контроля программ | 1980 |

|

SU879564A1 |

| СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2005 |

|

RU2292075C1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Способ и устройство автоматизированного структурирования мультикультурных учебных групп | 2016 |

|

RU2618387C1 |

1 у к

I r I

t

z

.1

7

1 /7/

K6i

КЗ

кги

0tit.i

OmSt

Kfft

(pvi.S

KfSKJf

K17

Oaf 7

0m n ХЗ

yff

Авторы

Даты

1982-12-23—Публикация

1979-12-21—Подача