щим входом счетчика адреса текущих команд выход первого элемента ИЛИ соединеи с .вторым управляющим входом счетчика адреса текущих команд и с вторым входом блока микропрограммного управления, второй выход первого блока сравнения и первый выход второго блока сравнения соединены соответственно с третьим и четвертым входами блока микропрограммного управления, второй выход второго блока сравнения соединен с вторыми упраЕ1Ляющими входами первых регистров верхней .и нижней границ участка программы и с пятым входом блока микропрограммного управления седьмой выход которого соединен с вторыми упра вляющими входами вторых регистров верхней и нижней границ . участка программы о т л и ч а ю щ е ее я тем, что, с целью расширения функциональных возможностей устройства путем фиксации границ

57949

выполненных участков программ с подсчетом циклов, в устройство введены счетчик циклов, третий элемент ИЛИ и блок элементов ИЛИ, причем выходы вторых регистров верхней и нижней границ участка программы соединены соответственно с первым и вторым входом блока элементов ИЛИ, выход .которого соединен с информационным входом илока памяти, восьмой выход блока микропрограммного управления соединен с управляющим входом счетчика циклов и с первым входом третьего элемента ИЛИ, выход которого соединен с управляющим входом блока памяти, второй выход второго блока сравнения соединен со счетным входом счетчика циклов, выход которого соединен с третьим входом блока элементов ИЛИ, пятый выход блока микропрограммного управления соединен с. вторым входом третьего элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программ | 1979 |

|

SU983712A1 |

| Устройство для контроля программ | 1983 |

|

SU1136172A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство для определения производительности ЭВМ | 1985 |

|

SU1439600A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

УСТРОЙСТБО ДЛЯ КОНТРОЛЯ ХОДА ПРОГРАММ, содержащее блок микропрограммного управления, первый и второй блоки сравнения, первый и второй регистры нижней границы участка программы, первый и второй регистры верхней границы участка протраммы, блок памяти,входной регистр ядреса команд, регистр адреса текудах команд, счетчик адреса текущих команд, блок коммутации, группу эле.ментов И, первый и второй элементы ИЛИ, причем информационный и первый управляющий входы блока коммутации являются соответственно адресным и управляющим входами устройства, первый выход блока коммутации соединен с информационным входом регистра адреса текущих команд, выходы которо го соединены с входами первого элемента ИЛИ, первыг: входом первого блока сравнения и с первыми входами элементов И группы, второй выход блока коммутации соединен с первыми информационными входами счетчика адреса текущих команд и входного регистра адреса команд, выходы которого соединены с входами второго-элемента ИЛИ и информационным входом первого регистра нижней границы участка программы, выходы элементов И группы соединены с вторыми информационными входами входного регистра адреса команд и счетчика адреса текущих команд, выход которого соединен с вторым входом первого блока сравнения и входом первого регистра верхней границы участка программы, выход второго элемента ИЛИ соединен с вторым управляющим входом блока коммутации, первый, второй, третий и четвертый выходы блока микропрограммного управления соединены со. ответственно с управляющим входом i регистра адреса текущих команд, с вторыми входами элементов И группы, О) с управляющим входом первого блока сравнения и с управляючщм входом второго блока сравнения, пятый выход блока микропрограммного управления соединен с первььми управляющими входами первых регистров верхней и нижней границ участка программы, выходы о ел которых соединены соответственно с информационными входами вторых ре гистров верхней и нижней границ со участка программы и соответственно. с первым и вторым информационными входами второго блока сравнения, щесо стой выход блока микропрограммного управления соединен с первыми управляющими входами вторых регистров верхней и нижней границ участка программы, выходы которых соединены с третьим и четвертым информационными входами блока сравнения, первый выход первого блока сравнения соединен с первым входом блока микропрограммного управления и перпым управляю

. . , . 1 Изобретение относится к вычислительной технике и может быть исползовано для организации контроля и отладки программ.

Известно устройство для контроля прохождения программ, содержащее зонную память, которая состоит из трех основных частей: быстродействующего запоминающего блока для хранения адресов, схем селекции и хранения адресов, схем считывания и визуального вывода зафиксированных адресов П

Недостаток устройства заключается в малой достоверности контроля программ.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее блок управления, блоки сравнения, регистры нижней границы участка программы, регистры верхней границы участка программы, блок памяти, входной регистр адреса, команд, регистр адреса текущих команд, счетчик адреса текущих команд, блок коммутации, группу элеГ 1

ментов И, элементы ИЛИ 2.

Однако устройство характеризуется -недостаточными функциональными

возможностями, так как не обеспечивает фиксацию границ выполненных участков Программ с подсчетом циклов.

Цель изобретения -.расширение функциональных возможностей устройства путем фиксации границ выполнения участков программ с подсчетом циклов,

Поставленная цель достигается тем, что в устройство для контроля хода программ, содержащее блок микропрограммного ynpaBJienHH, первый и второй блоки сравнения, первый и второй регистры нижней границы участка программы, первый и второй регистры в,ерхней границы участка программы, блок памяти, входной регистр адреса команд, регистр адреса текущих команд, счетчик адреса текущих команд, блок коммутации, группу элементов И, первый и второй элемент ИЛИ, причем информационный и первый управляющий входы блока коммутации являются соответственно адресным и управляющим входами устройства, первый выход блока коммутации соединен с информационным входом регистpa адреса текущих команд, выходы которого соединены с входами первого

элемента ИЛИ, первым входом первого блока сравнеш1я н с первыми входами элементов И группы, второй выход блока коммутации соединен с первым информациоонными входами счетчика адреса текущих команд и входного регистра адреса команд, выходы которого соединены с входами второго элемента Или и информационным входом первого регистра нижней границы участка лрограммы, выходы элементов И группы соединены с вторыми информационными входами входного регистра адреса команд и счетчика адреса теkyuyix команд, выход которого соеди нен с вторым входом первого блока сравнения и входом первого регистра верхней границы участка программы, выход второго элемента ИЛИ соединен с вторым управляющим входом бп0тка коммутации, первый второй, тий и четвертый выходы блока микропрограммного управления соединены соответственно с управляю1цим входом р егистра адреса текуи х команд, с вторыми входами элементов И группы, с управляющим входом первого блока сравнения и с управляющим входом второго блока сравнения, пятый выход блока микропрограммного управления соединен с первыми управляющими входами первых регистров верхней и нижней границ участка программы, выходы которых соединены соответственно с информационными входами вторых регистров верхней и нижней границ участка программы и соответственно с первым и вторым информационными входами второго блока сравнения, шестой выход блока микропрограммного управления соединен с первыми управляющими входами вторых регистров . верхней и нижней границ участка программы, выходы которых соединены с третьим и четвертым информационными входами блока сравнения, первый выход первого блока сравнения соединён с первым входом блока микропрограммного управления и первым управляющим входом счетчика адреса текущих команд, выход первого элемента 11ПИ соединен с вторым управляюищм входом счетчика адреса текущих команд и с вторым входом блока микропрограммного управления, второй выход первого блока сравнения и первый выход второго блока сравнения соединешз соответственно с третьим и четвертым входами блока микропрограммного уп579494

равления, второй выход второго блока сравнения соединен с вторыми управляющими входами первых регистров ; верхней и нижней границ участкг про-: 5 граммы и с пятым входом блока микponporpahiMHoro управления, седьмой выход которого соединен с вторыми управляющими входами вторых регистров верхней и нижней границ участка

o программы, введены счетчик циклов, третий элемент ИЛИ и блок элементов ИЛИ, причем выхода вторых регистров верхней и нижней границ участка программы соединены со ответственно с

5 первым и вторым входом блока элементов ШШ, выход которого соединен с информационным входом блока памяти, восьмой выход блока микропрограммного управления соеда нен с управляющим

0 входом счетчика циклов и с первым входом третьего элемента ИЛИ, выход которого соединен с управляющим входом блока памяти, второй выход второго блока сравнения соединен со

5 счетным входом счетчика циклов, выход которого соединен с третьим входом блока элементов ИЛИ,- пятый выход блока микропрограммного управления соединен с вторым входом тре0 тьегр элемента ИЛИ.

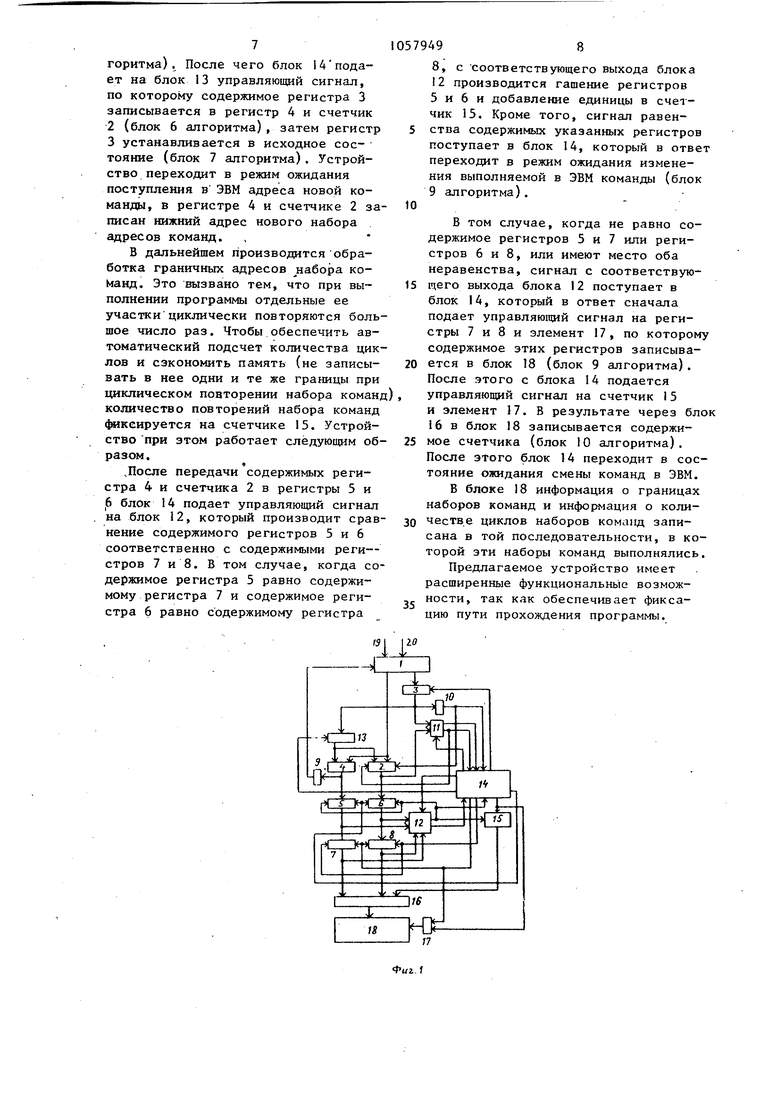

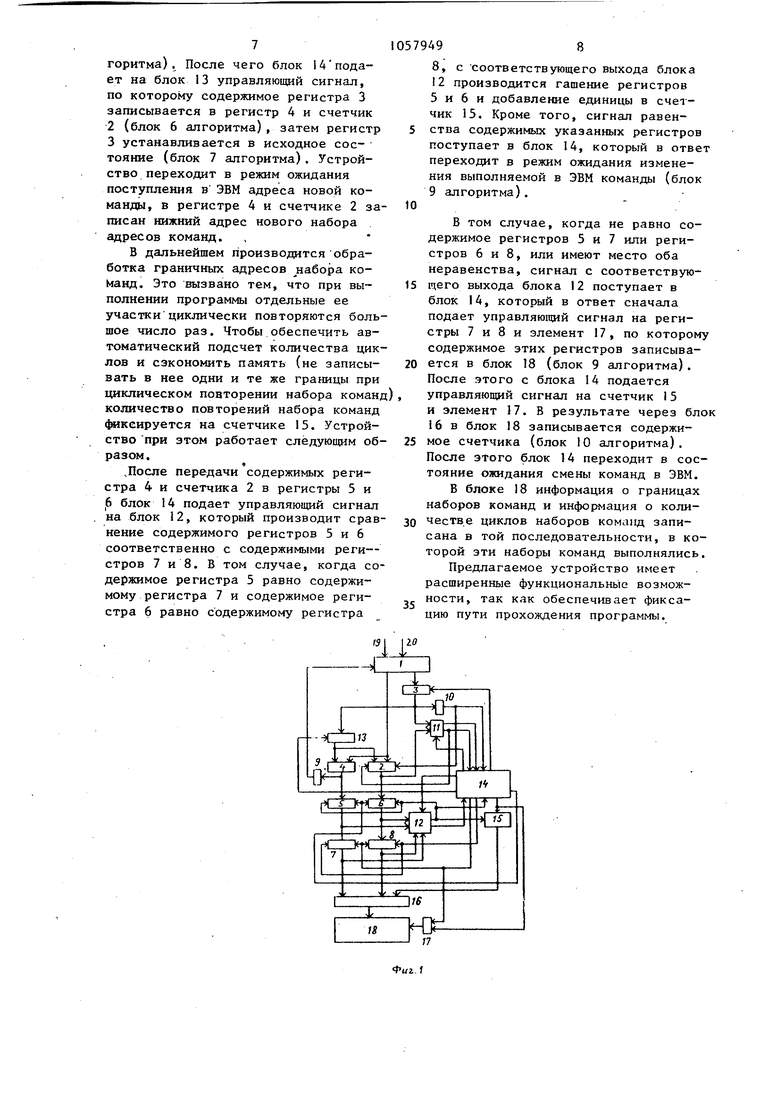

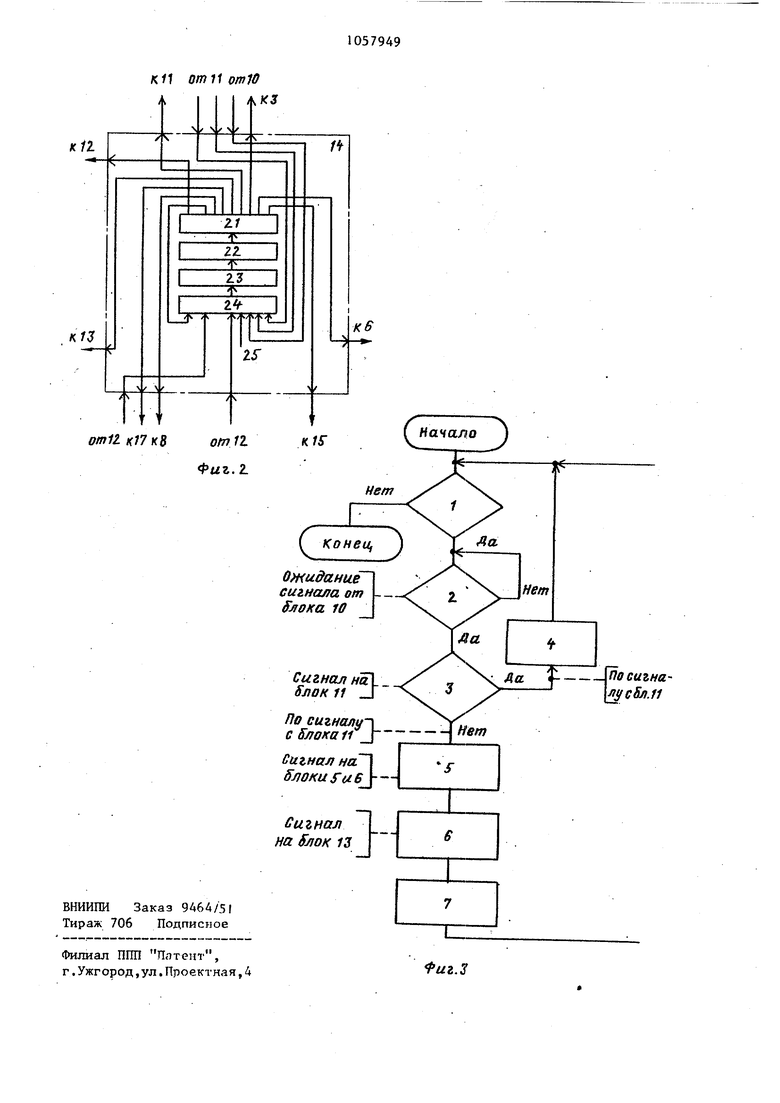

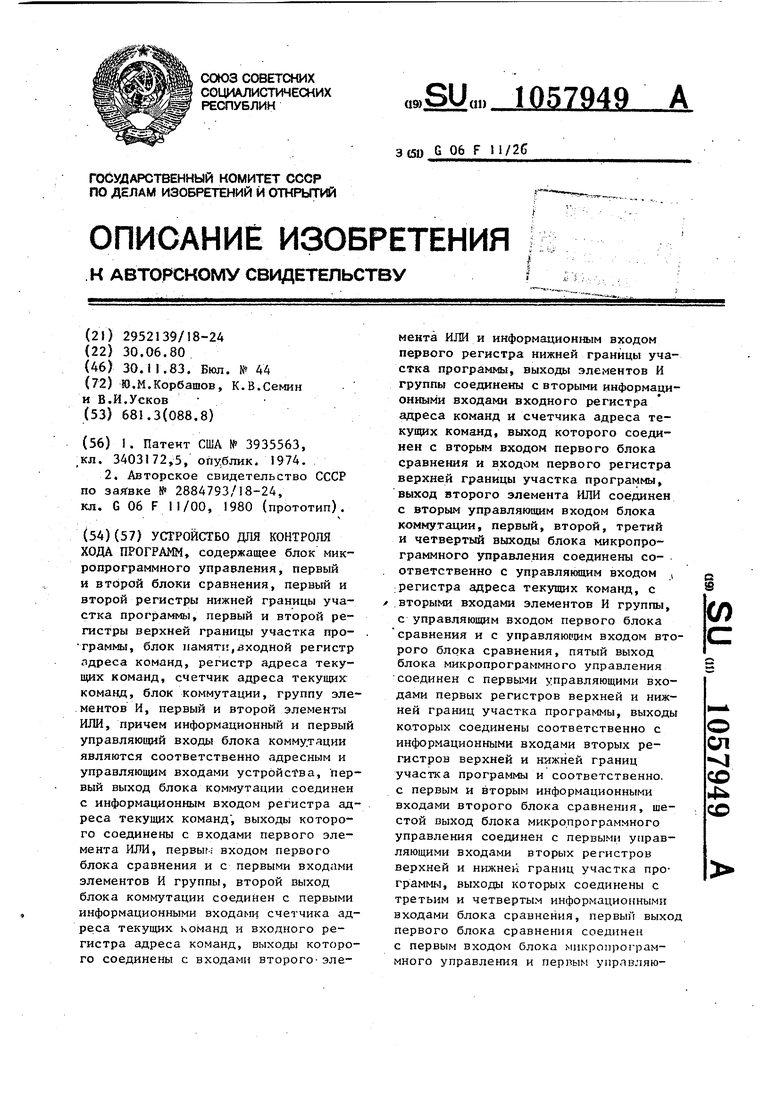

На фиг. представлена функциональная схема устройства для контроля хода программ; на фиг; 2 - вариант построения блока управления; на

5 фиг. 3 - алгоритм работы блока управления.

Устройство состоит из блока I коммутации, счетчика 2 адреса текущих Q команд, регистра 3 адреса текущих команд, выходного регистра 4 адреса команд, первого регистра 5 нижней границы участка программы, первого регистра 6 верхней границы участка . программы, второго регистра 7 нижней границы участка программы, второго регистра 8 верхней границы участка программы, элементов ИЛИ 9 и ТО, первого блока 11 сравнения, второго блока 12 сравнения, группы 13 эле0ментов И блока 14 микропрограммного управления, счетчика 15 циклов, блока 16 элементов ИЛИ, третьего элемента ИЛИ 17, блока 18 памяти, адресного входа 19 и управляющего входа 20.

Блок 14 состоит из блока 21 постоянной памяти, дешифратора 22, регистра 23 адреса микрокоманд, мо5

дификатора 24 адреса, входа 25 начальной установки.

Блок 14 работает в соответствии с микропрограммой, записанной в блоке постоянной памяти. Обработка сигналов от других узлов устройства произвол тся модификатором.

Узлы устройства выполняют, следующие функции.

На счетчике 2 устройство формирует адреса выполняемых в ЭВМ команд, на регистре 3 хранятся адреса текущих команд, поступающих из ЭВМ на вход 19. На вход 20 поступает сигнал изменения адреса команды. В регистре 4 хранится адрес нижней границы выполняемого участка программы, поступающий.или с входа 19 (через блок 1) или с регистра 3 (через блок 13). Регистры 5 и 6, 7 и 8 служат для вре менного хранения содержимых регистра 4 и счетчика 2 соответственно.

Устройство работает следующим образом.

В исходном состоянии (цепи установки узлов и исходное состояние не показаны, как не существенные) все регистры счетчика 2 и блок памяти не содержат никакой информации, в счетчике 15 записан код 00...О. Блок 14 находится в состоянии ожидания сигнала с выхода элемента О (блок алгоритма). Блок 1 подключав ет вход 19 к входам счетчика 2 и регистра 4.

Адрес начальной команды программы по сигналу изменения адреса команды из ЭВМ записывается с входа 19 в счетчик 2 и регистр 4. После записи адреса в регистр 4 сигнал с выхода элемента 9 (появляюигийся при ненулевом состоянии регистра) переключает блок 1, з результате чего последний отключает вход 19 от регистра 4 и счетчика 2 и подключает его к входу регистра 3. Такое состояние блока I сохраняется вплоть до установки устройства в исходное состояние. После записи в регистр 4 и счетчик 2 устройство находится в состоянии ожидания изменения адреса команды на счетчике команд ЭВМ.

Адрес следующейкоманды по сигналу изменения адреса команды через блок 1 записывается в регистр 3 . В результате (при ненулевом состоянии регистра З) сигнал с выхода элемента 10 увеличивает на единицу содержимое счетчика 2 и поступает на

0579496

вход блока 14, который в ответ на этот сигнал подает управляющий сигнал на вход блока 11, который при этом производит сравнение содержи5 мых регистра 3 и счетчика 2, т.е. сравнение адреса новой команды с увеличенн1ам на единицу адресом предыдущей команды (блок 3 алгоритма). В зависимости от результата срав10 нения реапизуются два режима работы устройства. Если содержимое регистра 3 и счетчика 2 равно (адреса предыдущей и последующей команд отличаются на единицу, т.е. в ЭВМ вьг15 полняются команды с последовате гьными адресами), то блок 14 по сигналу с соответствующего выхода блока 1 } производит гашение регистра 3 /блок 4 алгоритма) и устройство переходит 20 в режим о;кидания изменения выполняемой в ЭВМ команды (блок 14 Ожида-ет сигнал с выхода элемента Ю).

При поступлении на регистр 3 новой команд}) производится добавление 25 единицы в счетчик 2 и сравнение содержимого регистра 3 и счетчика 2. Если оно равно, то вновь производится гашение регистра 3 и переход к о ожиданию изменения команды в ЭВМ. 30 Работа устройства в данном случае соответствует выполнению в ЭВМ непрерывного набора команд с последовательными адресами. При этом содержимое регистра 4 определяет первую команду (нижний адрес набора адресов команд) набора выполняемых команд, а на счетчике 2 производится расширение верхней границы набора адресов команд.

В том случае, если содержимое счетчика 2 и регистра 3 не равно (т.е. адрес последующей команды отличается от адреса предыдущей команды на число отличное от единицы) работа устройства соответствует переходу в программе от одного набора команд другому, т.е. от одного линейного участка программы к другому. В этом случае сигнал с соответствующего выхода блока 1I уменьшает содержимое счетчика 2 на единицу (происходит возврат к адресу команды от которой произошла передача управления) и, кроме того, этот сигнал поступает на вход блока 14, который в ответ подает управляющий сигнал на входы регистров 5 и 6, .по которому в эти регистры записывается содержимое регистра 4 и счетчика 2 (блок 6 алгоритма), После чего блок 14подает на блок 13 управляющий сигнал, по которому содержимое регистра 3 записывается в регистр 4 и счетчик 2(блок 6 алгоритма), затем регистр 3устанавливается в исходное состояние (блок 7 алгоритма). Устройство переходит в режим ожидания поступления в ЭВМ адреса новой команды, в регистре 4 и счетчике 2 за писан нижний адрес нового набора адресов команд. В дальнейшем производится обработка граничных адресов набора команд. Это вызвано тем, что при выполнении программы отдельные ее участки циклически повторяются боль шое число раз. Чтобы обеспечить автоматический подсчет количества цик лов и сэкономить память (не записывать в нее одни и те же границы при циклическом повторении набора коман количество повторений набора команд кеируется на счетчике 15. Устройство при этом работает следующим об разом . ,После передачи содержимых регистра 4 и счетчика 2 в регистры 5 и |6 блок 14 подает управляющий сигнал на блок 12, который производит срав нение содержимого регистров 5 и 6 соответственно с содержимыми реги- стров 7 и 8. В том случае, когда со держимое регистра 5 равно содержимому регистра 7 и содержимое регистра 6 равно содержимому регистра 8, с соответствующего выхода блока 12 производится гашение регистров 5 и 6 и добавление единицы в счетчик 15. Кроме того, сигнал равенства содержимых указанных регистров поступает в блок 14, который в ответ переходит в режим ожидания изменения выполняемой в ЭВМ команды (блок 9 алгоритма). В том случае, когда не равно содержимое регистров 5 и 7 или регистров 6 и 8, или имеют место оба неравенства, сигнал с соответствующего выхода блока I2 поступает в блок 14, который в ответ сначала подает управляющий сигнал на регистры 7 и 8 и элемент 17, по которому содержимое этих регистров записывается в блок 18 (блок 9 алгоритма). После этого с блока 14 подается управляющий сигнал на счетчик 15 и элемент 17. В результате через блок 16 в блок 18 записывается содержимое счетчика (блок 10 алгоритма). После этого блок 14 переходит в состояние ожидания смены команд в ЭВМ. В блоке 18 информация о границах наборов команд и информация о количестве циклов наборов команд записана в той последовательности, в которой эти наборы команд выполнялись. Предлагаемое устройство имеет расширенные функциональные возможности, так как обеспечивает фиксацию пути прохождения программы.

К11 omil ofJff

| I | |||

| Патент США № 3935563, кл | |||

| 3403172,5, опублик | |||

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 2884793/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-11-30—Публикация

1980-06-30—Подача