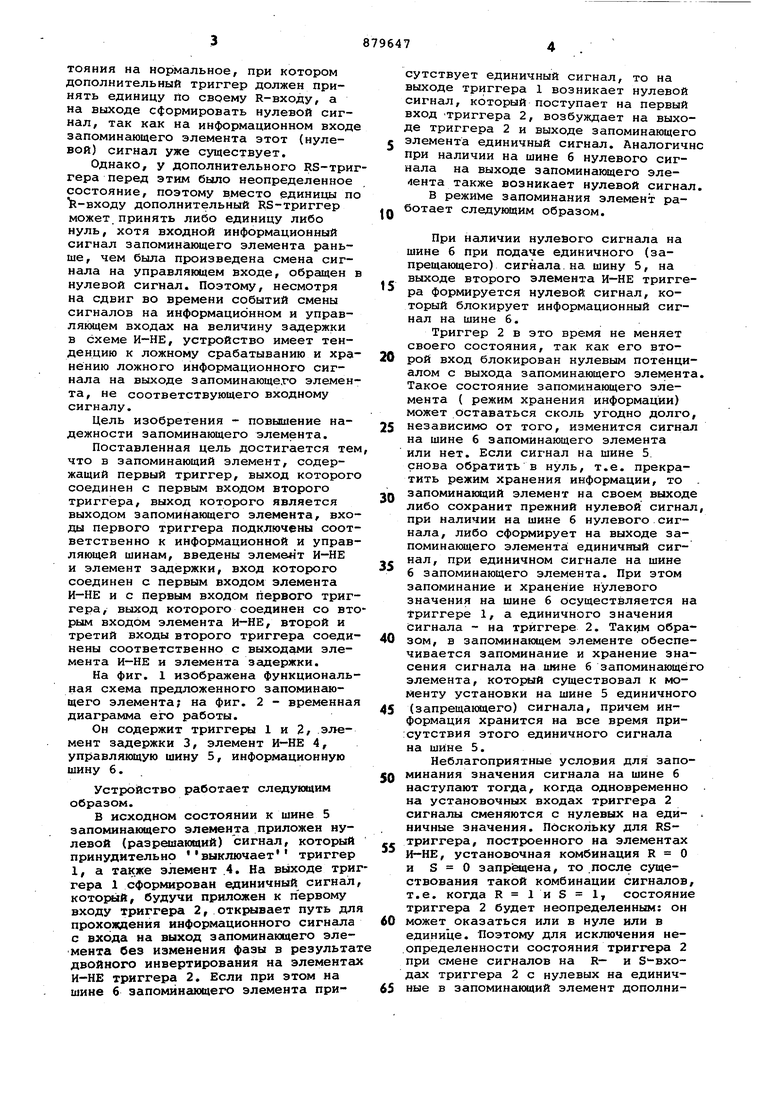

Изобретение относится к област-и автоматики и вычислительной техники и предназначено для применения в цифровых устройствах, в частности в буферных запоминающих устройствах для оперативного запоминания и хране ния мгновенных значений двоичного сигнала. Известен.запоминающий элемент 1 содержащий RS-триггер. Недостатками указанного запоминающего элемента являются невозможность управляемой выборки и хранени дискретной информации и, кроме того неопределенность состояния при опре деленных запрещенных комбинациях сигналов на установочных R и S-входах. TaKj для RS-триггера, построен ного на ячейках И-НЕ, запрещенной комбинацией является R 0 и S - О , а для триггера, построенного на ячейках ИЛИ-НЕ - R 1 и S 1. Наиболее близким из известных по технической сущности явялется запоминающий элемент, содержащий основн RS-триггер, имеющий сигнальный (информационный) и управляющий входы, дополнительный RS-триггер, R-вход которого подключен к Q - выходу основного триггера, подключенного RT входом, к информационному входу запоминающего элемента, причем S-входы обоих RS-триггеров,подключены к управляющему входу запоминающего элемента,выходом которого является ftвход дополнительного RS-триггераUl. .Недостатком этого устройства, выбранного за прототип, яв.пяется наличие ложных срабатываний дополнительного RS-тpиггgpa при определенной последовательности появления сигналов на информационном и управляющем входах запоминающехнэ элемента. Так, в режиме приема информации на управляющем входе существует нулевой запрещающий сигнал.. Пусть на информационнЬм входе запом инающего элемента существует единичный сигнал. В это время на установочных R- и S-входах дополнительного КЗтриггера присутствуют нулевые сигналы. Теперь сигнал на информационном входе сменим на нулевой. Как только на Q - выходе основного RS-триггера появится единичный сигнал, в это время на управляющем входе сформируется также единичный сигнал. Таким образом, на установочных входах дополнительного элемента происходит перехрД сигналов с запрещенного сое тояния на нормальное, при котором дополнительный триггер должен принять единицу по своему R-входу, а на выходе сформировать нулевой сигнал, так как на информационном вход запоминающего элемента этот (нулевой) сигнал уже существует. Однако, у дополнительного RS-три гера перед этим было неопределенное состояние, поэтому вместо единицы п -входу дополнительный RS-триггер может принять либо единицу либо нуль, хотя входной информационный сигнал запоминающего элемента раньше, чем была произведена смена сигнала на управляющем входе, обращен нулевой сигнал. Поэтому, несмотря на сдвиг во времени событий смены сигналов на информационном и управляющем входах на величину задержки в схеме И-НЕ, устройство имеет тенденцию к ложному срабатыванию и хра нению ложного информационного сигнала на выходе запоминающего элемен та, не соответствующего входному сигналу. Цель изобретения - повышение надежности запоминакицего элемента. Поставленная цель достигается те что в запоминающий элемент, содержащий первый триггер, выход которог соединен с первым входом второго триггера, выход которого является выходом запоминающего элемента, вхо ды первого триггера подключены соот ветственно к информационной и управ ляющей шинам, введены элемент И-НЕ и элемент задержки, вход которого соединен с первым входом элемента И-НЕ и с первым входом первого триг гера, выход которого соединен со вт рым входом элемента И-НЕ, второй и третий входы второго триггера соеди нены соответственно с выходами элемента и-НЕ и элемента задержки. На фиг. 1 изображена функциональ ная схема предложенного запоминающего элемента; на фиг. 2 - временна диаграмма его работы. Он содержит триггеры 1 и 2, элемент задержки 3, элемент И-НЕ 4, управляющую шину 5, информационную шину 6. Устройство работает следующим образом. В исходном состоянии к шине 5 запоминающего элемента приложен нулевой (разрешающий) сигнал, который принудительно выключает триггер 1, а также элемент .4. На выходе три гера 1 сформирован единичный сигнал который, будучи приложен к первому входу триггера 2, откривает путь дл прохояздения информационного сигнала с входа на выход запоминающего элемента без изменения фазы в результа двойного инвертирования на элемента и-НЕ триггера 2. Если при этом на шине 6 запоминающего элемента присутствует единичный сигнал, то на выходе триггера 1 возникает нулевой сигнал, который поступает на первый вход -триггера 2, возбуждает на выхое триггера 2 и выходе запоминающего элемента единичный сигнал. Аналогично при наличии на шине 6 нулевого сигнала на выходе запоминающего элелента также возникает нулевой сигнал. В режиме запоминания элемент раотает следующим образом. При наличии нулевого сигнгша на шине 6 при подаче единичного (запрещающего) сигнала на шину 5, на выходе второго элемента и-НЕ триггера формируется нулевой сигнал, который блокирует информационный сигнал на шине 6. Триггер 2 в это время не меняет своего состояния, так как его второй вход блокирован нулевым потенциалом с выхода запоминающего элемента. Такое состояние запоминающего элемента ( режим хранения информации) может оставаться сколь угодно долго, независимо от того, изменится сигнал на шине б запоминающего элемента или нет. Если сигнал на шине 5. снова обратить в нуль, т.е. прекратить режим хранения информации, то . запоминающий элемент на своем выходе либо сохранит прежний нулевой сигнал, при наличии на шине б нулевого сигнала, либо сформирует на выходе запоминакнцего элемента единичный сигнал, при единичном сигнале на шине б запоминающего элемента. При этом запоминание и хранение нулевого значения на шине б осуществляется на Триггере 1, а единичного значения сигнала - на триггере 2. Такум образом, в запоминающем элементе обеспечивается запоминание и хранение знасения сигнала на шине б запоминающего элемента, который существовал к моменту установки на шине 5 единичного (запрещакяцего) сигнала, причем информация хранится на все время при;сутствия этого единичного сигнала на шине 5. Неблагоприятные условия для запоминания значения сигнала на шине б наступают тогда, когда одновременно на установочных входах триггера 2 сигналы сменяются с нулевых на еди- . ничные значения. Поскольку для RSтриггера, построенного на элементах И-НЕ, установочная комбинация R О и запрещена, то после существования такой комбинации сигналов, т.е. когда , состояние триггера 2 будет неопределенным: он может оказаться или в нуле или в единице. Поэтому для исключения неопределенности состояния триггера 2 при смене сигналов на R- и S-BXOдах триггера 2 с нулевых на единичные в запоминающий элемент дополнительно введены элемент И-НЕ и элемент задержки.

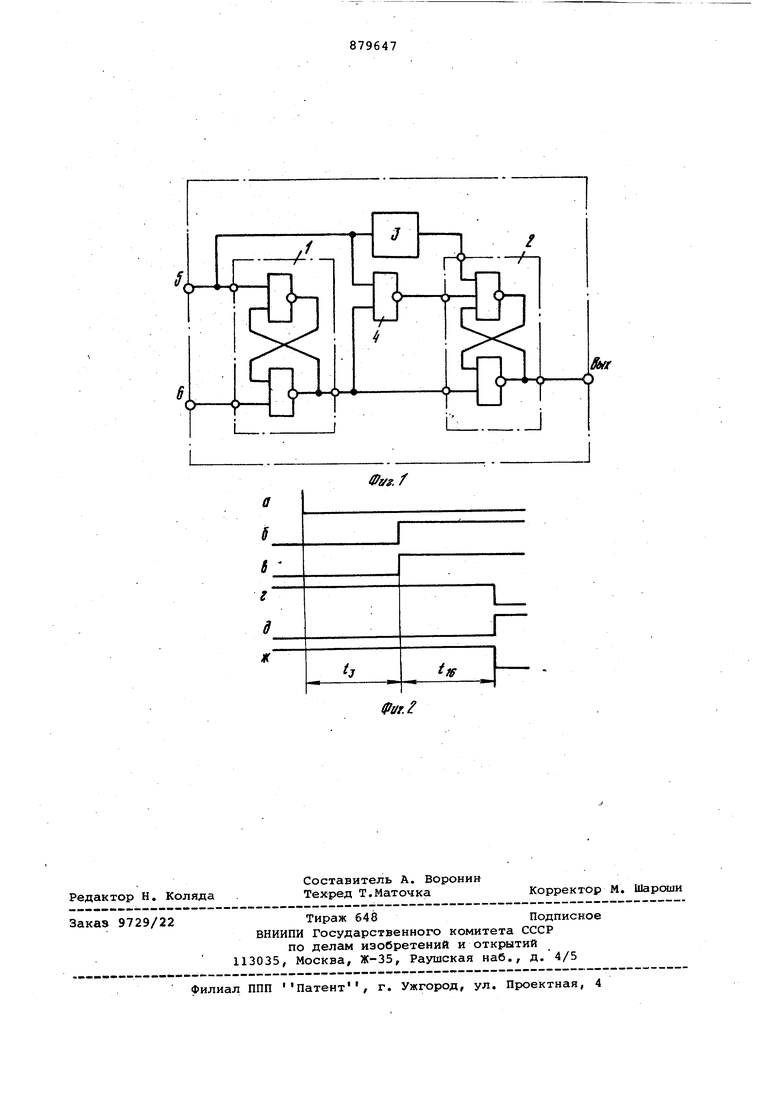

За пояснением устранения ложных срабатываний обратимся к временной диаграмме работы запоминающего эл ментана- фиг. 2.

При смене значения сигнала а на шине б с «Ч на О через время задержки tj на выходе триггера 1 появится единичный сигнал б. Пусть в это же время на шине 5 подан сигна в . Через время t, равное времени задержки в .элементе 4, на его выходе произойдет смена сигнгша г с 1 на О , который блокирует; работу первого элемента И-НЕ триггера 2 нулевым потенциалом на входе триггера 2, а единичный сигнал д на втором входе триггера 2 установится только после того, как сигнгш в пройдет через линию задержки 3 с некоторым запаздыванием на время t07/ t.- Следовательно, единичный сигнаш б на входе триггера 2 устанавливается раньше, чем произойдет смена сигнала д на выходе элемента 3 с нуля на единицу и триггер 2с единичного состояния перейдет в нулевое в соответствии с нулевым сигналом а на шине 6, который уже существует на протяжении времени t j .

Поэтому сигнал б проинвертировавшись на втором элементе триггера 2 и обратившись в нулевой сигнал ж, поступает на выход запоминающего элемента. К этому времени в. триггере 1 происходит запоминание инвертированного значения сигнала а на шине 6, так как вход второго элемента И-НЕ триггера 1 сблокирован выходным нулевым потенциалом с выхода первого элемента триггера 1 и дальнейшее продвижение информации по входу ( по шине 6 ) прекращено.

В результате анализа состояния информации на шине 5 и входе триггера 2 совершается целенаправленная установка триггера 2 в состояние, которое соответствует на момент сигнала а в промежутке времени t. Существенно при этом, что общее время, необходимое для произведения операции запоминающая,в любом случа не превысит удвоенной задержки одного элемента И-НЕ.

Следовательно, введенные в запоминающий элемент И-НЕ и элемент задержки, который, например, может быть выполнен на двух инверторах, не только устраняют ложное срабатывание триггера 2, но и позволяют до минимума сократить время, необходи мое для осуществления опе)ации запоминания .

В случае равенства времени задержки распространения сигналов tg 1 v выборки для запоминания можцо уменьшить до величины, не прешяиаюцей длительности переходного процесса на входах второго триггера.

Таким образом, предложенный элемент обладает повьшенной точностью выборки и хранения двоичной информации с обеспечением высокого быстродействия работы запоминающего элемента. Это позволяет ускорить процессы обработки информации в вычислительных комплексах при высокой точности выборки и хранения случайных периодических, стационарных или одиночных информационных сигналов, представленных в двоичной форме.

Формула изобретения

Запоминающий элемент, содержащий первый триггер, выход которого соединен с первым входом второго триггера, выход которого является выходом запоминающего элемента, входы первого триггера подключены соответственно к инфО1 4ационной и управляющей шинам, отличающий с я тем, что, с целью, повышения надежности запоминающего элемента, в него введены элемент И-НЕ и элемент задержки, вход которого соединен с первь входом элемента И-НЕ и с первым входом первого триггера, выход которого соединен со вторым входом элемента И-НЕ, второй и третий входы второго триггера.соединен соответственно с выходами элемента И-НЕ и элемента задержки.

Источники информации, принятые во внимание при экспертизе

1.Гутииков B.C. Интегральная электроника в измерительных приборги Л., Энергня 1974, с. 42-43.

2.Авторское свидетельство СССР 479225, кл. G 11 С 9/00, 1975, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ТЕЛЕНАВЕДЕНИЯ РАКЕТЫ ПО ЛУЧУ И СИСТЕМА ТЕЛЕНАВЕДЕНИЯ ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2258888C1 |

| Устройство для управления группой шаговых электродвигателей | 1981 |

|

SU1073871A2 |

| Устройство слежения за дорожкой дискового носителя информации | 1987 |

|

SU1614031A1 |

| Устройство для чтения микрофиш с автоматической установкой кадра | 1987 |

|

SU1425588A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Многоканальное приоритетное устройство | 1977 |

|

SU746519A1 |

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1554115A1 |

| Сдвиговый регистр | 1983 |

|

SU1624528A1 |

| Устройство для определения площади хроматографического пика | 1987 |

|

SU1501096A2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

а И

5, г

д ж

Авторы

Даты

1981-11-07—Публикация

1980-03-31—Подача