Изобретение относится к вычислительной технике и может быть использовано в качестве асинхронного буферного запоминающего устройства, работающего по принципу первый вошел - первый вышел (F1FO).

Цель изобретения - повышение надежности функционирования сдвигового регистра при разбросе временных параметров его элементов за счет адаптации длительности циклов передачи информации из предыдущей ячейки памяти в последующую и гашения предыдущей ячейки памяти к временным характеристикам элементов,

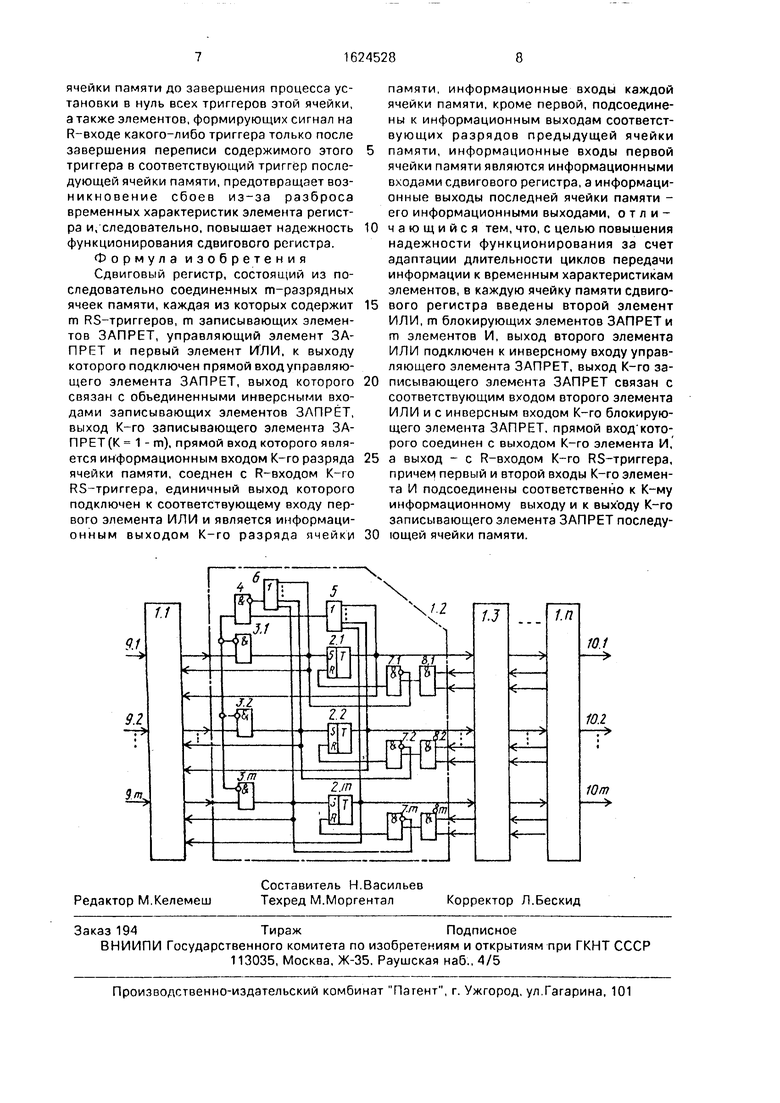

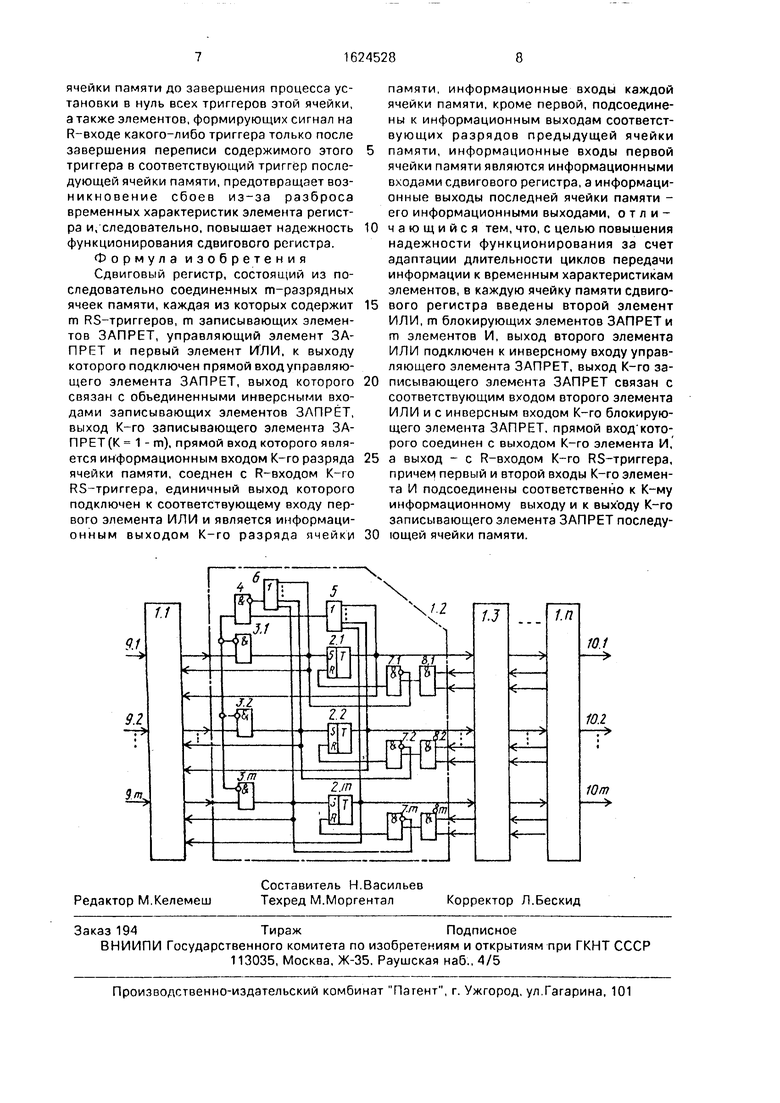

На чертеже схематически представлен предложенный сдвиговый регистр

Регистр состоит из п одинаковых ячеек 1 1 - 1.п памяти, ориентированных на прием и хранение m-разрядных двоичных слов, содержащих единицу хотя бы в одном из разрядов (например, один из разрядов может быть отведен для хранения маркера, указывающего на наличие слова в ячейке памяти). Вторая ячейка 1.2 памяти представлена в виде функциональной схемы.

Каждая из ячеек 1.1 - 1.п памяти содержит m RS-триггеров 2.1 - 2.m, m записывающих элементов ЗАПРЕТ 3.1 - З.пл, управляющий элемент ЗАПРЕТ 4, первый 5 и второй 6 элементы ИЛИ, m блокирующих элементов ЗАПРЕТ 7.1 - 7,т и т элементов И 8.1 - 8.т. Информационные входы первой ячейки 1.1 памяти являются информационными входами 9.1 - 9.т сдвигового регистра, а информационные выходы последней ячейки 1.п памяти являются информационными выходами 10.1 - 10.m сдвигового регистра.

Сдвиговый регистр работает следующим образом.

В исходном состоянии сдвигового регистра во всех ячейках 1.1 - 1.п памяти RS- триггеры 2.1 - 2.т находятся в нулевом состоянии, т. е. в сдвиговом регистре не хранится никакой информации.

На информационные входы 9.1 - 9.т сдвигового регистра поступают сигналы кода слова, содержащего от одной до m единиц. Минимальная длительность импульсов, соответствующих единицам, не должна быть менее максимального суммарного времени срабатывания записывающего элемента ЗАПРЕТ З.К (где К 1 - т) и RS-триггера 2.К.

По истечении времени задержки срабатывания триггеров первой ячейки 1.1 памяти единичные сигналы вводимого кода появляются на прямых входах соответствующих записывающих элементов ЗАПРЕТ 3.1 -З.т ячейки 1.2 памяти. Появление единичных сигналов на выходах записывающих элементов ЗАПРЕТ 3.1 - З.т (или хотя бы на выходе одного из этих элементов) приводит к срабатыванию соответствующих RS-триг- геров 2.1 - 2.ГП и переходу их в единичное состояние, а также к появлению единичного сигнала на выходе второго элемента ИЛИ 6. Поступление единичного сигнала с выхода элемента ИЛИ 6 на инверсный вход управляющего элемента ЗАПРЕТ 4 обеспечивает фиксацию нулевого сигнала на его выходе, в результате чего элементы ЗАПРЕТ 3.1 - З.т остаются открытыми для сигналов, поступающих на их прямой вход. Кроме того, единичные сигналы с выходов соответствующих элементов ЗАПРЕТ 3.1 - З.т, поступая на инверсные входы соответствующих им блокирующих элементов ЗАПРЕТ 7.1 - 7.т, блокируют поступление единичных сигналов на R-входы RS-триггеров 2.1 - 2,гп, предотвращая сброс в нуль тех RS-триггеров 2.1 - 2.т, которые были переведены в единичное состояние.

По истечении времени задержки второй ячейки 1.2 памяти в такой же последовательности срабатывают элементы третьей ячейки 1.3 памяти и т. д., вплоть до элементов последней ячейки 1.п памяти. В итоге код первого поступившего на информационные входы 9.1 - 9.т слова временно запо0 мйнается во всех ячейках 1.1 - 1.п памяти сдвигового регистра.

При наступлении паузы между первым и вторым словом, т. е. после снятия сигналов кода первого слова с информационных вхо5 дов 9.1 - 9.т на всех этих входах устанавливаются нулевые сигналы, что соответствует отсутствию информации на входах регистра. В результате на выходах записывающих элементов ЗАПРЕТ 3.1 - З.т (одного или

0 нескольких) первой ячейки 1.1 памяти единичные сигналы меняются на нулевые, разрешая прохождение сигналов с выходов элементов И 8.1 - 8,т через блокирующие элементы ЗАПРЕТ 7.1 - 7.гл на R-входы RS5 триггеров 2.1 - 2.т. Таким образом, происходит установка в нуль тех RS-триггеров 2.1 - 2.гл первой ячейки 1.1 памяти, б которые были записаны единичные значения разрядов кода первого слова, и первая ячейка 1.1

0 памяти освобождается.

Освобождение первой ячейки 1.1 памяти приводит к исчезновению единичных сигналов на информационных входах второй ячейки 1.2 памяти, а следовательно, на вы5 ходах записывающих элементов ЗАПРЕТ 3.1 - З.т этой ячейки памяти. Единичные сигналы кода первого слова, поступающие на входы некоторых элементов И 8.1 - 8.гл второй ячейки 1.2 памяти с входов и выхо0 дов соответствующих RS-триггеров 2.1 - 2.т третьей ячейки 1.3 памяти, вызывают появление на выходах этих элементов И единичных сигналов. Эти сигналы через открытые нулевым сигналом на инверсном

5 входе соответствующие блокирующие элементы ЗАПРЕТ 7.1 - 7.т поступают на R- входы находящихся в единичном состоянии RS-триггеров 2.1 - 2.т второй ячейки 1.2 памяти и переводят эти триггеры в нулевое

0 состояние, освобождая вторую ячейку 1.2 памяти.

Аналогичным образом освобождаются третья 1,3 и последующие ячейки памяти, включая ячейку 1,(п - 1) памяти.

5 В ячейке 1.п памяти код первого слова сохраняется, поскольку на входах ее элементов И 8.1 - 8.т отсутствуют сигналы, обеспечивающие формирование сигналов сброса RS-триггеров 2.1 - 2.т этой ячейки через блокирующие элементы ЗАПРЕТ 7,1 7.m. открытые нулевыми сигналами с выходов записывающих элементов ЗАПРЕТ 3.1 - З.т ячейки 1,п памяти.

Сохранение кода первого слова в ячейке 1.п памяти приводит к запиранию по инверсным входам ее записывающих элементов ЗАПРЕТ 3.1 - З.т единичным сигналом, поступающим с выхода первого элемента ИЛИ 5 через управляющий элемент ЗАПРЕТ 4, открытый по инверсному входу нулевым сигналом с выхода второго элемента ИЛИ 6 с момента установления нулевого сигнала на выходах всех записывающих элементов ЗАПРЕТ 3.1 - З.т этой ячейки в результате освобождения предыдущей ячейки 1.(п - 1) памяти.

Поэтому при поступлении на информационные входы 9.1 - 9.т сдвигового регистра кода второго слова рассмотренным образом работают ячейки 1.1 - 1.(п - 1) памяти, в результате этот код поступает в ячейку 1.(п - 1) памяти.

При наступлении паузы после второго слова описанным образом освобождаются ячейки 1.1 - 1.(п - 2) памяти, а код второго слова сохраняется в ячейке 1.(п - 1) памяти благодаря тому.что все элементы И 8. 1 - 8.т этой ячейки закрыты по одному из входов нулевыми сигналами, поступающими с выходов заблокированных элементов ЗАПРЕТ 3.1 - З.т ячейки 1.п памяти.

При поступлении на информационные входы 9.1 - 9.т третьего и последующих слов их коды запоминаются соответственно в ячейках 1.(п - 2) и предыдущих ячейках памяти. Код последнего п-го слова будет записан в ячейку 1.1 памяти.

Для взаимодействия сдвигового регистра с источником поступающей на него информации и с приемником информации, хранящейся в сдвиговом регистре, могут использоваться выходы первых элементов ИЛИ 5 ячеек 1.1 и 1.п памяти и входы элементов И 8.1 - 8.т последней ячейки 1.п памяти.

Единичный сигнал на выходе элемента ИЛИ 5 первой ячейки 1.1 памяти указывает на занятость этой ячейки, а сохранение этого сигнала после снятия кода очередного слова с информационных входов 9.1 - 9.т сдвигового регистра указывает на то, что все ячейки 1.1 - 1.п памяти заняты, и в случае поступления на входы сдвигового регистра кода следующего слова этот код не будет принят в регистр.

Нулевой сигнал на выходе элемента ИЛИ 5 последней ячейки 1.п памяти в случае, когда его длительность превышает интервал времени, требуемый для записи входного слова в эту ячейку памяти, сигнализирует об отсутствии информации в сдвиговом регистре.

Соотаетственно единичный сигнал на выходе этого элемента ИЛИ 5 указывает на 5 наличие в ячейке 1.п памяти информации, которая должна быть воспринята приемником. Последующее изменение содержимого ячейки 1.п памяти можно осуществить путем гашения хранящегося в ней кода слова, 10 для чего необходимо подать единичный сигнал на оба входа всех элементов И 8.1 - 8.т этой ячейки. Этот сигнал подтвердит нулевое состояние тех RS-триггеров 2.1 - 2.т, в которых были запомнены нулевые значения

15 разрядов слова, и переведет в нулевое состояние RS-триггеры, хранившие единичные значения разрядов слова, уже воспринятого приемником.

Освобождение ячейки 1.п памяти при0 ведет к разблокированию ее записывающих элементов ЗАПРЕТ 3.1 - З.т, в результате чего в ячейку 1.п памяти будет занесено содержимое ячейки 1.(п - 1) памяти, а по завершении процесса запоминания содер5 жимого ячейки 1.(п - 1) памяти в ячейке 1.п памяти будут сформированы сигналы освобождения ячейки 1.(п - 1) памяти. В свою очередь, освобождение этой ячейки памяти вызовет перепись в нее информации из

0 предыдущей ячейки памяти и освобождение предыдущей ячейки после переписи ее содержимого в последующую ячейку памяти. Этот процесс будет продолжаться до тех пор, пока содержимое каждой из занятых

5 ячеек памяти не будет переписано в последующую ячейку, т. е. пока весь массив хранящейся в сдвиговом регистре информации не будет сдвинут на один шаг (на одну ячейку памяти) в сторону последней ячейки 1.п

0 памяти, информационные выходы которой (т. е. выходы ее RS-триггеров 2.1 - 2.т) являются информационными выходами 10.1 - 10.m сдвигового регистра.

Из сказанного следует, что для осво5 бождения сдвигового регистра, т. е. для обнуления всех его ячеек памяти даже в случае полной занятости регистра, достаточно сформировать на входах элементов И 8.1 - 8.т последней ячейки 1.п памяти последо0 вательность из п единичных сигналов.

Для одновременного обнуления всех ячеек 1.1 - 1.п памяти сдвигового регистра в них могут быть использованы RS-триггеры с двумя R-входами, причем взаимосвязан5 ные вторые R-входы всех RS-триггеров образуют в этом случае цепь сброса (установки в нуль) сдвигового регистра.

Использование в сдвиговом регистре элементов, препятствующих записи информации в отдельные разрядные триггеры

ячейки памяти до завершения процесса установки в нуль всех триггеров этой ячейки, а также элементов, формирующих сигнал на R-входе какого-либо триггера только после завершения переписи содержимого этого триггера в соответствующий триггер последующей ячейки памяти, предотвращает воз- никновение сбоев из-за разброса временных характеристик элемента регистра и, следовательно, повышает надежность функционирования сдвигового регистра. Формула изобретения Сдвиговый регистр, состоящий из последовательно соединенных т-разрядных ячеек памяти, каждая из которых содержит m RS-триггеров, m записывающих элементов ЗАПРЕТ, управляющий элемент ЗАПРЕТ и первый элемент ИЛИ. к выходу которого подключен прямой вход управляющего элемента ЗАПРЕТ, выход которого связан с объединенными инверсными входами записывающих элементов ЗАПРЁТ, выход К-го записывающего элемента ЗАПРЕТ (К 1 - т), прямой вход которого является информационным входом К-го разряда ячейки памяти, соеднен с R-входом К-го RS-триггера, единичный выход которого подключен к соответствующему входу первого элемента ИЛИ и является информационным выходом К-го разряда ячейки

памяти, информационные входы каждой ячейки памяти, кроме первой, подсоединены к информационным выходам соответствующих разрядов предыдущей ячейки памяти, информационные входы первой ячейки памяти являются информационными входами сдвигового регистра, а информационные выходы последней ячейки памяти - его информационными выходами, отличающийся тем, что, с целью повышения надежности функционирования за счет адаптации длительности циклов передачи информации к временным характеристикам элементов, в каждую ячейку памяти сдвигового регистра введены второй элемент ИЛИ, m блокирующих элементов ЗАПРЕТ и m элементов И, выход второго элемента ИЛИ подключен к инверсному входу управляющего элемента ЗАПРЕТ, выход К-го записывающего элемента ЗАПРЕТ связан с соответствующим входом второго элемента ИЛИ и с инверсным входом К-го блокирующего элемента ЗАПРЕТ, прямой вход кото- рого соединен с выходом К-го элемента И, а выход - с R-входом К-го RS-триггера, причем первый и второй входы К-го элемента И подсоединены соответственно к К-му информационному выходу и к выходу К-го записывающего элемента ЗАПРЕТ последующей ячейки памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль многоканального коммутатора | 1986 |

|

SU1368971A1 |

| Устройство приоритетного доступа к магистрали | 1990 |

|

SU1839249A1 |

| Адресное устройство для цифрового фильтра | 1985 |

|

SU1298859A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Устройство для программного управления | 1985 |

|

SU1267362A2 |

| Счетное устройство | 1986 |

|

SU1368981A1 |

| Устройство неординарной разовой коммутации | 1986 |

|

SU1370766A1 |

| Буферное запоминающее устройство | 1977 |

|

SU763965A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве асинхронного буферного запоминающего устройства. Цель изобретения - повышение надежности функционирования за счет адаптации длительности циклов передачи информации к временным характеристикам элементов. Сдвиговый регистр состоит из п последовательно соединенных m-разрядных ячеек памяти, каждая из которых содержит m RS-триггеров, m записывающих элементов ЗАПРЕТ, управляющий элемент ЗАПРЕТ, первый и второй элементы ИЛИ, m блокирующих элементов ЗАПРЕТ и m элементов И. Информационными входами сдвигового регистра являются прямые входы записывающих элементов ЗАПРЕТ первой ячейки памяти, а информационными выходами - единичные выходы RS-триггеров последней n-й ячейки памяти. Организация управляющих цепочек с использованием как первого и второго элементов ИЛИ и управляющего элемента ЗАПРЕТ, так и блокирующих элементов ЗАПРЕТ и элементов И препятствует записи информации в какой-либо из RS-триггеров ячейки памяти до завершения обнуления всех ее RS-триггеров и позволяет сформировать сигнал на R-пходе RS-триггера в случае отсутствия единичного сигнала на его S- входе и только после переписи содержимого данного разряда в соответствующий разряд последующей ячейки памяти, что предотвращает возникновение сбоев при работе сдвигового pei истра из-за разброса временных характеристик элементов и, следовательно, повышает надежность функционирования сдвигового регистра. 1 ил. + Ё ( ю N ел ю 00

| Регистр сдвига | 1982 |

|

SU1111207A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| СПОСОБ ПРИГОТОВЛЕНИЯ ПРЕПАРАТА ЖИДКОГО ЗОЛОТА | 1922 |

|

SU1002A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Регистр сдвига | 1978 |

|

SU809383A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-01-30—Публикация

1983-06-01—Подача