(54) УСТЮЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КАНАЛА СВЯЗИ С МИНИМАЛЬНЫМ УЮБНЕМ ПОМЕХ

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для определения оптимальных рабочих частот | 1980 |

|

SU926779A2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Устройство для вычисления нормированных статистических моментов случайных процессов | 1986 |

|

SU1385131A2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| Спектроанализатор | 1979 |

|

SU866494A1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

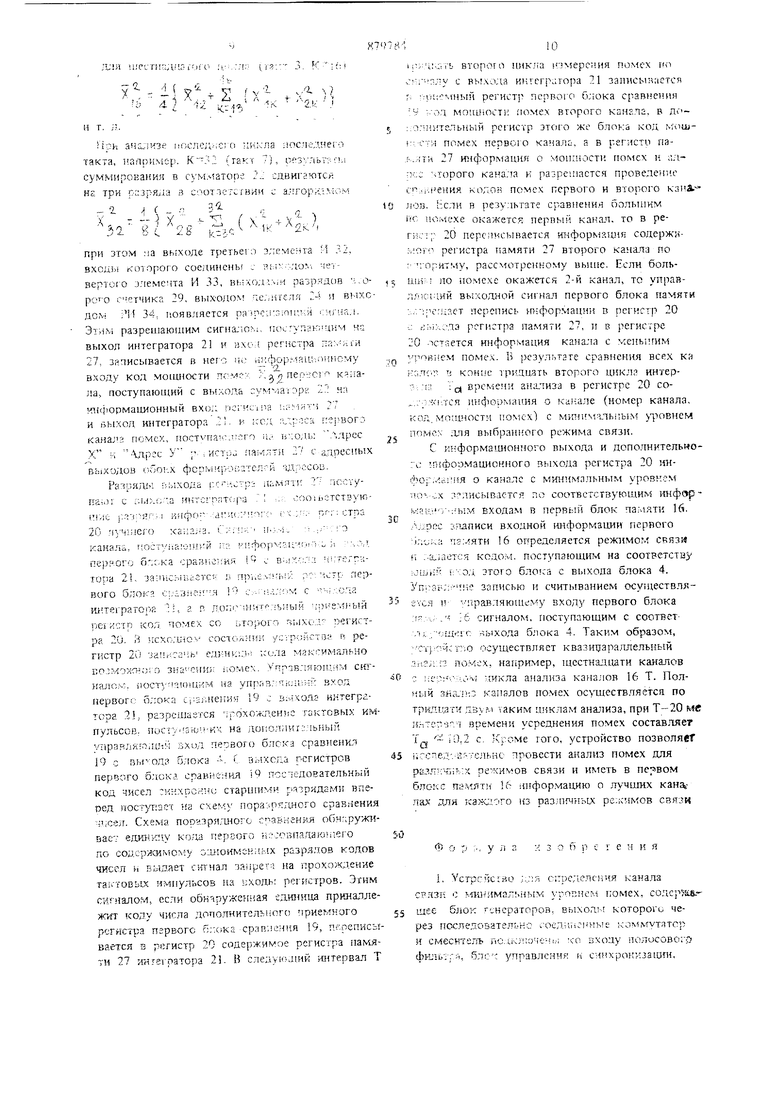

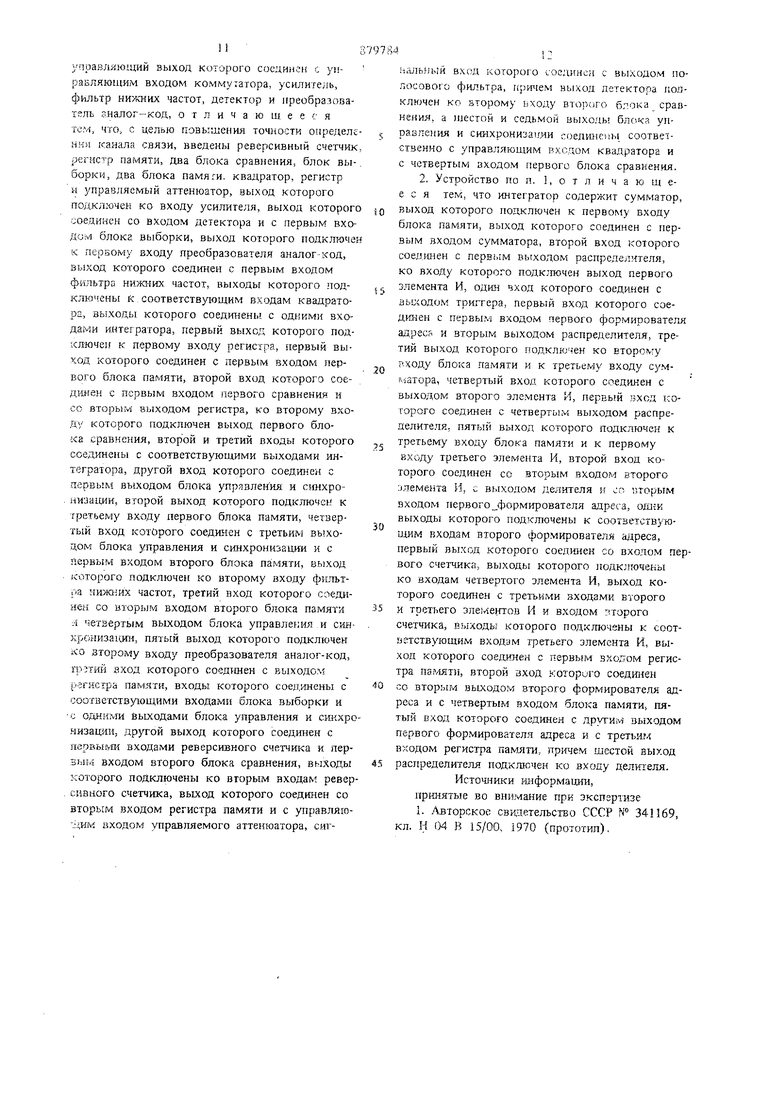

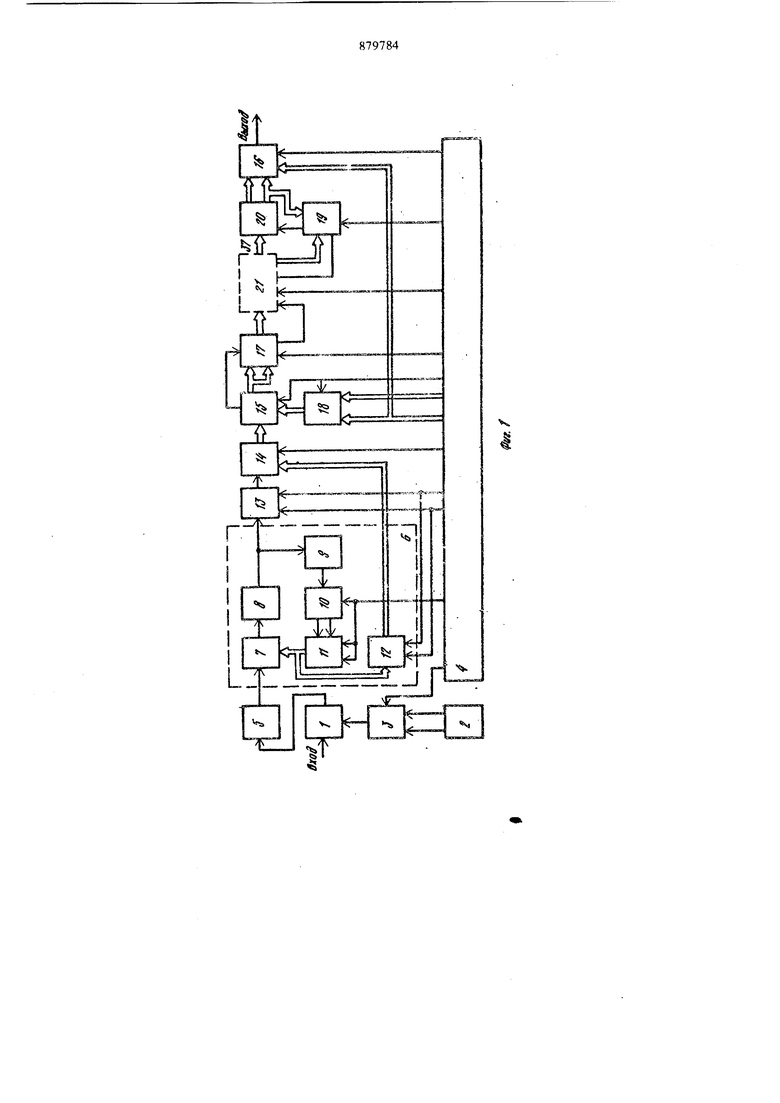

Изобретение относится к радиотехнике и может использоваться в системах радиосвязи, в частности в адаптивных системах связи KB и УКВ диапазонов. Известно устройство для определения канал связи с минимальным уровнем помех, содержа щее блок генераторов, выходы которых через последовательно соединенные коммутатор и смеситель подключены ко входу полосового фильтра, блок управления и синхронизации, управляющий выход которого соединен с управляющим входом коммутатора, усилитель, фильтр нижних частот, детектор и преобразователь аналог-код 1. Однако известное устройство имеет низкую точность определения канала связи. Цель изобретения - повышение точности определения канала связи. Для этого в устройство для определения канала связи с минимальным уровнем помех, содержащее блок генераторов, выходы которого через последовательно соединенные коммута тор и смеситель подключеньг ко входу полосового фильтра, блок управления и синхронизащ1 управляющий выход которого соединен с управляющим входом коммутатора, усилитель, фильтр, нижних частот , детектор и преобразователь аналог-код, введены реверсивный счетчик, регистр памяти, два блока сравнения, блок выборки, два блока памяти, квадратор, регистр и управляемый аттенюатор, выход которого подключен ко входу усилителя, выход которого соединен со входом детектора и с первым входом блока выборки, выход которого подключен к первому входу преобразователя аналогкод, выход которого соединен с первым «входом фильтра нижних частот, выходы которого подключены к соответствующим входам квадратора, выходы которого соединены с одними входами интегратора, первый выход которого подключен к первому входу регистра, первый выход которого соединен с первым входом первого блока памяти, второй вход которого соединен с первым входом первого блока сравнения и со вторым выходом регистра, ко второму входу которого подключен выход первого блока сравнения, второй и третий входы которого соединены с соответствующими выходами интегратора, друго -: пхпд которого соединен с первым пыходом блока управлеHrt н сн}1хроиизации, второй выход которого подк; ючс | к третьему входу первого б.чока памяти, ;ствер11 Й вход KOTopoio соединен с TpcTbiiv н,ыход,ом блока управления и сиихроHi-fJaiuiH и с пе1)вым входом второго Одока iiaNUiTH, и.,ч которого долтсдючеп ко BiojiOMy вход.у ;Ь11дьтра ни;к1П х. часгот, третий вход которого СОеД. СО ПТОГЛ.ТМ входом второго блока чет ертым выходом блока уцрч.влепип 11 )од : а1;ии, пятый выход которсмо лодк.иомеп ко второму ихо;лу преобразоватед аиа.юг-ко,,, третий вход которого coe/uiiien с выход, регистра памяти, входы которого соед.япепы с соответствуклиими входаМ) пд01ча iidioojiioi с одними выход;1мд бло;ча у :п;: 5депия и синхролизацни, дру1ой выход, jciiioporfj соел. с первьгми вxoдa д pcBepciiHiuiro п iiciiBhiM входом яторого cjiaijiicHjH, ВЫХОД которого подктпочены ко :-;тор;. ()Л.ам periepcHoiioro счетлшса, В1-1ХС-Д которого сосд, со вторым входом рсгистХ иа-.чги и е управлякллим входом управдяемо) аттенюатора, сигнальный вход, KOTciporo соед| иеи с выходом цодосового (biubTpa. :ipi;4c,; sibixoii, дс1е1ч 11р:: iio,,Uvjno4eii ко )j Opo.iV :1ход; второю олока cpaBiiein i, ijiecioii ii содьмий выхо:;ы 6;к)ка управления п елнхрс))п;;;;п,1:;1 coej,:;;ieii)i соответственно с уираид/дслциь; вxoдo к в;;; ЦД гора и с четвертым входом о;:;):-:а еравЕгения, iljJirjeM, интегратор содержит c viMarop. выхол :со;ОРОго подключе к nejiiiOMy B ;:i;i,; едока памичч, Д)ХОД которо-iO СОе:Д;1ц- С ЛСрВЛМ ;)ХОЛ,Ол1 CVMNiaTOpa, НТОрой 15Х.ОЛ ;o4i:o;o сое,;и1нен с (M Bi.ixojlOM распре;;елл ел;;.. ко вхол,у которого ,ключсд выход, ис, :дел;сн1г и, од,л1 Bxoji, jcofOjioro соедЛД : с Л;1хол,ох тдштеги;, лерв1)1Й вход, которого С .д. ;,iOi е 1ер1Д,:м входом первого фор мд:-(,:ваа;л: ;;;,:,jieca н B-;-o;ii,iM выходом расгредс лнгедя, nicTHii выхо;;, ,0о нодкдюче} ко еторогду ьходу блока дам/гтп и к третьему входу су;-)Матора, летвеотьн 1.ход Koropoio соел,инеи с выходом liroporo эдемедта И, первы вход Koropoio соединен с четве)тгым выходом рас1тредед1 тед«, ii rrb;i; которого поцюпочеп к третьеглу входу блока naivjn;: и ic первому вход.у третьей) :)демен-га И, второй вход ко торого coejiHiieH со зторь,1,м 5ходом второго эле мента И, с Л)1хо,чом д,е)пгге; Я и со вторым вхо дом siepBoro (Ьормпрователя адреса, одни . хоторого подключеды к соогветствующим входам второ о формирователя адреса, первьн вы ход которого соед.ипен со входом первого счет чдка, которого 1;одкл10че11ы ко входам чет.цсрто10 элемента И,, выход KOToi oro сое.цние с (М1 входами второго , третьего элементов 1 м ВХОД1.0М BTOpoio счетчика, выходы кот рого подклкгтеиы к соответствующим входам ретьего леме1 та И, выход которого соединен пе)вым входом регистра памяти, второй вход KOTijporo соединен со вторь м выходом второго 4 1рмироватедя адреса и с четвертым входо.м блока памяти, пягмн вход которого ое/шнен с другим выходом первого формировае.ля адреса и с третьим входом регистра памяи, причем дестой выход раепредедителя подключен ко входу делителя. На фга. 1 представлена структурная электрическая схема предложенного устройства; на на фиг. 2 вариант выполнения интегратора. Устройство для определения канала связи с мпнимадьнглм уровнем помех содержит смеси-те.чь , б.юк 2 генераторов, коммутатор 3, блок 4 управления и синхронизагдаи, подосовой фильтр 5, блок б дискрет1- ого автоматического регулирования усиления (БДАРУ), в состав которого входят удравдяющий аттенюатор ,7, ycHJHiTeJib 8, детектор 9, второй бдок сравнения 10, реверсивнв1Й счетчик PC 11 и регистр памяти 12, блок 13 выборк, преобразователь 14 ададот-код, фидьтр 15 нижних частот, первый блок намяти 16, квадратор 17, второй блок памяти 18, первый бдок сравнения 19, регистр 20, интегратор 21, в состав которого входят сумматор 22, блок 23 памяти, делитель 24, пе|Л)ый и формирователи адреса 25 и 26 соответственно, регистр памяти 27, первый и второй счетчики 28 и 29, первый, второй, третий и четверть элементы И 30-33, расдре/делитель 34 и триггер 35. Устройство работает следующигЛ образом. По о-ггпаду Mcxo/ j oe устройстзо устанавднвается в исходное состояние. Сигнал шестна.цдати помех в полосе промежуточной частот 1 радиоприемного устройства поступает на и формацион11Ь Й вход смесителя 1, на управляющий вход которого на время такта Т, подается самая высокая частота с блока генератораов 2 через коммутатор 3. Длите1П Ность такта Т, постулаго дего на управляющий вход коммутатора 3, задается с соответствующего выхода блока 4. По.чосовым фильтром 5 выделяются первые гармоники продуктов преобразова;вш первого домох входного сигнала. Сигнал помех первого канала длите.ш носгою Т nocTyiiacT с выхода полосового фильтра 5 на вход БДАРУ 6, где, пройдя через последоватедьно включенные управляемый аттенюатор 7, усилитель 8, детектор 9, поступает на вход второго блока сравнения 10. В нем напряжение и„,, огибаклдей детектированного сигнала помех сравнивается с двумя пороговыми напряжениями и, и и, ггричем и. 211,,. Если I ,, . I значение напряжения Ugy превышает пороговое напряжение U., то по такту управляющего сигнала, ностунающего на уиравляющий вход 5 этого блока сравнения и оба входа PC 1 с другого выхода блока 4, на первом управляющем выходе появляется разрешающий сигнал управления и в PC 11 по входу запясыр.ается единица. PC 11 своими выходами управляет управляемым аттенюаторол{ 7, который уменьшает свой коэффигхиент передачи в два раза. Если в следующий такт управляющего сигнала UQ будет больще напряжения LL, то процесс регулирования повторяется, а если UQ., U , то на втором управляющем второго блока сравнения 10 появляется разрешающий сигнал управления, по которому разрешается прохождение тактового импульса по второму входу PC 11 и его содержимое уменьщается на единицу. Управляющий аттенюатор 7 увеличивает свой коэффициент передачи в два раза. Если в результате сравнения выполняется условие Uj Ug.pUj, то на обоих управляющих выходах второго блока сравнения 0 присутствуют запрещающие сигналы и содержимое PC 11 не изменяется. Значение двоичного кода PC И, соответствующее текущему значению коэффициента передачи управляемого аттенюатора в момент взятия выборок из сигнала пом записывается в регистр памяти 12 импульсами управления, поступаю дими с частотой дискрети зации f на управляющие входы регистра памя ти и дополнительные входы блока 13 выборки с соответствующих выходов блока 4. Нормиро ванный относительно порогового напряжения и. и сжатый в 2 - раз (где 0,1,2,3) сигнал помех первого канала с выхода усилите ля 8 БДАРУ 6 поступает на вход блока 13. Входной узкополосый сигнал помех может быт записан в виде X Ct)-Rg )(а)ехр f 4, --)( (-t) Q-i - X2(i) где f - центральная частота узкополосного входного сигнала блока 13; X W--Xa)COe0(t), ) --Х (-b)(-b) X(t)X(t)cose(t), ) X(t) sin6(t)- - квадратурные составляющие комплексной огибающей сигналаX(t) В блоке 13 входной узкополосный сигнал помех в результате дискретизации с частотой f 1/Тд импульсными последовательностями, поступающими с соответствующих выходов блока 4 и сдвинутые относительно друг друга на величину дТГ-г 1/4 f при выполнении условия nf« f(, переносится на нулевута частоту и представляется в виде выборок ( Х(Г.) комплексной огибающей X(t) сигнала помех. Выборки Х(Тд), U) квадратур комплексной огибающей сигнала поочередн 6 преобразуются в двоичный код преобразователем 4 аналог-код с линейной шкалой квантования., такт работы которого задается с выхода блока 4. В преобразователе аналог-код 14 код выборок каждой квадратуры в вь ходном регистре сдвигается влево на количество разрядов, определяемое кодом коэффициента передачи управляющего аттенюатора 7 и пост)Т1ах)ЩИМ на дополнительный информационный вход преобразователя аналог-код 14, с выхода разрядов регистра памяти 12. С выхода преобразователя аналог-код 14 параллельный код квадратур ), Х2(ГГд) комплексной огибающей сигнала помех в полосе Д1 полосового филыра 5поступает на информационный вход фильтра 15 нижних частот, имеющего несколько полос 6F / f измерения помех, задаваемых в зависимости от обеспечения требуемого режима связи коэффициентами, поступающими на разряды управляющего входа с выхода второго блока памяти 18. связи (адрес коэффициентов) задается кодом, пост пающим на вход, второго блока памяти 18 с выхода блока 4. Коэффициенты фильтра 15 для выбршшого режима поступают из второго блока памяти 18 на фильтр 15 последовательно по такту кода сигнала адреса. Фильтр 15 последовательно во врегчгени отдельно фштьтрует квадрат}фы Х(Тд), X2(ZT,.) и вьщает араллелъным кодом на оба информационных входа квадратора 17, по одной, последней на га1тервале Т измерения nof-iex, выборке квадратур установ1шшегося выходного процесса фяпьтра. Эти выборки квадратур записываются в приемные регистры квадратора 17, представляющего из себя перег1шожителъ, сигналом с управляющего выхода фильтра 15 и последовательно на шгтерваль Т воэводлтся в квадрат Х, X.с определенным тактом, поступающим на дополнительный вход с выхода блока 4. Параллельный код квадратов после.дних выборок квадратур Х, Х комплексной огибающей помех первого канала в полосе U F поступает с информационного выхода квадратора 17 на (шформационный вход интегратора 21. С управляющего выхода квадратора 17, соед1шенного с соответсгвующим входом интегратора 21, поступает управляющю сигнал записи Б 1.{нтегратор 21 кода квадратур информационного входа. Интегратор 2 работает следующим образом. По переднему фронту сигнала H iierpaTopa 21 триггер 35 по соответствующему входу устанавливается в eдиничIioe состояние и своим выходом разрешает прохождение через первый элемент И 30 на вход распредел5гге;1я 34 импульсов (РИ) тактовых им 1ульсов, поступаюпртх t определенного блока 4. РИ 34 выделяет восемь raKTOBbLX кмп льсов в::ода. Импульс

с а1) iil посту ::;-; на ьхол cy/.-i -iaropH 22 и нхол )ка 23 и зпписынает

первой квалратугп) ,ч ; вхолмого ni;q;oi:iMa:iHr/;:Hori; сшнала, и к;; второй ;рисмнь Й регистр гсоц ьу/,ей, nocyyiijfCiUHx на долол)гелы1ЫЙ и|фор 1;ационньш нхол суммат;)рз 22 с вьчодэ блока 23 и sainscaintLix в исходном ссктолпин ПС адресу ХУ первого б::()ка лЗ. Сумматор 22 складывает содержимое приEMHhix регистров и результат сложслия -заг гЫваст гя регистр резу;гьтатз сипшлом- nocryfis(iirriajjOM с iibiXj/ia РИ 34,

cyMMSTOpa 22 записывается в плок 2л по алрссу, соотьстстзутщему первому изг;:пяем( сана.1у ломсх, Сигналом с РИ 34 триг гер 35 iiC соотеетствуюя ему xotiy сбрзсь-паегсй в ноль ллиллиает прохойсдение тактовых И ;пульсов. Си}5ХрСя-П О с liOCeMbJM ИМ уЛ |СО;1 ЛСЛ

т;ль 24 устанавл- вается а елюлчное cocioaiuie. По 1 рихоле 310г:ого г№Л ульса ла другой вхол nHiCpaioria iu-iKJi работы, рассьютреннь ; вьпле. гю1 торяется. В cy fГvтaтope 22 теперь уже склалываютс;; кваярать Fiepfsoit квалратуры Х., 3a iсанной fi опок 23 гю адресу первого капала, ;; второй лсвадратуры Х , поступающей Ьа Л(Ьор;«а 1 к)иный Бхол сумма ора 22 с iiiicbopмаичоьного .Ла ква;;.ратора 7, лерв;;го i-ca;:-;.

PP-I

1: . ,t, ,i fi.ijvji ф-:оь.11 V ,, V .;лро,:: У

У Г.ч;кл 23 для rpHCMj млф1;рмацчи

ПЯТОЙ) :чЗ)::,Л; ОН О IM ill:- Kiii: ,К-; :io. мве1 алu nou- . л ;vv;,vx ;и алглч;:; сГм1ась1нае1СЯ л ло;,;, .:,:,:.:: Зч--рл., ;у.ГССй Pi, а nTop-iJ q;v 4M;-.-::. :л; алрс;-, 2-устинзнллвает . У г;,.;):-,-;) 2 ;-:1ал(-н. Устройство ..ля 1Л;л ;:ления ч:ср(ло iUiKia 1Г МС1МЛ5Ч5 кании п .

, лrrл; fГ i i.-A.:;peiiM)i к :-И iiliiUi/Iols Бтогюго )а i h. i н ip-rfx 11НКЛС1Н а;1а:к) асг;-,;ч-|1-1:: о..у iniiiic ,tnrr,p;:vrviv обрйоогки чс;;Н(;. , /iK ; ii Г1ЛИ;асгся от lioiiBoro ;nii:;ia 1--лл. -i,; в

COClO/shUl ;j flJ( 2.i :;; ,i.,;,::;v r ЛЛКЛОГО -CaИаЛ; 7П ЗаП-- :l , .ЛМлЛ;; ПреДЫЛу1Л5;

,;OB ,,;1М.:л;;. ,; ;л1,)-елсл;1; К л-ого цикл;- 1Г;;.;ерГ|(ич помех па П:-;хо л; четкертого : ;ev5 ;:s И 3- :;.,;:;;лс :с;; rir-jjicniaнп 1ИЙ 1 иг:::1л, кс-огмй ,;-i :.,,м li;; ,:rMi; лол второго 3 И .И. ;; иа л,.;:-;, вход ore :;остуи; ет гззре1;|аиллий :-: . :;, ле; М:е;;я 24. и р:;.я.л Л -етсл ::ро;ч;жлелие на ;шклс из уТ ;-с:;И)-

И -;ПуЛЬСОН, СДВИГД- ЛОС VliivOllliiX с 1ХОЛ;. РИ 34

на нход с /лмгтора 32. x4;Ti.;i;:,;c с/и на два разряд. пьзулый; су.;мир()п; :;;ч ,1; КаЖЛ(5-8ОГО KaiiaJia.

.)елите; ь 24 синхронно с восьмь М кмпульсам пторого цикла переходит в улезое состол ие, 3 первьш формировчтель 25 адреса X ус-анавлизается в единичное состояние н СПОИР,; выходом изменяет ;1лрес блока 23, лод/отавлипая память к анализу второго канала помех, код адреса X поступает на ход рс;кстро 27, Устройство готоьо к измерению второго Kaiia.na . С выхода блока 4 поступает упргБ,|я-1О1Цнй сигнал на управляю Ц55Й вход, ггоммугатора 3, которьгй подключает к унравляюиз.ему входу смесителя 1 след ;о;цую более ;;vi3KvT j частоту блока генераторов 2. 1-1а выходе nj.nocoBOio фидьтра 5 вьщедяется пом.ех второго канала, который проходит весь рассмоп) тракт обработки л резуль т«т сложения в сумматоре 22 квадратов второго канатга 1гомех записывается в блок 23 ПС йторого какала помех. Формировате.ць a/J, 25 своим выходол; Адрес X уста1авл тает адрес блока 23 д:ш приема гагформацки третьего канала. Таким же образом измерк;:отсл и все другие каналы помех. По ококча.ьгки ана.лиза, , четвертого канала iioMf.x rfepBs.iH формирователь адреса 25 сбрасып;-етс п (ЮЛЬ синхронно с аосьмым гм-7 л

f eJibMhi ; :.;:(уЛЬС(.:;1 и, ,..Л,.; Ill 4 ;..,зулътят} I с.:5сл, л.тп ка,-;. кг);.;;--;;; -.lari 1сятся

:;Э COOnjeiv. iLiyV;:;;.;, а,Д.,ССа. Ьл:). ;; .;3, СО;лерла1мое Олокг 23 но г(кьм;: iiiKjiaiv. и мериткл является ;;слодной информацией 1;рк ajajnne дгвяroio ; оследу;(п(;1 о HJMcpcuHi.. Но восьмого шиЛ; ;Л;з.Изг )й счетчик 2Н сбрасьшаетси ь нг1Ль, i: п;к, алаллза ганалои iioyex пор гопяется анал,, ич)0 рассмотренным эьпле ijjiKnaM «ССо, а ггсрньж яторого счетчика 29 премеки анализа устаиакл вагтся н единично: сос-;ия ;ис, пидслгплвая количество

TaKlOEi по К; ЛИ1ГЛ и ,()М Ч i - ,

;.- 8).

AuajiiS кана. О вр;чя втог/ою, третьего и , д. тактов .оги-еп анализу каналов первого тактг и OT.iK4aeCi; тем. ..п а};ализ велетея

го амкла звписьтак;тсй згл-и-нш; экспоиенциального . вычисле:;;.,; по , горятму удя двепаццато-о iufK:y гакт 2, К 21 X - 1 7 i Т -i .AN) ;-; 2 t2. -4iiM и т. л.- . H;h ачсшизе последнего ;и-(;.;ла : оследнего такта, . (гакт ), оезхльт гы суммирова1Ш в сум аторг .:.: сдвигакися на три р;:зрЯма з соотзсгсгвии с алгорид.КМ 9 / С л ii,.. при этом ма третьего элемс;1та М З, входы которого соединены j ВЬРГ.ЧО-,-, четвертого злемемта И 33, «(лхол.,- разрядс)з ..0рсг-о счетчика 29, выходо чс.миеля 4 и ДОЛ- :М 34. появляется ра рС11Я;п1и -й :нгнал. Этим разрешающим сигиа-ю.;, (юсупук-.чиги на выход интегратора 2 и лхс-л регистра па:,-И1И 27, записывается в иего пс nHcJiopr.aLi nHfiCMy входу код мощности г с:мел пер:;сг кчиаj.a, поступающий с сумма; эрк ... нп миформанионный BXIJ;: пггн;:1ПЗ и:-мнт1 и интегратора 1. и код адроеа кана;12 помех, ггост%-па оj:ero :;, кчол.ь: .лдрсс X У р , истра naivi TH с адресных Вгяходов ойокх фсрмкроватслй чдрссовРазряды г;ыхода рС--отр; льмлтг nccvyпа о; с :л,|;.;;да интсгрлтора , ; . oooii.crCTByvoii-ic |:аз;- ;г; икфО;- агис: - ;- ( пг-;-; стра 20 xauaja. и.з-г- ,:.-:; канала, г осту|;а 0 и-й iu риформ ц-гп- :. h -..% перрого б ,:,ка сравногня .: чктегрнтора 21, 3a;iViCbiUi;eTC п , р -icrp первого блока С:;13) С..:;|Л;;;А с -i ;:ОДа ш-тйгратО а 15, а п догл- лиитрльныи чриел1ЫЙ pesHCin код vioMex со ьторого м,1ход пегкстра 20, И нсходиеч- COCTO/.HTSH усуройстпу в регистр 20 за г;сачь ед}НК;Л кода максимально DO.;Mo;Kaio; п зна сии;; комсх. Упрзвгшюгдим скгналом. 110С1Лпаю цим на упрлз::ткд1;1-;й вход первог;; блока 1) -: в хода иитегргтора 2, разрсдиется /рохождение тактовых км пульсов, посгу-аюп.к на до1;од;ии::ль 1ЫЙ управ;лягг), вход депвого блока срав} еикя 19 с вы-од блока -, С Вд-дхсца регистров riepBc/ro б;к;кд сравнедил 9 последовательньгй код чисел :кн,хпсн1и; старшими разрядами впеоед )гаст)д-:ае-с на схему поразрядного сравнения iiiceir. Схема поразрягшого С-а&ненйя оОнгфужн Бает еди}ие1у кода первого н;:-;овпадаюи его по содерлшмому однонменаьх разрядов кодов чисел и .-итнал запрет на прохождение тал.-товых имнульсов на 5;ходь; регистров. Этим сигналом, если обкчружен:чая гдштица принадле KvfT коду числа дополнителй -:ого приемного регистра первого f;::oKa срав: ег ия 19, пкрепись вается в регистр 20 содержимое регистра памя ти 27 интегратора 2. В следую.дий интервал Т 1р:-ч;-: гь второго цикла 1з% ерс;1ия помех riii с и ;гсгратора 21 записывается Г: li.iCMHbift регистр первого блока cpaBiieiHtH у ;-од мо цност1-: гюмех второго канала, в до:,ол1 ителы1Ый регистр этого же код r.niuj : си помех первого канала, а в регистч пзГ...-11И 27 И){4;орл1ац1ш о мощности помех и. второго канала к разрешается проведение сп,,:-.иения кодов помех первого и второго капа.-ЛОБ. 1::сди в результате сравнения большим iiC uoivsexe окажется первый канал, то в рег;ь;:;: 20 переписывается ннформяи)я содерж i.ioro регистра памяти 27 второго канала по ; торнтму, рассмотренному выше. Если больiiiiv iio iiONiexe окажется 2-й канзд, то управji.ViCLiHH выходной сигнал первого блока памяти .,/.:p c:i;aeT перепись т-формацин в регистр 20 .; г;:,1:,-дэ рсгр.стра па,мяти 27, л в регистре 20 1стяется информация канала с меньигим уговкем помех. В результате сравнения всех ка 1:ал(.; ч KOHtjc тридцать второго цикла интерТ; л; Уд времени аншиза в регистре 20 со,.;:-:-.тс я И1 фоимания о ка-;але (номер канала, код, мощности помех) с мш и гiльi;ь -t уровнем помех для вь бранного режима связи. С ;г-:формаиионного выхода и допо.чнительно: : гчсЬор.машюниого выхода регистра 20 инфор,.. о Канаде с минимальным уровнг% ПО-. ...х .нсывастся по соответствующим ннфор Лiк r nГ л входпм В перв1: й блок памяти 1й, /:.:.;рес зплписи входной тформагшн первого .: г;з:/яти 16 оггредепяется режимом связи п :-а,;ается кодо.. поступающим на соответству :ошик S; :ол. этого с выхода блока 4. Упраг;; ;- записью и считыванием осуществллsvcM 1 г1 равдяюикму входу первого блока . г Д- ;б сигналом, поступающим с соответлл.:Щг:гс пыхода блока 4. Таким образом, ;CYj-OH;т ю осуществляет квазицара.гшельпый :;г;гг1 г помех, например, шестнадцати каналов с lic-pii-u.si дикда анализа каналов 16 Т. Полный . каналов помех осч шесгвляется по традизти двум таким диклам анализа, при Т-20 ме и.те-тз л времени усреднения помех составляет Т iO,2 с, Сроме ГОТО, устройство позволяет .i-. й-тедькс провести анализ помех для рвз.,п-.:х режимов связи и и%теть в первом блоке .яти 16 .мацию о лучших кан% лах для ка)сТ1Го ю разл1гчнььх ое кимов свяли : 3 о п р 1, VcTpcHCirio ;:;:я с;тредепс;1ня канала сряз; о ьж 1имальным уропнсм помех, со.. шее блок („нераторов. которого через последовательно оед;111г|)мые KON NfvTaTcp и CMCCKTejTb по.1.гч; ;оче- л хо входу полосового фильГГА, блсч удравлення н сннхрон защга.

управляющий выход которого соединен с уцгэаЕЛЯюишм входом коммутатора, усилитель, фильтр ни/ккнх частот, детектор и преобразователь аналог-код, отличающееся тем, что, с целью повылення тощсости ог1ределсния каиала связи, введены реверсивный счетчик регистр памяти, два блока сравнения, блок выборки, два блока памяти, квадратор, регистр 4i управляемый аттенюатор, выход которого подключен ко входу усилителя, выход которого соединен со входом детектора и с первым вхоДО1У1 блока выборки, выход которого подключен к первому входу преобразователя аналоГКОД, выход которого соединен с первым входом фильтра нижних, частот, выходы которого подключены к соответствующим входам квадратора, которого соединень с одними входами интегратора, первьш выход которого подключе к первому входу регистра, первый выход которого соед1шен с первым входом первого блока памяти, второй вход которого соедмген с первь М входом первого сравнения и со BTOpbKvi выходом регистра, ко второму входу которого подключен выход первого блока сравнения, второй и третий входы которого соелдинены с соответствующими вь ходами интегратора, другой вход которого соедшен с первь М вььчодом блока упрявления и синхро. HWJiiiniii, второй выход которого подключен к третьему входу первого блока памяти, четвертый вход которого соедияен с третьим выходом блока управления и синхронизации и с первым входом второго блока памяти, выход которого подключен ко второму входу фильтра нияоаих частот, третий вход которого соединен со вторым входом второго блока памяти л четвертым выходом блока управления и с.инхронизагдаи, выход которого подключен ко второму входу преобразователя аналог-код, грзтйй вход которого соед1шен с выxoдo | егястра памяти, входы которого соединены с соответствующими входами блока выборки и с одними выходами блока управления и синхронизации, другой выход которого соединен с первыгуШ входами реверсивного счетчика и перзын входом второго блока сравнения, выходы которого подключены ко вторым входам ревер, снвного счетчика, выход которого соединен со вторым входом регистра памяти и с унравляю:;дим входом управляемого аттенюатора, сигь.шь.чьш вход которого соединен с выходом полосового фильтра, lipMieM выход детектора по.аключен ко второму входу вторсяо блока сравнения, а шестой и седьмой блока управления и синхронизаили соединег Ы соответственно с управляющим входом квадратора и с четвертым входом первого блока сравнения. 2. Устройство по п. , о т л и ч а ю щ ее с я тем, что интегратор содержит сумматор,

выход которого подключен к первому входу блока памяти, выход которого соединен с первым входом сумматора, второй вход которого соединен с первым вьгходом распределителя, ко входу которого подк.почен выход первого

элемента И, один вход которого соединен с выходом триггера, первый вход которого соединен с первым входом первого формирователя адрес и вторым выходом распределителя, третий выход которого подключен ко второму

входу блока памяти и к третьему входу сумматора, четвертый вход которого соединен с вьгходом второго элемента И, первый вход которого соединен с четвертькм выходом распределителя, пятглй выход которого подключен к

третьему входу блока памяти и к первому входу третьего элемента И, второй вход которого соединен со вторым входом второго элемента И, с выходом делителя и со пторым входом первого формирователя адреса, о.ш-:и выходы которого подключены к соответствующим входам второго формирователя адреса, первый которого соединен со входом первого счетчика, выходы которого 1юдключены ко входам четвертого элемента И, выход которого соединен с третьими входами второго

и третьего элементов И и входом второго

счетчика, выходы которого подключены к соотвгтствующим входам третьего элемента И, выход которого соединен с первь м входом регистра nai.4STij, второй вход :оторого соедт{ен

со вторым выходом второго формирователя адреса и с четвертым входом блока памяти, пятый вход которого соединен с другим вьгходом первого фор.мирователя адреса и с третьим входом регистра памяти, прстем шестой выход

распределителя подключен ко входу делителя.

Источники илформащга, принятые во внимание при экспертизе 1. Мторское сви,аетельство СССР N 341169, кл. Н 04 В 15/00, 1910 (прототип),

Авторы

Даты

1981-11-07—Публикация

1980-01-11—Подача