(54) ЦИФЮВОЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой дискриминатор | 1983 |

|

SU1128248A1 |

| Цифровой дискриминатор | 1981 |

|

SU1003069A1 |

| Цифровой дискриминатор | 1981 |

|

SU1023320A1 |

| Цифровой дискриминатор | 1983 |

|

SU1128247A1 |

| Цифровой дискриминатор | 1985 |

|

SU1312564A1 |

| Цифровой дискриминатор | 1981 |

|

SU951292A1 |

| Цифровой дискриминатор | 1985 |

|

SU1288687A1 |

| Цифровой дискриминатор | 1983 |

|

SU1170447A1 |

| Цифровой дискриминатор | 1983 |

|

SU1151951A1 |

| ЦИФРОВОЙ ДИСКРИМИНАТОР | 1993 |

|

RU2072552C1 |

Изобретение относится к вычислительной и информационно-измерительной технике. Известен цифровой дискриминатор, содержащий счетчик исследуемой величины, ключи ввода уровня дискриминации и счетчика, с помощью которого задается этот уровень (1 . В этом дискриминаторе эа один цикл преоб разованкя мгновенного значения исследуемой величины фиксируется равенство или превышение только одного заданного уровня дискриминации, что является его недостатком. Наиболее близким к изобретению является многоканальный цифровой дискримииатор, содержащий блок счетчиков исследуемой величины, переключатели и блоки сравнения по числу уровней дискриминации, триггеры и блок совпадения 2. Этот дискриминатор может дискриминироват исследуемую величину по ряду уровней (которые образуют сетку уровней дискриминации), но построен путем составления из одноканальных цифровых дискриминаторов. Такое решение требует использования большого объема оборудования, что является его недостатком. В системе обработки данных существует необходимость в дискриминации низкочастотных сигналов по ряду уровней дискриминации, при этом за цикл преобразования таких сигналов необходимо фиксировать мгновенное значение исследуемого сигнала, достигшего наибольшего уровня дискриминащш за этот цикл. Когда на уровне низкочастотного сигнала есть высокочастотная помеха, амплитуда которой находится в пределах уровня дискриминации, происходит многократное срабатывание известного дискриминатора на одном уровне дискриминации, что ведет к избыточности информации, выдаваемой им. Цель изобретения - уменьшение объема оборудования щсфрового дискриминатора. Поставленная цель достигается тем, что цифровой дискриминатор, содержащий счетчик, переключатель уровней, первый и второй блоки сравнения и блок выдачи, причем входы первой группы первого блока сравнения соединень с выходами переключателя уровней, содержит блок памяти и блок управлешы, причем выходы п младших разрядов счетчика

(n к, где к - разрядность счетчика) соединены со входами второй группы первого блока сравнения, входы первой группы второго блок Ьравнения соединены с выходами (п+1) младших разрядов счетчика и с информационными входами блока памяти, выходы которого соединены со входами второй группы второго блока сравнения, выходы разрядов счетчика соединены с информационными входами блока выдачи, первый, второй и третий входы блока ут1равлення соединены соответственно с выходами первого и второго блоков сравнения и с управляющим входом дискриминатора, первый и второй выходы блока управления соединены соответственно с управляющими входами блока памяти и блока выдачи, информационный вход дискриминатора соединен со счетным входом счетчика, выходы блока выдачи и первого блока сравнения являются выходами дискриминатора.

Кроме того, блок управления содержит элемент И и элемент задержки, выход которого соединен с первым выходом блока,первый, второй и третий входы которого соединены со входами элемента И, выход которого соединен со вторым выходом блока.

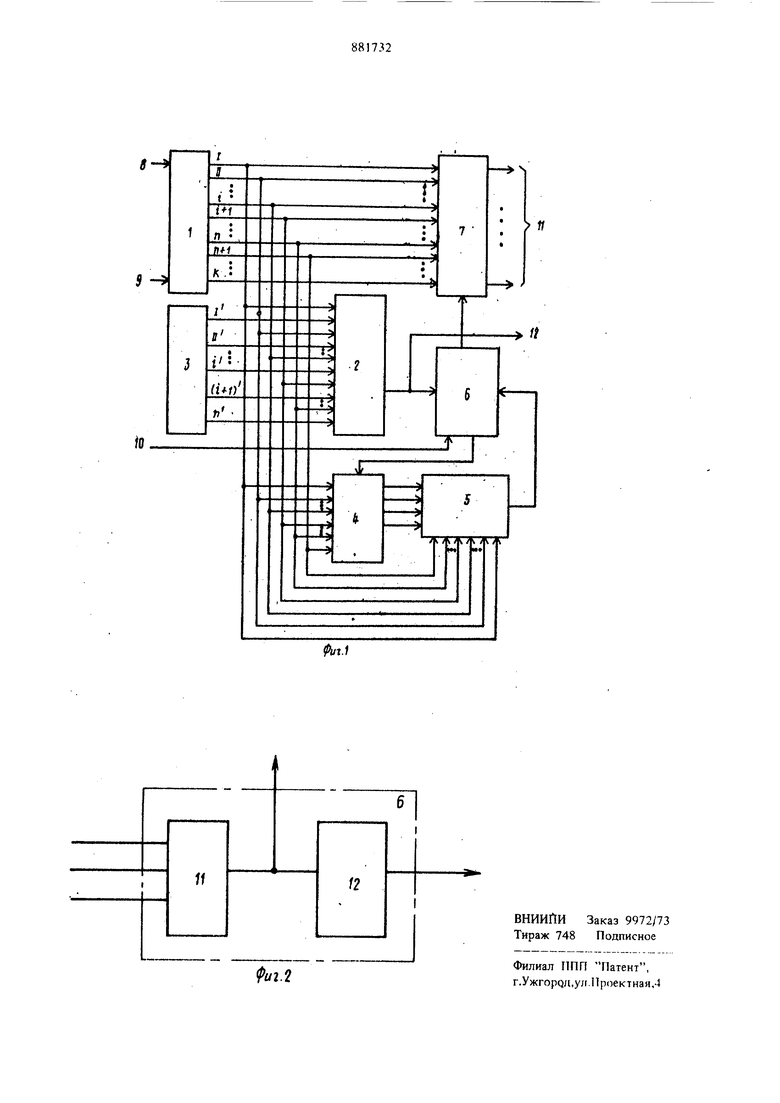

На фиг. 1 представлена блок-схема цифрового дискриминатора; на фиг. 2 - схема блока управления.

Цифровой дискриминатор содержит счетчик 1, блок сравнения 2, переключатель уровней 3, блок памяти 4, блок сравнения 5, блок управления 6, блок вьщачи 7, информационный вход 8, устанс вочный вход 9, управляющий вход 10, выходы 11 и 12.

Принцип работы устройства заключается в следующем.

Уровни дискриминации устанавлнвак)тся с шагом, равным числу 2, где n - 1, 2, 3 ... Для определения совпадения исследуемой величины анализируются все n младших разрядов кода зтой величины, где n соответствует показателю степени числа 2 выбранного шага уровня дискриминации. Таким образом, если все анализируемые младшие разряды равны нулю, то, следовательно, исследуемая величина совпадает с одним из уровней дискриминации.

Устройство работает следующим образом..

В начале дакла по входу 9 подается импуль начала преобразования исследуемой величины, при этом счетчик 1 обнуляется. Мгновенное значение исследуемой величины в виде унитарного кода подается по входу 8 на вход счетчика 1, увеличивая его содержимое. Младшие разряды кода с выходов n младших разрядов счетчика подаются на одни выходы блока сравнения 2, а на другие его входы подается код шага уровней дискриминации с выходов переключателя уровней 3. Переключателем

уровня 3 можно установить любой шаг уровня дискриминации от 2 до 2, где п - 1, 2, 3 ... Если шаг уровня дискриминации устанавливается равным 2, то сигналы высокого уровня (логическая 1) подаются с выходов переклю чателя 3 с первого по i -и, а по остальным выходам подаются сигналы низкого уровня (логический ). При этом каждое текущее значение исследуемой величины, у которой- состояние младших разрядов с первого по j -и равно логическому О, поступая на блок сравнения 2, формирует на его выходе, а также на выходе 12 сигнал логической 1, означающий достижение исследуемой величины очередного уровня дискриминации. Более старшие разряды (с (i +1)-го по п-й) кода исследуемой величины в анализе не участвуют, так как они блокируются сигналами логического О от соответствующих шин переключателя уровней 3.

В конце преобразования на выходах счетчика 1 формируется потенциальный код исследуемой величины за этот цикл исследования. Если этот код соответствует одному из уровней дискриминации, то на выходе блока сравнения 2 формируется разрешающий сигнал. Импульс конца преобразования по входу 10 поступает в блок управления 6 и, если отсутствует сигнал запрета на выходе блока сравнения 5, то блок управления б выдает сигнал разрешения в блок выдачи 7, по которому код исследуемой величины, соответствующий одному из уровней дискриминации, выводится на выходы Ц. Кроме того, в момент отпирания блока выдачи 7 с другого выхода блока управления 6 форми руетсй сигнал, по которому в блок памяти 4 записывается п+1 младших разрядов кода исследуемой величины.

Для фиксации наибольшего значения исследуемой величины, достигшей нового уровня д скриминации (большого или меньшего), к блоку памяти 4 и блоку сравнения 5 подключены п+1 разрядов, так как при анализе исследуемой величины по уровням дискриминации с шагом, равным п, код числа, соответствующий следующему уровню дискриминации, имеет в (п+1)-ом разряде состояние, обратное состоянию (п+1)-го разряда кода последнего зафиксированного значения исследуемой величины.

Если в результате наложения высокочастотной помехи исследуемая величина за второй и последующие циклы преобразования находится в пределах последнего зафиксированного уровня, то в случае неравенства предыдущему значению

на выходе блока сравнения 2 будет запрещающий сигнал; в случае равенства на выходы блока сравнения 5 поступают одинаковые коды с п+1 выходов младших разрядов счетчика 1

и с выходов блока памяти 4, т.е. на выходе блока сравнения 5 появится сигнал запрета.

При достижении исследуемой величиной за цикл преобразования нового уровня дискриминации на выходах блока управления 6 формируются сигналы, обеспечивающие выход кода исследуемой величины на выход 11 и запись в блок памяти 4 новых значений п+1 младших разрядов этой величины.

Данный цифровой дискримииатор имеет по сравнению с известным, меньшее количество оборудования.

Кроме того, снижена по сравнению с известным избыточность информации, выдаваемой, дискриминатором.

Формула изобретения

сравнения, входы первой группы второго блока сравнения соединены с выходами (п-М) младших разрядов счетчика и с информационными входами блока памяти, выходы которого соединены

со входами второй группы второго блока

сравнения, выходы разрядов счетчика соединены с информационными входакш блока выддчи, первый, второй и третий входы блока управления соединены соответственно с выходами

первого и второго блоков сравнения и с управляюцдам входом дискриминатора, первый и второй выходы блока управления соединены соответственно с управляющими входами блока памяти и блока вьщачи, информационный

вход дискриминатора соединен со счетным входом счетчика, выходы блока выдачи и первого блока сравнения являются вьтходамн дискриминатора.

со вторьпи выходом блока.

Источники информации, принятые во вшшание при экспертизе 1.0 Авторское свидетельство СССР Ц. 329527, кл. G 06 F 15/36, 1971.

кл. G 06 F 7/00, 1975 (прототип).

Авторы

Даты

1981-11-15—Публикация

1979-09-24—Подача