с управлякицими входами соответственно первого и BTopoio блоков сравнения, выход первого элемента и блока управления соединен с входом синхронизации регистра результата, первый и второй выходы первого блока сравнения соединены соответственно со вторым и третьим входами первого элемента ИЛИ блока управления, первьй и второй выходы второго блока сравнения соединены соответственно с вторым и третьим входами второго элемента ИЛИ блока управления.

2. Дискриминатор по п. 1, отличающийся тем, что блок сравнения содержит сумматор, вычитатель, два регистра и два узла сравнения, причем первая группа информационных входов блока соединена с первыми

группами входов сумматора, вычитатёля, первого и второго узлов сравнения, вторая группа информационных входов блока соединена с вторыми группами входов сумматора и вычитателя, выходы сумматора соединены с информационными входами -первого регистра, выходы которого подключены к второй группе входов первого узла сравнения, выход которого соединен с первым выходом блока, выходы вычитателя соединены с информационными входами второго регистра, выходы которого соединены с второй группой входов второго узла сравнения, выход которого соединен с вторым выходом блока, управляющий вход блока соединен с входами синхронизации первого и второго регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой дискриминатор | 1985 |

|

SU1312564A1 |

| Цифровой дискриминатор | 1983 |

|

SU1128248A1 |

| Цифровой дискриминатор | 1984 |

|

SU1259244A1 |

| Цифровой дискриминатор | 1985 |

|

SU1288687A1 |

| Цифровой дискриминатор | 1983 |

|

SU1128247A1 |

| Цифровой дискриминатор | 1981 |

|

SU1023320A1 |

| Система программного управления процессом порционной вакуумной обработки стали | 1989 |

|

SU1684347A2 |

| Вычислительное устройство | 1980 |

|

SU1001090A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

1. ЦИФРОВОЙ ДИСКРИМИНАТОР, содержащий счетчик первого параметра, счетчик второго параметра, первый блок сравнения, регистр результатови блок управления, блок управления содержит два элемента И, триггер, элемент ИЛИ и элемент задержки, причем вход запуска дискриминатора соединен со счетным входом триггера и первым входом первого элемента ИЛИ, вход первого параметра дискриминатора соединен со счетным входом счетчика первого параметра, выходы которого соединены с первой группой информа-г ционных входов регистра результата, вход второго параметра дискриминатора соединен со счетным входом счетчика второго параметра, выходы которого соединены с второй группой информационных входов регистра результата, выходы которого соедине.ны с выходами дискриминатора, первая группа входов задания уровней дискриминации дискриминат.ора соединана с первой группой информационных входов первого блока сравнения, отличающий с я тем, что, с целью расширения функциональных возможностей за счет дискриминации по разности и сумме параметров в него введены сумматор, вычитатель и второй блок сравнения, а в Олокуправления введены третий элемент И и второй и третий элементы ИЛИ, причем в блоке управления инверсный выход триггера соединен с первыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с первым и вторым входами третьего элемента ИЛИ и i первыми входами соответственно второго и третьего элементов И, выход (Л третьего элемента ИЛИ соединен с вторым входом первого элемента И, выход которого через элемент задержки соединен с вторыми входами первого и третьего элементов И, вторая группа входов задания уровня дискриминации дискриминатора соединена с первой группой информации входов второго блока управления, выходы счетчика первого параметра соединены с первыми группами входов сумматора и вычиj;;. тателя, выходы счетчика второго пара4 метра соединены с вторыми группами входов сумматора и вычитателя, выходы сумматора соединены с второй группой информационных входов первого блока сравнения и третьей группой информационных входов регистра результата, выходы вычитателя соединены с второй группой информационный входов второго блока сравнения и четвертой группой информационных входов регистра результата, выходы второго и третьего элементов блока управления соединены

I

Изобретение относится к вычислительной и информационно-измерительной технике и может найти применение в системах регистрации и обработки случайных сигналов.

Целью изобретения является расширение функциональных возможностей за счет дискриминации по разности и сумме параметров.

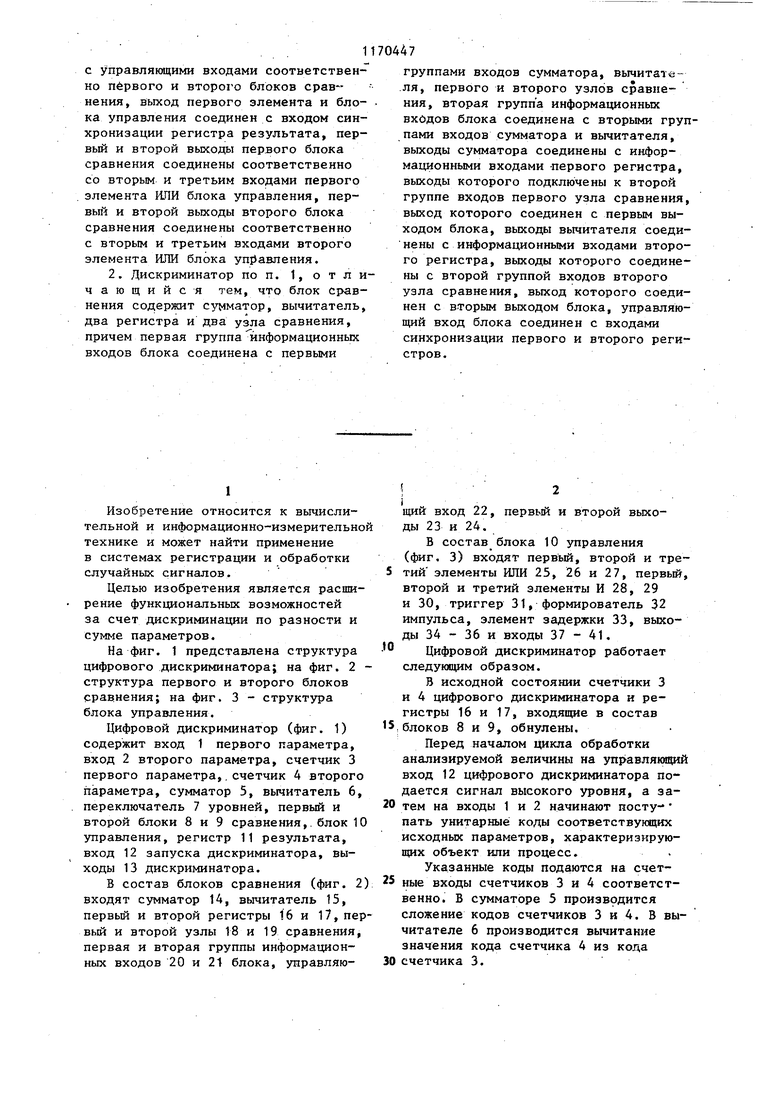

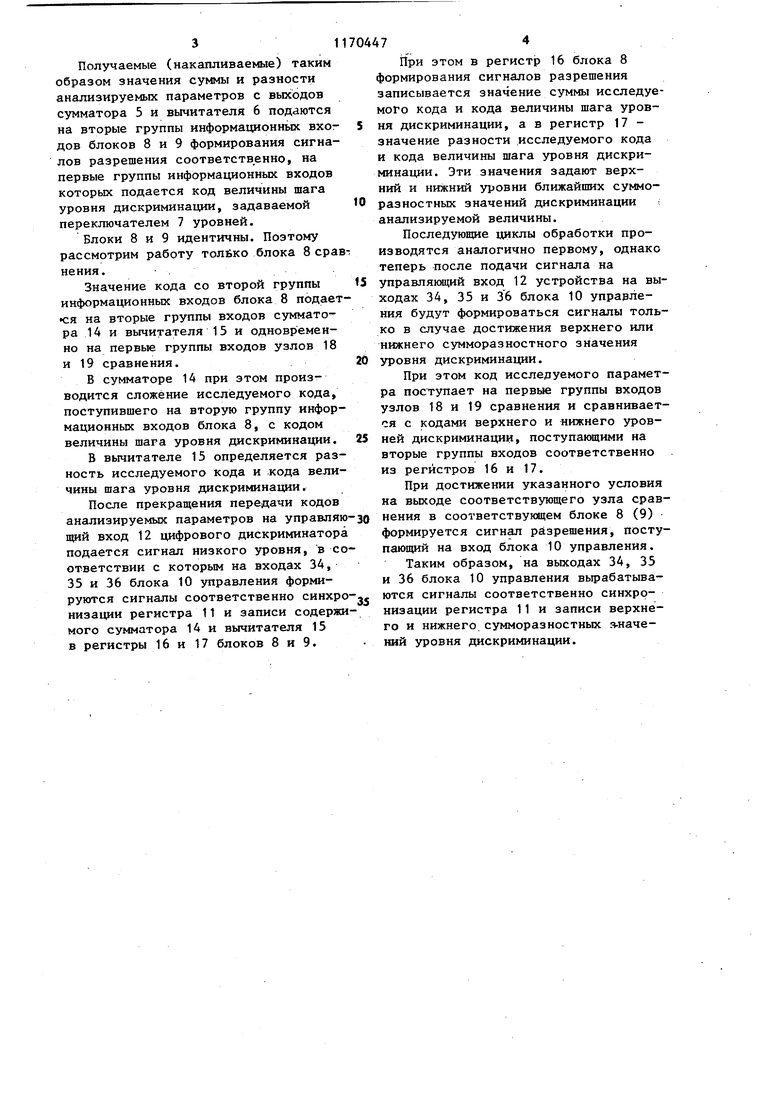

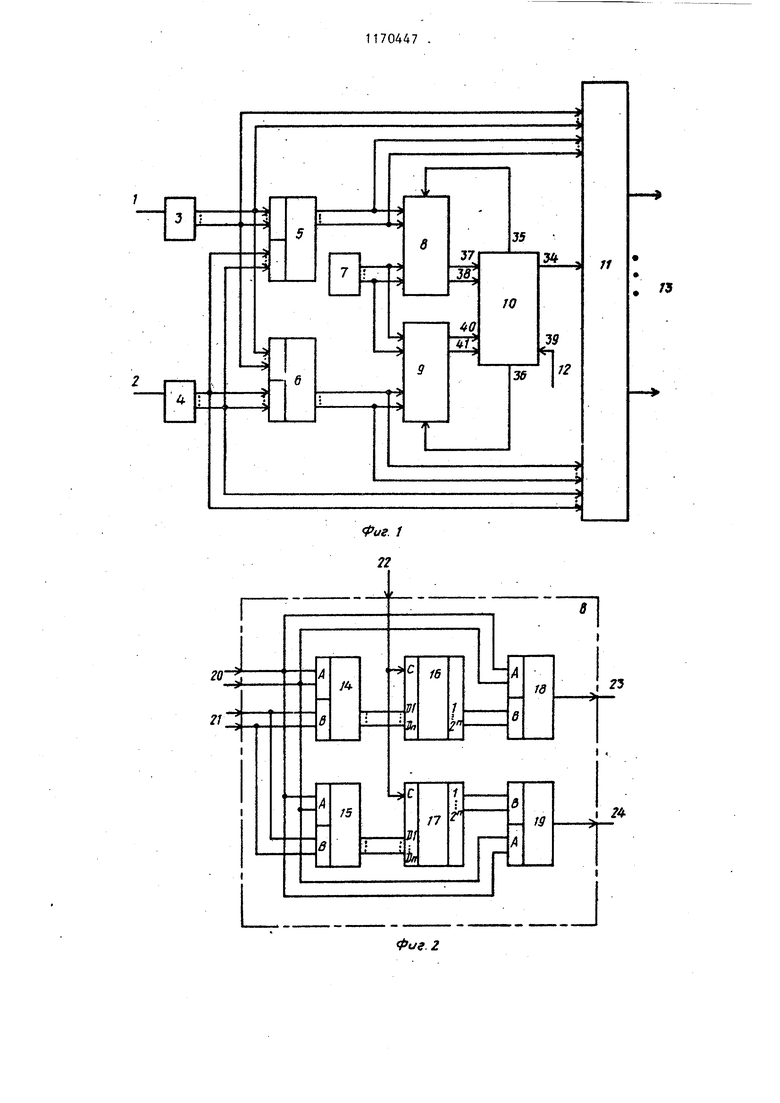

На фиг. 1 представлена структура цифрового дискриминатора; на фиг. 2 структура первого и второго блоков сравнения; на фиг. 3 - структура блока управления.

Цифровой дискриминатор (фиг. 1) содержит вход 1 первого параметра, вход 2 второго параметра, счетчик 3 первого параметра,, счетчик 4 второго параметра, сумматор 5, вычитатель 6, переключатель 7 уровней, первый и второй блоки 8 и 9 сравнения,, блок 10 управления, регистр 11 результата, вход 12 запуска дискриминатора, выходы 13 дискриминатора.

В состав блоков сравнения (фиг. 2) входят сумматор 14, вычитатель 15, первый и второй регистры 16 и 17, первый и второй узлы 18 и 19 сравнения, первая и вторая группы информационных входов 20 и 2t блока, управляющий вход 22, первый и второй выходы 23 и 24.

В состав блока 10 управления (фиг. 3) входят первый, второй и тре5 тий элементы ИЛИ 25, 26 и 27, первый второй и третий элементы И 28, 29 и 30, триггер 31, формирователь 32 импульса, элемент задержки 33, выходы 34 - 36 и входы 37-41. Цифровой дискриминатор работает следующим образом.

В исходной состоянии счетчики 3 и 4 цифрового дискриминатора и регистры 16 и 17, входящие в состав 15,блоков 8 и 9, обнулены.

Перед началом цикла обработки анализируемой величины на управляющи вход 12 цифрового дискриминатора подается сигнал высокого уровня, а затем на входы 1 и 2 начинают посту- пать унитарные; коды соответствующих исходных параметров, характеризирующих объект или процесс.

Указанные коды подаются на счетные входы счетчиков 3 и 4 соответственно. В сумматоре 5 производится сложение кодов счетчиков 3 и 4. В вычитателе 6 производится вычитание значения кода счетчика 4 из кода 30 счетчика 3.

Получаемые (накапливаемые) таким образом значения суммы и разности анализируемых параметров с выходов сумматора 5 и вычитателя 6 подаются на вторые группы информационных вхотДОН блоков 8 и 9 формирования сигналов разрешения соответственно, на первые группы информационных входов которых подается код величины шага уровня дискриминации, задаваемой переключателем 7 уровней.

Блоки 8 и 9 идентичны. Поэтому рассмотрим работу толйко блока 8 срав нения.

Значение кода со второй группы информационных входов блока 8 подается на вторые группы входов сумматора 14 и вычитателя 15 и одновременно на первые группы входов узлов 18 и 19 сравнения.

В сумматоре 14 при этом производится сложение исследуемого кода, поступившего на вторую группу информационных входов блока 8, с кодом величины шага уровня дискриминации.

В вычитателе 15 определяется разность исследуемого кода и кода величины шага уровня дискриминации.

После прекращения передачи кодов анализируемых параметров на управляю щий вход 12 цифрового дискриминатора подается сигнал низкого уровня, в соответствии с которым на входах 34, 35 и 36 блока 10 управления формируются сигналы соответственно синхро низации регистра 11 и записи содержимого сумматора 14 и вычитателя 15 в регистры 16 и 17 блоков 8 и 9.

При этом в регистр 16 блока 8 формирования сигналов разрешения записывается значение суммы исследуемого кода и кода величины шага уровня дискриминации, а в регистр 17 значение разности исследуемого кода и кода величины шага уровня дискриминации. Эти значения задают верхний и нижний уровни ближайших сумморазностных значений дискриминации анализируемой величины.

Последую цие циклы обработки производятся аналогично первому, однако теперь лосле подачи сигнала на управлякмций вход 12 устройства на выходах 34, 35 и 36 блока 10 управления будут формироваться сигналы только в случае достижения верхнего или нижнего сумморазностного значения уровня дискриминации.

При этом код исследуемого параметра поступает на первые группы входов узлов 18 и 19 сравнения и сравнивается с кодами верхнего и нижнего уровней дискриминации, поступающими на вторые группы входов соответственно из регистров 16 и 17.

При достижении указанного условия на выходе соответствующего узла сравнения в соответствующем блоке 8 (9) формируется сигнал разрешения, поступающий на вход блока 10 управления.

Таким образом, на выходах 34, 35 и 36 блока 10 управления вьфабатываются сигналы соответственно синхронизации регистра 11 и записи верхнего и нижнего сумморазностных з-начений уровня дискриминации.

фаг. 2

Фиг. 3

| Многоканальный цифровой дискриминатор | 1975 |

|

SU591854A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой дискриминатор | 1981 |

|

SU1023320A1 |

Авторы

Даты

1985-07-30—Публикация

1983-12-26—Подача