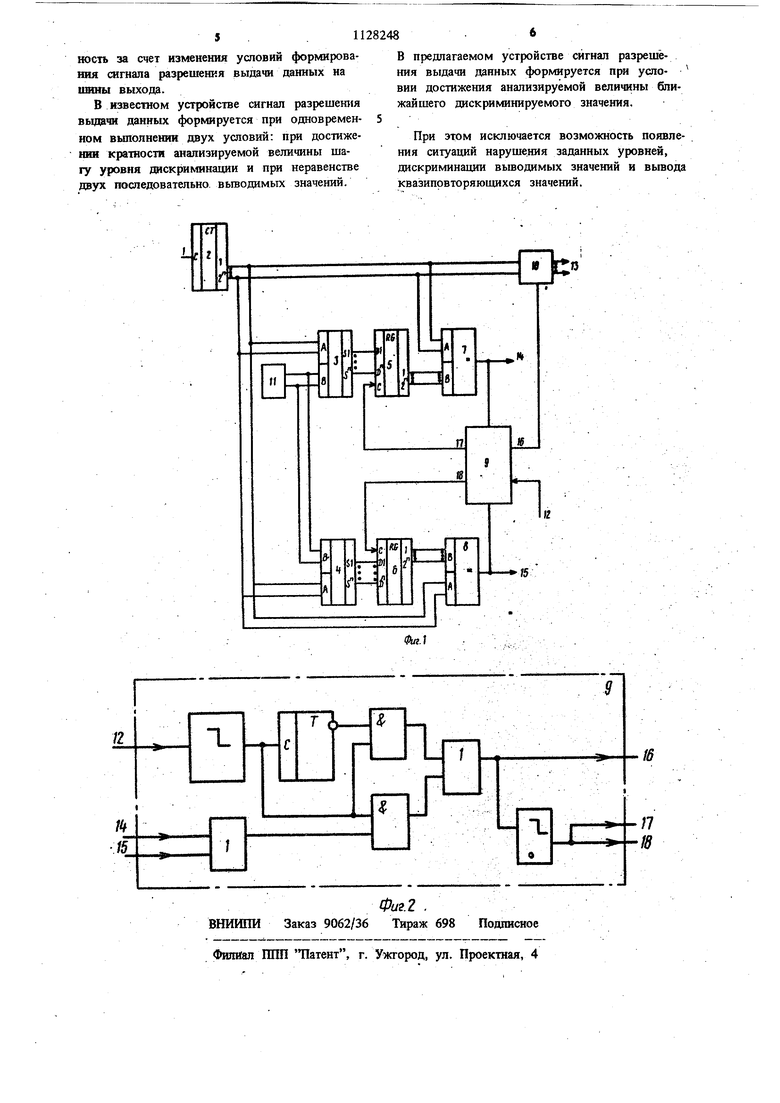

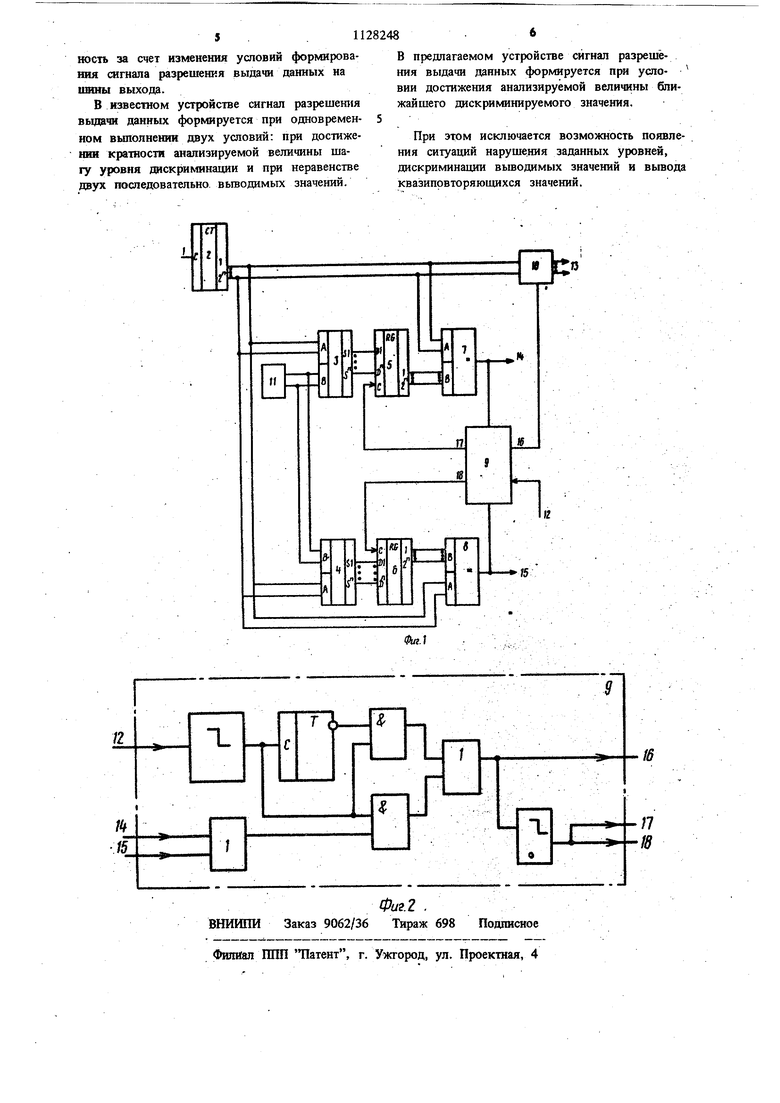

Изобретение относится к области информационно-измерительной и вычислительной техники и может найти применение в системах регистрации и обработки случайньгх сигналов J в частности может быть использовано для обработки данных, получаемых от координатографа.. Известен многоканальный цифровой дискриминатор, содержащий блок счетчиков исследуемой величины, переключатели уровней и блоки сравнения по числу уровней дискриминации, триггеры и блок совпадения 11 Это устройство MOJtceT дискриминировать анализируемую величину по ряду уровней дискриминации, однако состоит из одноканальных дискриминаторов, что требует большого объема оборудования. Наиболее близким к изобретению . является цифровой дискриминатор, содержащий первый и второй счетчики, первый и второй блоки памяти, первый и второй злементы сравнения, переключатель уровней, блок управления и блок выдачи, причем выходы разрядов первого счетчика соединены с установочными входами первого блока памяти, первой группой входов первого элемента сравнения и информационными входами блока выдачи, выходы которого являются выходами устройства, выходы первого блока памяти соединены с второй группой входов первого элемента сравнения, выход которого соединен с первым управляющим входом блока управления, второй управляющий вход которого является зшравляющим входом уст ройства, первый и второй выходы блока уп равления соединены соответственно с управляющими входами первого блока памяти и блока выдачи, счетный вход первого счетшка соединен с информационным входом устройства и со счетным входом второго счетчика, выходы разрядов которого соединены с группой информационных входов блока правления, второй группой входов второго злемента сравнения и группой установочных входов второго блока памяти, инверсные выходы разрядов которого соединены с уста новочными входами второго счетчика, третий и четвертый выходы блока управления соеди нены с управляющими входами второго бло ка памяти и второго счетчика соответственно. Выходы переключателя уровней соединены с первой группой входов второго элеме та сравнения, выход которого соединен с вх дом установки второго счетчика в нулевое состояние, блок управления цифрового дискриминахора содержит формирователь переднего фронта, первый и второй формирователи заднего фронта, триггер, первый и второй элементы И, элемент ИЛИ, элемент ИЛИ-НЕ, причем группа информационных входов блока соединена с входами элемента ИЛИ-НЕ, выход которого соединен с входом первого элемента И, выход которого соединен с входом злемента ИЛИ и с входом первого формирователя заднего фронта, выход которого является первым выходом блока, первый управляющий вход 6iiioка соединен с входом первого элемента Н, второй управляющий вход блока соединен с входами формирователя переднего фронта и второго формирователя заднего фронта, выход которого соединен с входом синхронизации триггера, входами первого и второго элемента И, нулевой выход триггера соединен с входом Второго злемента И, выход которого соединен с входом элемента ИЛИ, выход которого является вторым выходом блока, выход второго элемента И является третьим выходом блока, выход . формирователя переднего фронта является четвертым выходом блока 2. Недостатком известного цифрового дискриминатора является низкая функциональная надежность вследствие возможности нарущения заданных уровней дискри ганации вьгеодимых значений, а также вьгеОда квазиповторяющихся (отличающихся, на единицу) значений в области уровня дискриминации, что наряду с нарушением функций дискриминатора приводит к избыточности вьшодимой информации. Указанные сбои в работе дискриминатора возникают, когда первый и второй счетчики дискриминатора из-за технологических разбросов параметров фиксируют различающиеся значения анализируемой величины при наличии в поступающем унитарном коде укоро-. ченного импульса, формируемого, например, при окончании тактирования временных интервалов,г При этом в области значений уровней дискриминации, возникают ситуации, когда второй счетчик, участвующий в формировании сигнала разрешения вывода дискриминируемых значений, дает такое разрешение, а первый счетчик, участвующий в формирова- . НИИ сигнала запрета вывода повторных значений, не вводит запрет и значение анализируемой величинь(, зафиксированное первым счетчиком, вьпзоднтся. Целью изобретения является повышение достоверности цифрового дискриминатора за счет устранения условий разночтения при формировании заданных уровней дискримичации. Поставленная цель достигается тем, что в цифровой дискриминатор, содержащий счетчик, переключатель уровней, первый и второй блоки памяти, первый и второй элементы сравнения, блок выдачи числа и блок управления, включающий триггер, первый и второй элементы И, первый элемент ИЛИ, формирователи заднего фрюнта импульса, причем информадионный вход устройства соединен со счетным входом счетчика, выходы разрядов которого соединены с первой группой входов первого элемента сравнения и информационными входами блока выдачи числа, выходы которого являются выходами устройства, выходы первого блока пам,яти соединены с второй группой входов первого элемента сравнения, вход разрешения записи кода устройства подключен к входу первого формирователя заднего фронта импульса, выход ко торого подключен К первым входам первого и второго элементов И и синхронизирующему входу триггера, инверсный которого соединён с вторым входом первого элемента И, выходы первого и второго элементов И подключены к входам первого элемента ИЛИ, выход которого соединен с входом разрешения выдачи блока выдачи числа и через второй формирователь заднего фронта имяулься с входом разрешения записи пер вого блока памяти, введены сумматор и вычитатель, первые группы входов которых подключены к выходам переключателя уров ней, а вторые группы входов - к выходам разрядов счетчика и первой группе входов второго элемента сравнения, вторая группа входов которого подключена к выходам второго блока памяти, установЗчные входы которого соединены с выходами вычитателя, а вход разрешения записи - с выходом второго формирователя заднего фронта импульса, в блок управления дополнительно введен второй элемент ИЛИ, выход которого соединен с вторым входом второго элемента И, а входы подключены к выходам первого и второго элементов сравнения. Для отчета уровней дискриминации от первоначально поступившей анализируемой величины, от значения ее, зафиксированного счетчиком, складывается (вычисляется) значение . соответствующих ближайших верхнего и нижнего уровней дискриминации. При этом индивидуальные параметры счетчика влияют оди наково на формирование соответствующих вьтодимых значегат. На фиг. 1 приведена структурная схема цифрового дискриминатора; на фиг. 2 - схе ма блока управления. Устройство содержит информационный вход 1, счетчик 2, сумматор 3, вычитатель 4, . вый и второй блоки 5 и 6 памяти, первый и второй элементы 7 и 8 сравнения, блок 9 управления, блок 10 выдачи числа, переключатель 11 уровней, вход 22 разрешения записи кода, выходы 13, выходы 14 и 15, одновременно являющиеся первым и третьим управляющими входами блока управления, выходы 16-18 блока управления. Цифровой дискриминатор работает следующим образом. В исходном состоянии в счетчик 2 и блок 5 и 6 памяти записаны нули. Перед началом цикла обработки на joipaBляющий вход 12 подается сигнал высокого уровня и на информационный вход 1 начинает поступать угштарный код анализируемой величины, который подается на счетный вход счетчика 2, Код, преобразующийся в счетчике 2, складьшается в сумматоре 3 с кодом величины тага уровня дискриминации, который задан переключателем 11 уровней, а в вычитателе 4 из кода, образующегося в счетчике 2, вычитается величина шага уровНя дискриминации. После прекращения передачи кода анализируемой величины на вход. 12 подается сигнал низкого уровня, в соответствии с которым на выходах 16-18 блока 9 управления формируются сигналы соответственно отпирания блока 10 выдачи числа и записи содержимого сумматора 3 и вычитателя 4 в блоки 5 и 6 памяти. В блок 5 памяти при этом записывается код суммы анализируемой величины и шага уровня дискриминации, а в блок 6 памяти соответственно код разности указанных параметров, которые задают верхний и нижний уровни ближайшего дискриминируемого значения. Последующие циклы обработки производятся аналогично первому, однако теперь после подачи сигнала на управляющий вход 12 устройства на выходах 16-18 блока 9 управления формируются сигналы только в том случае, если на выходе одного из элементов 7 и 8 сравнения возникает сигнал равенства. Этот сигнал формируется, когда анализируемая величина достигает одного из двух ближайших сформированных дискриминируемых значений. При вьшолнении этого условия на выходе 13 устройства формируется код исследуемой величины. В предлагаемом цифровом дискриминаторе путем Введения сумматора, вычитателя и новых связей устранена избыточность выдаваемой информации н повышена достоверHocib за счет изменения условий формирования сигнала разрешения выдачи данных на ишны выхода.

В известном устройстве сигнал разрешения выдачи данных формируется при одновременном выполнении двух условий: при достижении кратности анализируемой величины шагу уровня дискриминации и при неравенстве дв)гх последовательно вьгеодимых значений.

В предлагаемом устройстве сигнал разрешения выдачи данных формируется при уелоВИИ достижения анализируемой величины ближайшего дискриминируемого значения.

При этом исключается возможность появления ситуаш1й нарушения заданных уровней, дискриминации вьшодимых значений и вывода квазипрвторяющихся значений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой дискриминатор | 1985 |

|

SU1312564A1 |

| Цифровой дискриминатор | 1983 |

|

SU1128247A1 |

| Цифровой дискриминатор | 1981 |

|

SU1003069A1 |

| Цифровой дискриминатор | 1984 |

|

SU1259244A1 |

| Цифровой дискриминатор | 1985 |

|

SU1288687A1 |

| Цифровой дискриминатор | 1983 |

|

SU1170447A1 |

| Цифровой дискриминатор | 1981 |

|

SU1023320A1 |

| Цифровой дискриминатор | 1979 |

|

SU881732A1 |

| Цифровой дискриминатор | 1983 |

|

SU1151951A1 |

| Амплитудный дифференциальный дискриминатор | 1978 |

|

SU765780A1 |

ЦИФРОВОЙ ДИСКРИМИНАТОР, содержащий счетчик, переключатель уровней, первый и второй блоки памяти, первый и второй элементы сравнения, блок выдачи числа и блок управления, включающий триггер первый и второй элементы И, первый элемент ИЛИ, формирователи заднего фронта импульса, причем информационный вход устройства соединен со счетным входом счетчика, выходы разрядов которого соединены с первой группой входов первого элемента сравнения и информационными входами блока выдачи числа, выходы которого являются выходами устройства, выходы первого блока памяти соединены с второй группой входов первого элемента сравнения, вход разрещеш1я записи кода устройства подключен к входу первого формирователя заднего фронта импульса, выход которого подключен к первым входам первого и второго элементов И и синхронизирующему входу триггера, инверсный выход, которого соединен с вторым входом первого элемента И, выходы первого и второго элементов И подключены к входам первого элемента ИЛИ, выход которого соединен с входом разрещения выдачи блока выдач 1 )числа и. через второй формирователь заднего фронта импульса с входом разрешения записи первого блока памяти, отличающийся тем, что, с цель.ю повыщения достоверности цифрового дискриминатора за счет устранения условий разночтения при формировании заданных уровней дискриминации, в него введены сум(Л матор и вычитатель, первые группы входов которых подключены к выходам переключателя уровней, а вторые группы - к выходам разрядов счетчика и первой группе входов второго элемента сравнения, вторая группа входов которого подключена к вы- . ходам второго блока памяти, установочные N9 входы которого соединены с выходами выX) читателя, а вход разрешения записи с выходом второго формирователя задаего фроио та импульса, в блок управления дополни41 Х тельно введен второй элемент ИЛИ, выход кЬторого соединен с вторым входом второго этемента И, а входы подключены к выходам первого и второго элементов сравнения.

}:

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальный цифровой дискриминатор | 1975 |

|

SU591854A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой дискриминатор | 1981 |

|

SU1003069A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-07—Публикация

1983-06-09—Подача