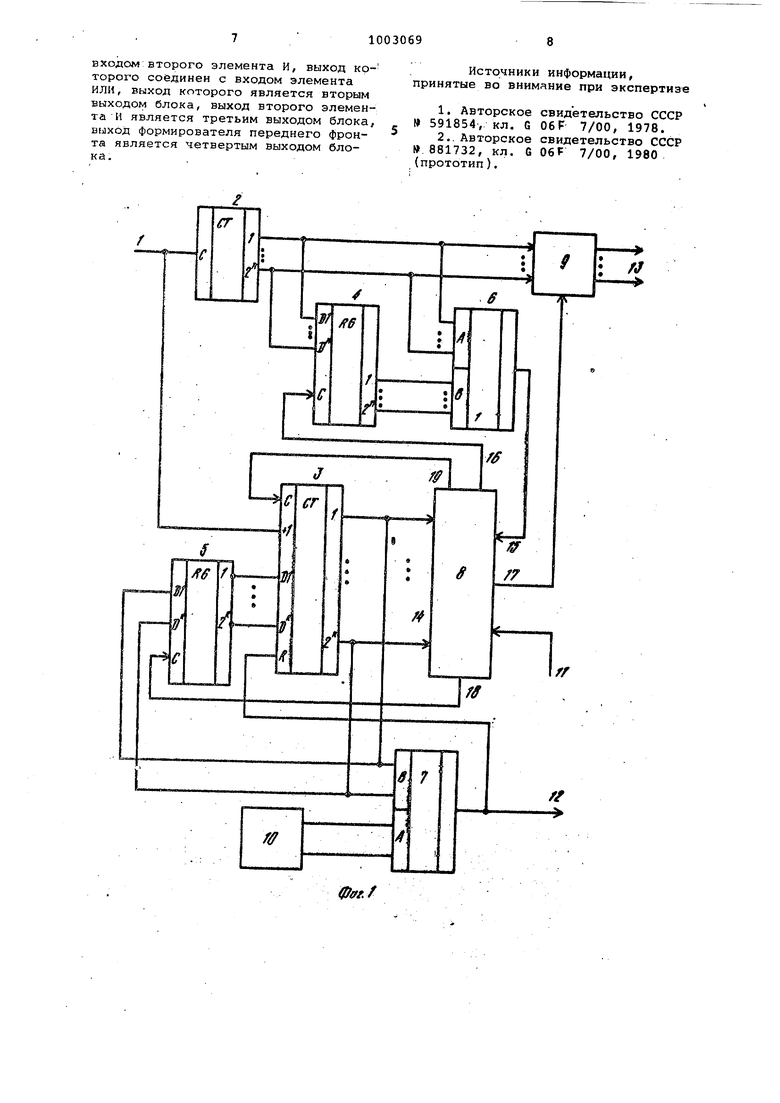

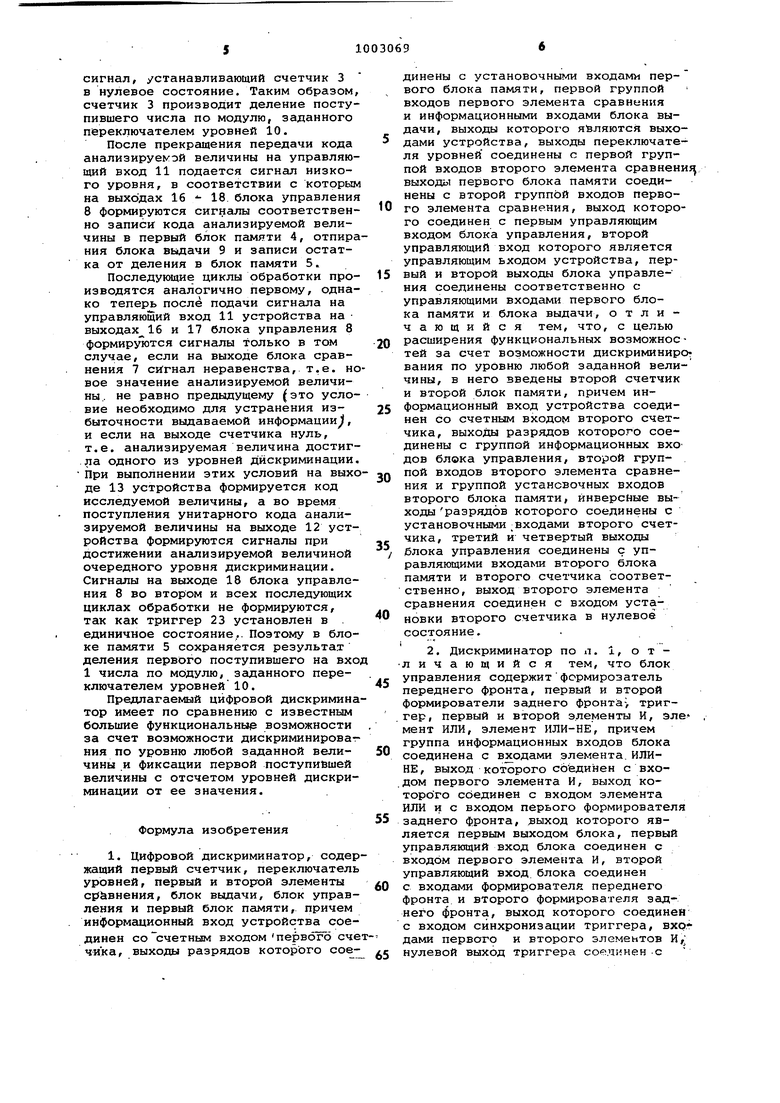

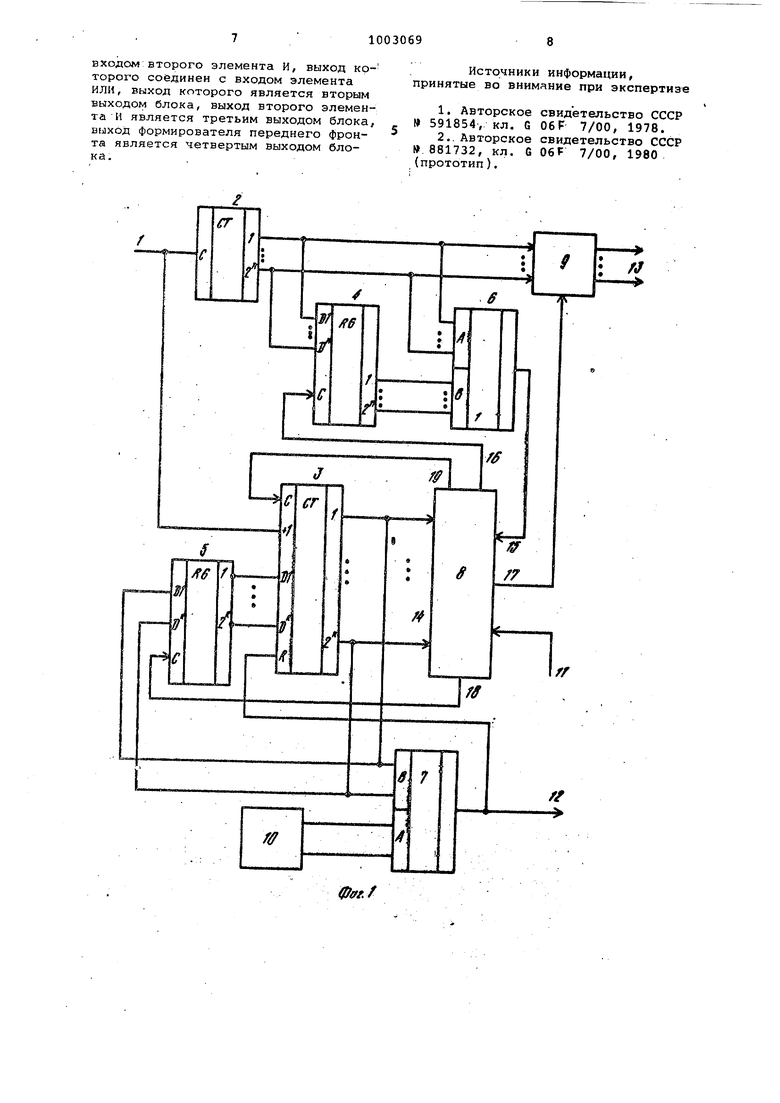

дискриминации с шагом 2 } где п - целое число. Целью изобретения является расшир ние функциональных возможностей цифрового дискриминатора за счет возможности дискриминирования по уровню любой заданной величины. Поставленная цель достигается тем, что в цифровой дискриминатор, содержащий первый счетчик, переключатель уровней, первый и второй элементы сравненип, блок выдачи, блок управления и первый блок памяти, причем информационный вход устройстJNa соединен со счетным входом перво о счетчика, выходы разрядов которого соединены с установочными входами первого блока памяти, первой группой входов первого элемента сравнения и информационными входами блока выдачи, выходы которого являются выходами устройства, выходы переключателя уровней соединены с первой группой входов второго элемента сравнения, выходы nepBoiQ блока памяти соединены с второй группой входов первого элемента сравнения, выход каторого соединен с первым управляющим входом блока управления, второй управляющий вход которого является управляю щим входом устройства, первый и второй выходы блока управления соединены соответственно с управляющими вхо дами первого блока памяти и блока вЫ дачи, введены второй счетчик и второй блок памяти, причем информационный вход устройства соединен со счетным входом второго счетчика, выходы разрядов которого соединены с группой информационных входов блока управления, второй группой входов второго элемента сравнения и группой установочных входов второго блока памяти, инверсные выходы разрядов кО торого соединены с установочными входами второго счетчика, третий и четвертый выходы блока управления . соединены с управляющими входами -вто рого блока памяти и второго счетчика соответственно, выход второгЪ элемента сравнения соединен с входом установки второго счетчика в нулевое состояние.... Шри этом блок управления содержи формирователь переднего фронта, первый и второй формирователи заднего фронта, триггер, первый и второй элементы и, элемент ИЛИ, элемент ИЛИ-НЕ, причем группа информационных входов блока соединена с входами элемента ИЛИ-НЕ, выход которого соединен с входом первого элемента И выход которого соединен с входом элемента ИЛИ и с входом первого фор мирователя заднего фронта, выход ко торого является первым выходом блок первый управляющими вход блока соеди нен с входом первого элемента И, второй управляющий вход блока соединен с входами формирователя переднего фронта и второго формирователя заднего фронта, выход которого соединен с входом синхронизации триггера, входами первого и второго элементов И, нулевой выход триггера соединен с входом второго элемента И, выход которого соединен с входом элемента ИЛИ, выход которого является вторым выходом блока, выход второго элемента И является третьим вы-; ходом блока, выход формирователя переднего фронта является четвертым выходом блока. .Принцип работы устройства заключается в определении кратности ; анализируемой величины шагу уровней дискриминации путем деления этой величины на величину шага.. Для отсчета уровней дискримина(ции от первоначально поступившей анализируемой величины остаток от деления ее запоминается/ а затем вычитается из последующих значений анализируемых величин. На фиг. 1 приведена структурная схема устройства на фиг. 2 - схема блока управления. Устройство содержит информационный вход 1, первый и второй счетчики 2 и 3 , первый и второй блоки памяти 4 и 5, первый и второй элементы сравнения б и 7, блок управления 8, блок вьщачи 9, переключатель уровней 10, управляющий вход 11, который является одновременно первым входом блока управления, выходы 12 и 13, группа входов блока управления 14, вход блока управления 15, первый - четвертый выходы 16 - 19 блока управления, формирователь переднего фронта 20, формирователи заднего фронта 21 и 22, триггер 23, элементы И 24 и 25, элемент ИЛИ 26, элемент ИЛИ-НЕ 27. Цифровой дискриминатор работает следующим образом. В исходном состоянии в счетчик 2 и блоки памяти 4 и 5 записаны нули. Перед началом цикла обработки на управляющий вход 11 подается сигнал высокого уровня, в соответствии с которым на выходе 19 блока управления 8 формируется сигнал разрешения записи в счетчик 3 содержимого блока .памяти 5, а затем на информационный вход 1 начинает поступать унитарный код анализируемой величины. Этот код подается на счетные входа счетчиков 2 и 3. Код, содержа- щийся в счетчике 3, сравнивается элементом сравнения 6 с кодом величины шага уровня дискриминации, который задан переключателем уровней 10. .- . . . При равенстве кодов на выходе элемента сравнения б формируется сигнал, устанавливающий счетчик 3 в нулевое состояние. Таким образом счетчик 3 производит деление поступившего числа по модулю, заданного переключателем уровней 10. После прекращения передачи кода анализируемой величины на управляющий вход 11 подается сигнал низкого уровня, в соответствии с которым на выходах 16 - 18 блока управления 8 формируются сигналы соответственно записи кода анализируемой величины в первый блок памяти 4, отпира ния блока вьдачи 9 и записи остатка от деления в блок памяти 5. Последующие циклы обработки производятся аналогично первому, однако теперь после подачи сигнала на управляющий вход 11 устройства на выходах 16 и 17 блока управления 8 формируются сигналы только в том случае, если на выходе блока сравнения 7 сигнал неравенства, т.е. но вое значение анализируемой величины, не равно предыдущему (это условие необходимо для устранения избыточности выдаваемой информации, и если на выходе счетчика нуль, т.е. анализируемая величина достиг.ла одного из уровней дискриминации. При выполнении этих условий на выхо де 13 устройства формируется код исследуемой величины, а во время поступления унитарного кода анализируемой величины на выходе 12 устройства формируются сигналы при достижении анализируемой величиной очередного уровня дискриминации. Сигналы на выходе 18 блока управления 8 во втором и всех последующих циклах обработки не формируются, так как триггер 23 установлен в . единичное состояние,. Поэтому в блоке памяти 5 сохраняется результат деления первого поступившего на вхо 1 числа по модулю, заданного переключателем уровней 10. Предлагаемый цифровой дискримина тор имеет по сравнению с известным большие функциональные возможности за счет возможности дискриминировагния по уровню любой заданной величины и фиксации первой поступившей величины с отсчетом уровней дискриминации от ее значения. Формула изобретения 1. Цифровой дискриминатор, содер жащий первый счетчик, переключатель уровней, первый и второй элементы сравнения, блок выдачи, блок управления и первый блок памяти, причем информационный вход устройства соединен со счетным входом первбгб сче чика, выходы разрядов которого соединены с установочными входами первого блока памяти, первой группой входов первого элемента сравнения и информационными входами блока выдачи, выходы которого яЬляются выходами устройства, выходы переключателя уровней соединены с первой группой входов второго элемента сравнени5 выходы первого блока памяти соединены с второй группой входов первого элемента сравнения, выход которого соединен с первым управляющим входом блока управления, второй управляющий вход которого является управляющим входом устройства, первый и второй выходы блока управления соединены соответственно с управляющими входами первого блока памяти и блока выдачи, отличающийся тем, что, с целью расширения функциональных возможное тей за счет возможности дискриминирот вания по уровню любой заданной величины, в него введены второй счетчик и второй блок памяти, причем информационный вход устройства соединен со счетным входом второго счетчика, выходы разрядов которого соединены с группой информационных вхо дов блока управления, второй группой входов второго элемента сравнения и группой установочных входов второго блока памяти, инверсные выходы разрядов которого соединены с установочными входами второго счетчика, третий и четвертый выходы блока управления соединены с управляющими входами второго блока памяти и второго счетчика соответственно, выход второго элемента сравнения соединен с входом установки второго счетчика в нулевое состояние. 2. Дискриминатор по п. 1, о т личающийся тем, что блок управления содержитформирователь переднего фронта, первый и второй формирователи заднего фронта-, триггер, первый и второй элементы И, эле мент ИЛИ, элемент ИЛИ-НЕ, причем группа информационных входов блока соединена с взсодами элемента. ИЛИНЕ, выход которого соединен с входом первого элемента И, выход которого соединен с входом элемента ИЛИ и с входом перього формирователя заднего фронта, выход которого явяется первым выходом блока, первый управляющий вход блока соединен с входом первого элемента И, второй управляющий вход, блока соединен с входами формирователя переднего фронта и второго формирователя заднего фронта, выход которого соединен с входом синхронизации триггера, вхо. дами первого и второго элементов И/ нулевой выход триггера сое.чинен .с

входом;второго элемента И, выход которого соединен с входом элемента ИЛИ, выход которого является вторым выходом блока, выход второго элемента Н является третьим выходом блока, выход формирователя переднего фронта является четвертым выходом блока.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР 591854, кл, G 06F 7/00, 1978.

2.. Авторское свидетельство СССР 881732, кл. G 06F 7/00, 1980

(прототип).

ff

fff

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой дискриминатор | 1983 |

|

SU1128248A1 |

| Цифровой дискриминатор | 1983 |

|

SU1128247A1 |

| Цифровой дискриминатор | 1984 |

|

SU1259244A1 |

| Цифровой дискриминатор | 1981 |

|

SU1023320A1 |

| Цифровой дискриминатор | 1985 |

|

SU1312564A1 |

| Цифровой дискриминатор | 1985 |

|

SU1288687A1 |

| Цифровой дискриминатор | 1983 |

|

SU1170447A1 |

| Цифровой дискриминатор | 1979 |

|

SU881732A1 |

| Цифровой дискриминатор | 1983 |

|

SU1151951A1 |

| ЦИФРОВОЙ ДИСКРИМИНАТОР | 1993 |

|

RU2072552C1 |

/J

//

/

fr

-гу

//

/4

/ff

22

ff

i 0fff.l

Авторы

Даты

1983-03-07—Публикация

1981-06-09—Подача