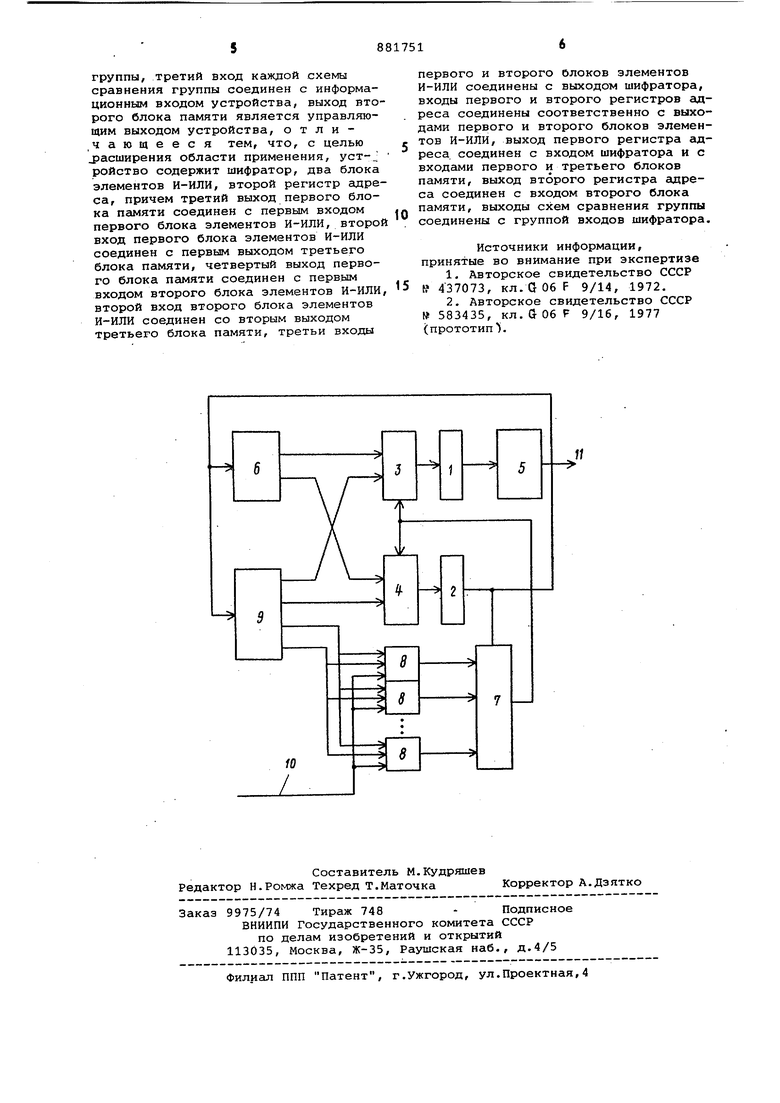

Изобретение относится к вычислительной технике и может быть использовано при создании микропрограммных процессоров. .Известно устройство микропрограммного управления, содержащее блок памяти, усилители, дешифратор, схему выбора, регистры адреса, схему управления, группы элементов И, группу эле ментов ИЛИ, триггер управления, блок объединения признаков условного перехода l . Недостатком такого устройства является большой объем оборудования. Наиболее близким к изобретению, по технической сущности и достигаемому результату является устройство многоnporpsiMMHoro управления, содержащее сравнения, три блока памяти, регисвгр кода операции, блок синхронизации/ регистр адреса, регистр микроко манды, дешифратор, формирователь фун кциональных сигналов 2. Однако такое устройство характери зуется ограниченной областью примене ния. Цель изобретения - расширение области применения устрюйства. Поставленная цель достигается тем, что в устройство микропрограммного управления, содержащее три блока „памяти, первый регистр адреса, группу схем сравнения, причем первый второй выходы первого блока памяти соединены соответственно с первым, вторым входами Кс1ждой схемы сравнения группы, третий вход каждой схемы сравнения группы соединен с информационным входом устройства, выход второго блока памяти является управляющим выходом устройства, введены шифратор, два блока элементов И-ИЛИ, второй регистр адреса, причем третий выход первого блока памяти соединен с первым входом первого блока элементов И-ИЛИ, второй вход первого блока элементов И-ИЛИ соединен с первым выходом третьего блока пг1мяти, четвертый выход первого блока памяти соединен с первым входом второго блока элементов И-ИЛИ, второй вход второго блока элементов И-ИЛИ соединен со вторым выходом третьего блока памяти, третьи входы первого и второго блоков элементов И-ИЛИ соединены с выходом шифратора, входы первого и второго регистров адреса соединены соответственно с выходами первого и второго блоков элементов И-ИЛИ, выход первого регистра адреса соединен с входом шифратора и с входами первого и третьего блоков памяти, выход второго регистра адреса соединен с входом второго блока памяти, выходы схем сравнения группы соединены с группой входов шифратора. На чертеже приведена блок-схема устройства. Устройство содержит регистры 1 и 2 адреса, блоки 3 и 4 элементов И-ИЛ блок 5 памяти микрокоманд, блок б па мяти адресов, шифратор 7, группу схе 8 сравнения, блок 9 памяти адресов, информационный вход 10 устройства, управляющий выход 11 устройства. Устройство работает следующим образом. В исходном состоянии в блоки памяти 5, 6 и 9 заносится необходимая информация, а в адресные регистры 1 и 2 - начальные адреса. В блок 5 памяти микрокоманд записываются все необходимые, причем различные, микрокоманды (МК) без какого-либо повторения или дублирования. Каждое слово блока 6 памяти адресов содержит адрес текущей МК из блока 5 , адрес безусловного (условного) перехода А+ . и адрес блока памяти адресов - Agp . Указанная информация записывается в блок б только в тех случаях, когда данный переход программы к следующей МК является безусловным, т.е. не тре бует анализа состояния условий системы поступающих по входу 10. Каждое слово блока 9 памяти адре сов содержит К адресов . составл Яющих первую группу выходов блока 9; К адресов безусловного (.условного) перехода А. и Ag; вторая группа выходов 9 , а также векторы условий {УЛ (i 1 - К) , состав ляющих четвертую группу выходов бло ка 9, и векторы маски условий | (i 1 - К ) (третья группа выходов. Единичные значения разрядов Ki выделяют разряды вектора Щ , которые необходимо сравнивать со знача- 1ШЯМИ шин условий входа 10. Разряды Q , которым в Mj соответствуют О, в сравнении не участвуют. Информация из блока 9 памяти используется только при организации условного перехода к следующей МК программы. В этом случае выбор адреса и A. определяется по состоянию шин условий входа 1р. Ц,ассм6трйм работу устройства по селекции адресов. С выхода регистра 2 на управляющий вход шифратора 7 поступает адре блока памяти АБП Если Agj О, то шифратор 7 закрывается и на его выходах устанавливается код 0...0 Поэтому блоки 3 и 4 переключаются на прием адресов Ag, А из бл ка б памяти. Если Agr, 1, то шифратор 7 открыт и код его выхода опред ляется результатом сравнения в схемах 8. Пусть сравнение происходит в 1 -и схеме 8 (i 1-К). Тогда на выхое шифратора 7 появляется код, равный i , и блоки 3 и 4 переключаются на прием информации по i-му направлению. Тем самым выполняется селекция адресов А, А. -Agn з блока 9 памяти. Рассмотрим, как выбирается на-. правление перехода программы. В каждой схеме 8 значение условий входа 10 сравнивается с одним из векторов У,-,под вектором маски М; . Так как для любой пары направлений перехода в произвольной графе программы существует хотя бы одно общее условие перехода, то совпадение одного из векторов условий У,с состоянием входа 10 может произойти только в одной схеме сравнения 8. Это совпадение и определяет адреса которые должны быть МК tM БП использованы при данном условном переходе к следующей МК прогрс1ммы. Устройство работает следующим образом. В каждом такте работы из блоков 5,6 и 9 памяти по адресам А,(регистр 1) и А+ (регистр 2) одновременно считается следующая информация: из блока 5 памяти - текущая микрокоманда, подлежащая выполнению; из блока б памяти возможны следующие адреса АМЧ A.j , Agp ; из блока 9 памяти набор возможных следующих адресов A|yj, А , АБР , а также векторов условий( У) и маски ( М; . Затем в 8 происходит сравнение набораГу с состоянием условий входа 10 и выбирается направление условного перехода программы ( если Ag на-выходе регистра 2 равен 1) , т.е. с помощью блоков 3 и 4 на входы регистра 1 подается следующий адрес Ащ, а на входе регистра 2 - следующие адреса A+i Agn . В случае, когда переход к следующей МК является безусловным (т.е. Agn О на выходе регистра 2), блоки 3 и 4 принимают информацию с выходов блока б памяти.В конце рабочего такта выбранные адреса , , Agn записываются в адресные регистры 1 и 2. После этого рабочий такт закончен, Дрименение изобретения позволяет расширить область применения устройства. Формула изобретения Устройство микропрограммного управления, содержащее три блока памяти, первый регистр адреса, группу схем сравнения, причем первый, второй выходы первого блока памяти соеднены соответственно с первым, вторым входами каждой схемы сравнения

группы, третий вход каждой схемы сравнения группы соединен с информационным входом устройства, выход второго блока памяти является управляющим выходом устройства, о т л и ,чающееся тем, что, с целью J)acщиpeния области применения, уст-J ройство содержит шифратор, два блока элементов И-ИЛИ, второй регистр адреса, причем третий выход первого блока памяти соединен с первым входом первого блока элементов И-ИЛИ, второй вход первого блока элементов И-ИЛИ соединен с первым выходом третьего блока памяти, четвертый выход первого блока памяти соединен с первым входом второго блока элементов И-ИЛИ, второй вход второго блока элементов И-ИЛИ соединен со вторым выходом третьего блока памяти, третьи входы

первого и второго блоков элементов И-ИЛИ соединены с выходом шифратора, входы первого и второго регистров адреса соединены соответственно с выходами первого и второго блоков элементов И-ИЛИ, выход первого регистра адреса соединен с входом шифратора и с входами первого и третьего блоков памяти, выход второго регистра адреса соединен с входом второго блока памяти, выходы схем сравнения группы соединены с группой входов шифратора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

5 S 437073, кл.ООбР 9/14, 1972.

2.Авторское свидетельство СССР № 583435, кл.йОбР 9/16, 1977 (прототип .

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1134937A1 |

| Устройство микропрограммного управления | 1980 |

|

SU942020A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1111161A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1170457A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1629910A1 |

| Микропрограммное устройство управления с контролем переходов | 1981 |

|

SU985787A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1716512A1 |

| Микропрограммное устройство управ-лЕНия | 1978 |

|

SU807290A1 |

Авторы

Даты

1981-11-15—Публикация

1980-01-10—Подача