условий, второй вход третьего блока элементов ИЛИ соединен с выходом управления приемом кода операций блока памяти микрокоманд, первый вход пер510ГО блока элементов И соединен с вторым выходом регистра логических условий, вход синхронизации которого является вторым входом синхронизации устройства, третий вход синхронизации устройства соединен со входом чтения блока памяти кодов управления адресацией, первьй, второй, тртий и четвертый выходы которого соединены соответственно со вторым входом первого блока элементов И, со вторым входом второго блока 31лементов И, со вторым входом третьего блока элементов И и с первым входом пятого блока элементов И, второй вход которого соединен с выходом регистра адреса, выход пятого блока элментов И через элемент задержки соединен с четвертым входом первого блока элементов ИЛИ, вьпкод управления режимами работы редистра- логических условий блока памяти микрокоманд соединен со входом чтениязаписи регистра логических условий, выход управления маскированием блока памяти микрокоманд соединен с первым входом шестого блока элементов И, выход которого соединен с информационным входом регистра логических условий, второй вход шестого блока элементов И соединен с выходом второго блока элементов ИЛИ, выход третьего блока элементов ИЛИ соединен )с управляющим входом мультиплексора и с первым входом второго элемента И, выход которого соединен со входом синхронизации регистра кода операции, второй вход второго элемента И является четвертым входом синхронизации устройства, выход управления приемом логических условий блока памяти микрокоманд соединен через элемент НЕ со вторым входом четвертого блока элементов И, третий вход которого является входом прерываний устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода микропрограмм | 1988 |

|

SU1501067A2 |

| Устройство для контроля хода микропрограмм | 1987 |

|

SU1430959A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

Изобретение относится к вычислителной технике, в частности к управляющим устройствам, основанным на принципе микропрограммного управления, и может быть использовано в процессоpax цифровых вычислительных систем и в системах контроля и автоматического проектирования для проверки работоспособности и отладки в реальном масштабе времени аппаратуры и программного обеспечения микропроцессорных устройств.

Известно микропрограммное устройство управления, содержащее два запоминающих блока, два регистра адреса, два блока проверки условий, элемент И, элемент запрета и группу элементов И il.

Недостатка ш данного устройства являются ограниченные возможности ад ресации микропрограмм обработки прерываний и невозможность перехода по коду операций. Недостаток обусловлен тем, что коды всех адресов микрокоманд некоторой микропрограммы об1эаботки прерывания имеют нули в тех же разрядах, что и в разрядах адреса возврата в основную микропрограмму, записанного в первьй регистр адреса. В СВЯ31} с этим количество микрокоманд микропрограммы обработки прерывания ограничено числом ненулевых разрядов кода адреса возврата.

Недостатком является также наличие только микрокомандного уровня управления в устройстве, в то время как в современных цифровых системах может присутствовать и командный уровень.

Кроме того, устройству присуща сложность модификации микропрограммного обеспечения на этапе его проектирования и сопровождения, что связано с наличием двух запоминающих блоков, в которых хранятся микрокоманды. Так, например, вставка или удаление одной микрокоманды приводит либо к появлению дополнительной пустой микрокоманды и, следовательно, к понижению быстродействия устройства, либо, когда последнее не допустимо, к перераспределению микрокоманд в запоминающих блоках и изменению их адресных частей, начиная с места изменения.

Известно также устройство микропрограммного управления, содержащее шифратор, дешифратор, регистры адреса, прерываний, дополнительный регистр адреса, коммутатор, блок элементов ИЛИ, элемент НЕ и элемент И с соответствующими связями 2J ,

Недостатками устройства являются ограниченные возможности организации ьетвлений по логическим условиям, возможна лишь модификация по ИЛИ нулевых разрядов кодов адреса, вырабатываемых шифратором, отсутствие возможности перехода по коду операций, являющееся следствием отсутствия командного уровня управления, ограниченная область использования.

Недостаток обусловлен тем, что любое изменение набора выполняемых микрокоманд связано с существенной переработкой всего устройства, в частности его основных блоков: шифратора, обеспечивающего выработку адреса следующей микрокоманды,и дешифратора, формирующего микрокоманду

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее блок памяти микрокоманд, регистр адреса, регистр кода операций, мультиплексор, э лемент И, блоки элементов И и ИЛИ, причем первый вход блока памяти микрокоманд соединен с выходом регистра адреса, подключенного своим первым входом к выходу первого блока элементов ИЛИ, первый, второй и третий входы которого соединены с вькодами соответственно первого, второго и третьего блоков элементов И, перйый вход второго блока элементов И соединен с выходом регистра кода операц, подключенного первым входом к выходу мультиплексора, соединенного своими первым и вторым, входами со- ответственно со вторым входом блока памяти микрокоманд и с входом приема кода операций устройства, битовый и .векторный входы логических условий которого подключены соответственно к первым входам первого элемента И и четвертого блока элементов И, вькоды которых соединены соответственно

со вторым и первым входами второго блока элементов ИЛИ, подключенного своим третьим входом к входу битовых логических условий устройства,два 5 управляющих входа которого соединены со вторым входом регистра адреса и со вторым входом блока памяти микрокоманд, первый выход которого является выходом устройства, а третий соединен с первым входом третьего блока элементов И L2J.

В известном устройстве ограничены возможности организации условных переходов в микропрограммах. В частности, переход по входному логическому условию возможен лишь при входе в микропрограмму вьшолнения операции по коду этой операции, причем изменяются как старшие разряды регистра адреса, определяемые кодом логических условий, так и остальные разряды того же регистра, определяемые кодом операции.-В то же время при микропрограммном выполнении 5 некоторых операций необходимо выполнять несколько независимых от кода операций условных переходов.

При условном переходе по коду операции, записанному предварительно в Q соответствующий регистр, происходит переход по всем разрядам кода операций, что может привести к существенному увеличению объема микропрограммной памяти по сравнению с последо-г вательным переходом по отдельным полям кода операций. Так, например, код операции может включать попе формата операций (команды), одно или два поля типа адресации операндов, поле указания разрядности операндов н др. Если при этом микропрограмма выполняет последовательно сначала вычисление адресов операндов, затем считывание операндов из оперативной памяти и только затем собственно операцию над операндами то переход по всему коду операции приведет к тому что ячеекJ где п , m - соответственнп числп рязрядов в коде ппеояции и поле типа адресации, блока памяти микрокоманд будут заняты операционно ничего невьтолняющими микрокомандами.

Недостатком устройства является также отсутствие возможности прерывания вьтолняемой микроп}эограммы по запроса от внешних устройств некоторой вычислительной системы, включающей также и рассматриваемое устройство, и продолжение указанной микропрограммы после окончаник обраб отки пр е рыв ани я. Недостатком является также .отсут«ствие возможности настройки устройст ва на конкретное применеииеу в резуль тате которого может потребоваться изменение параметров функций адресации реализуемых устройством, или самих функцийе Гак в некоторых случаях для удобства микропрограммирования может потребоваться изменение, номеров модифицируемых разрядов адреса следующей микрокоманды при переходе по коду операций и (ИЛИ) по входному логи ческому условию. Целью изобретения является расшиpeiffle фугкционапьных возможностей : за счет осуществления независимых ус ловньрс переходов в микропрограмме и реализации запросов на прерывания. Поставленная цель достигается тем что микропрограммное устройство уп равления, содержащее блок памяти мик рокоманд, регистр адреса, регистр ко да операций, гультиплексор5 первый элемент И, первьй, второй, третий и четвертьй блоки элементов первьсД и второй блоки элементов ИЛИ, причем вькоды кода опера1дий блока па. мяти микрокоманд являются управляющими выходами устройства, вход управления обращением устройства соед ней- со входом чтения блока памяти микрокоманда выход кода адреса возврата которого соединен с первым информационньм входом мультиплексора, второй информациоиньй вход которого соединен со входом кода команды устройства, выход кода безусловного перехода блока памяти микрокоманд соединен с первым входом третьего блока элементов И, выход управ-пения приемом логических условий блока памяти микрокоманд соединен с первым входом первого элемента И, второй вход которого соединен с первым вхо дом второго блока элементов ЙЖ и является входом бита логического ус ловия устройства, первый вход синхронизации устройства соединен со входом записи регистра адреса, инфор ма1даонный вход которого соединен с выходом первого блока элементов ИЛИ первый вход которого соединен с вых дом первого блока элементов И, второй вход первого блока элементов liJlH соединен с выходом второго блока элементов Mj первьпй вход которого соединен с вь ходом peгиcтpJ кода операций, информационный вход которого соединен с выходом мультиплексора, третий вход первого блока элементов ИЛИ соединен с вькодом третьего блока элементов И, выход первого элемента И соединен со вторым входом второго блока элементов ИЛИ, третий вход которого соединен с выходом четвертого блока элементов И, первый вход которого является входом вектора логических условий устройства, ВЬЕХОД регистра адреса соединен с адресным входом блока памяти микрокоманд дополнительно введены блок памяти кодов управления адресацией, третий блок элементов ИЛИ, регистр логических условий, второй элемент И,, элемент НЕ, пятый и шестой блоки элементов И и элемент задержки, причем, выход кода функции выбора следующего адреса блока памяти микрокоманд соединен с первым адресным входом блока памяти кодов управления адресацией, второй адресный вход которого соединен с первым вх-одом третьего блока элементов ИЛИ и с первым выходом регистра логических условий, второй вход третьего блока элементов ИЛИ соединен с выходом управления приемом кода операции блока памяти микрокоманд,, первьй вход первого блока элементов И соединен с вторым вь ходом регистра логических условий вход сипхронизации которого является вторым входом синхронизации устройства,, третий вход синхронизации устройства со входом чтения блока памяти кодов управления адресацией, первый, второй, третий и четвертый выходы которого соединены соответственно с вторым входом первого блока элементов И со вторым входом в .-орого блока элементов И, со вторым входом третьего блока элементов И и с первым входом пятого блока элементов И; второй вход которого соединен с выходом регистра адреса, выход пятого блока элементов И через элемент задержки соединен с четвертым входом первого блока элементов ИЛИ, выход управления режимами работы ретистра логических условий блока памяти микрокоманд соединен со входом чтениязаписи регистра логическ -гх условий, выход управления маскированием блока памяти микрокоманд соедир1ен с первьп-t

входом шестого блока элементов И, выход которого соединен с информационным входом регистра логических условий, второй вход шестого блока элементов И соединен с выходом второго 5 блока элементов ИЛИ, выход третьего блока элементов ИЛИ соединен с управляющим входом мультиплексора и с первым входом второго элемента И, выход которого соединен со входом синхрони-ю зации регистра кода операции, второй вход второго элемента -И является четвертым входом синхронизации устройства, выход управления приемом логических условий блока памяти микроко- 15 манд соединен через элемент НЕ со вторым входом четвертого блока элементов И, третий вход которого является входом прерываний устройства.

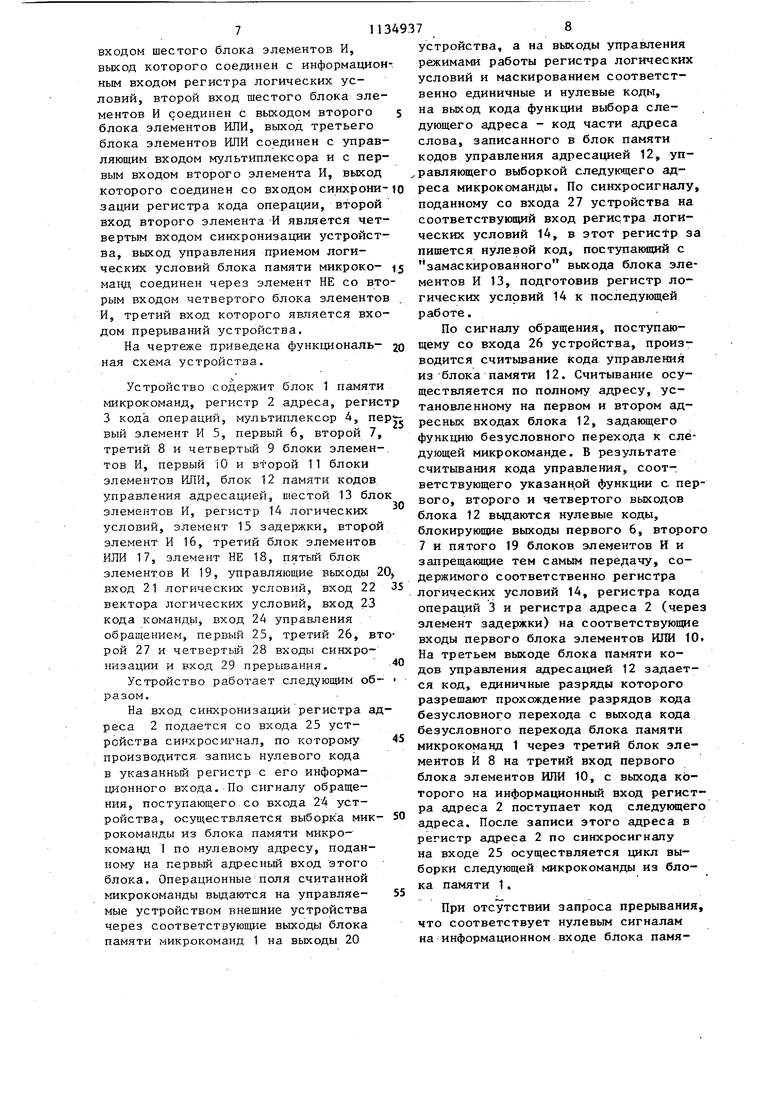

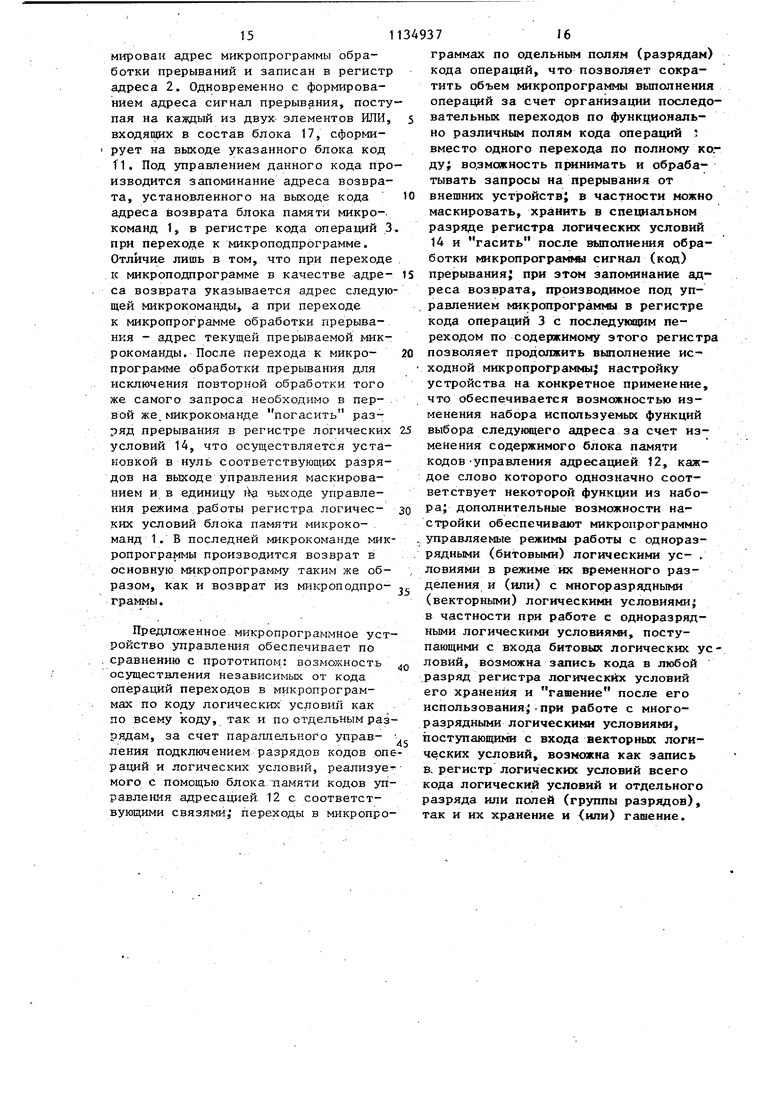

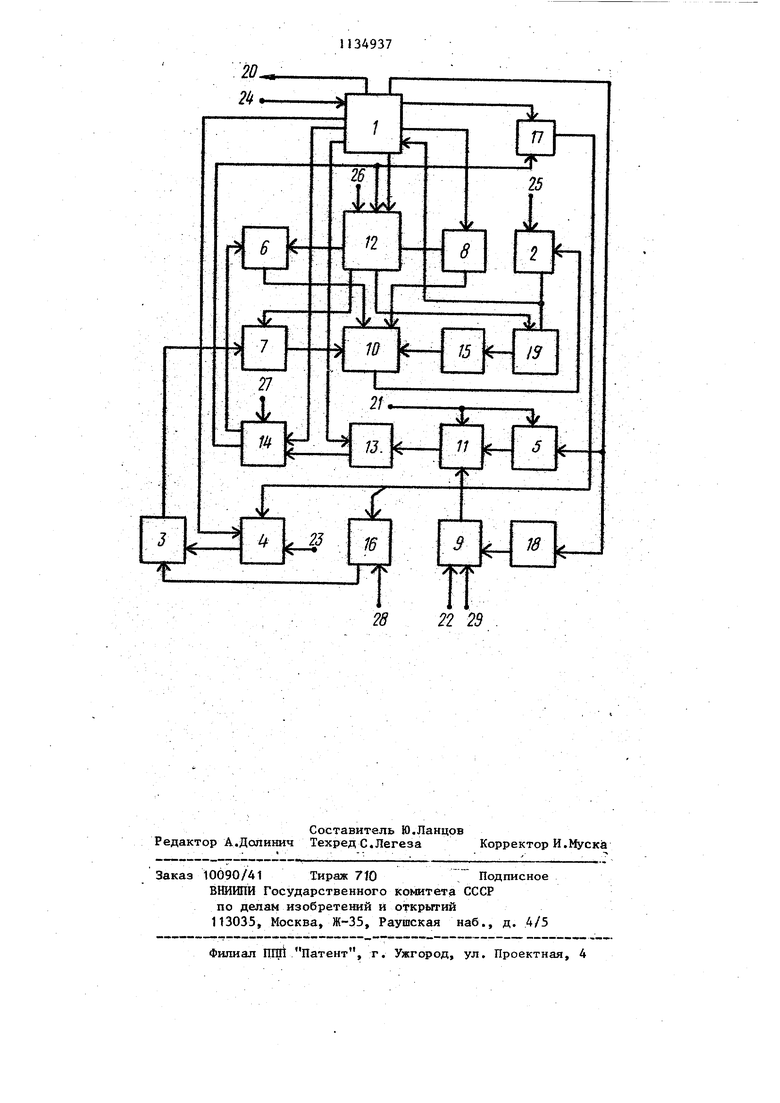

На чертеже приведена функциональ- 20 ная схема устройства.

Устройство содержит блок 1 памяти шкpoкoмaнд, регистр 2 адреса, регистр 3 кода операций, мультиплексор 4, пер; вый элемент И 5, первый 6, второй 7, третий 8 и четвертый 9 блоки элемен-. тон И, первый 10 и второй 11 блоки элементов ИЛИ, блок 12 памяти кодов, управления адресацией, шестой 13 блок элементов И, регистр 14 логических условий, элемент 15 задержки, второй элемент И 16, третий блок элементов ИЖ 17, элемент НЕ 18, пятый блок элементов И 19, управляющие выходы 20, вход 21 логических условий, вход 22 35 вектора логических условий, вход 23 кода команды, вход 24 управления обращением, первый 25, третий 26, второй 27 и четвертый 28 входы синхронизации и вход 29 прерывания. -О

Устройство работает следующим об- разом.

На вход синхронизаиуий регистра адреса 2 подается со входа 25 устройства синхросигнал, по которому 45 производится запись нулевого кода в указанньш регистр с его информационного входа. По сигналу обращения, поступающего со входа 24 устройства, осуЕ ествляется выборка мик- 50 рокоманды из блока памяти микрокоманд 1 по нулевому адресу, поданному на первый адресный вход этого блока. Операционные поля считанной микрокоманды выдаются на управляе- 55 мые устройством внешние устройства через соответствующие выходы блока памяти микрокоманд 1 на выходы 20

устройства, а на выходы управления режимами работы регистра логических условий и маскированием соответственно единичные и нулевые коды, на выход кода функции выбора следующего адреса - код части адреса слова, записанного в блок памяти кодов управления адресацией 12, уп равляющего выборкой следующего адреса микрокоманды. По синхросигналу, поданному со входа 27 устройства на соответствующий вход регистра логических условий 14, в этот регистр за пишется нулевой код, поступающий с замаскированного выхода блока элементов И 13, подготовив регистр логических условий 14 к последующей работе,

По сигналу обращения, поступающему со входа 26 устройства, производится считывание кода управления из блока памяти 12. Считывание осуществляется по полному адресу, установленному на первом и втором адресных входах блока 12, задакнцего функцию безусловного перехода к следующей микрокоманде. В результате считывания кода управления, соответствующего указанной функции с первого, второго и четвертого выходов блока 12 В1адаются нулевые коды, блокирующие выходы первого 6, второг 7 и пятого 19 блоков элементов И и запрещающие тем самым передачу, содержимого соответственно регистра логических условий 14, регистра кода операций 3 и регистра адреса 2 (чере элемент задержки) на соответствующие входы первого блока элементов ИЛИ 10 На третьем выходе блока памяти кодов управления сщресадией 12 задается код, единичные разряды которого разрешают прохождение разрядов кода безусловного перехода с выхода кода безусловного перехода блока памяти микрокоманд 1 через третий блок элементов И 8 на третий вход первого блока элементов ИЛИ 10, с выхода которого на информационный вход регистра адреса 2 поступает код следукнцего адреса. После записи этого адреса в регистр адреса 2 по синхросигналу на входе 25 осуществляется цикл выборки следующей микрокоманда. из блока памяти 1,

При отсутствии запроса прерывания, что соответствует нулевым сигналам на информационном входе блока памя9113ти кодов управления aRpecavftefi 12, из этого блока по сигналу обращения считывается соответствующий код управления. В результате на первом и втором выходах блока памяти кодов управления адресацией 12 устанавливаются нули, на его третьем выходе единицы, а на четвертом - код, единичные разряды которого выделяют те разряды содержимого регистра адреса 2, относительно которых производится безусловный переход. Таким образом, содержимое регистр логических условий 14 и регистра кода операций 3 не может быть передано Соответственно через первый 6 и второй 7 блоки элементов И на первый и второй входы первся-о блока элементов ШШ 1р. Код безусловного перехода через третий блок элементов И 8 передается на третий вход первого бло ка элементов ИЛИ 10. Содержимое реГ1к:тра адреса передаются на второй вход пятого блока элементов И 19, с выхода которого вьщеленные кодом управления разряды текущего адреса пос тупают через элемент задержки 15 на четвертый вход первого блока элементов ИЛИ 10, на выходе которого форми руется код следу«ицего адреса. По син хросигналу на соответствующем входе регистра йрреса 2 производится запись сформированного следующего адре са микрокоманды с информационного входа этого регистра. Вход в микропрограмму выполнения некоторой операции производится при считывании микрокоманды из блока памяти микрокоманд 1- по сигналу обращения, поступающего на вход 24 уст ройства. При этом на выход управлени приемом кода операций блока 1 вьщает ся двухбитовый код 01, первый бит которого предназначен для управления мультиплексором 4, а второй - для управления записью в регистр кода операций 3. Указанный код через третий блок элементов ИЛИ 17 подается первым битом на управлякяций вход мультиплексора 4, а вторьм битом на первый вход второго элемента И 16 При нулевом сигнале на своем управляющем входе мультиплексор 4 передает на свой выход и далее на информационный вход регистра кода опера191й 3 информацию со входа кода кома ды 23 устройства, подключенного к второму информационному входу мульти плексора. Сигнал записи, поступивший со входа 28 устройства, пройдя через открытый второй элемент И 16 на соответствующий вход регистра кода операций 3, произведет запись кода команда в/указанный регистр. В случае если переход по всему коду команды или его части необходимо выполнить сразу после приема этого кода в регистр операций 3, то на выход кода функтщи выбора следующего адреса блока памяти микрокоманд 1 выдается соответствукяций код функции перехода к следующей микрокоманде по коду команды (по всему коду или по его части) . В случае, если выполнение операции не требует дополнительного ветвле1шя по логическим условиям, то при считывании кода управления иэ блока памяти кодов управления адресацией 12 с второго выхода последнего на первый вход первого блока элементов И 6 будут переданы нули. В противном случае из блока памяти кодов управления адресацией 12 будет считан код управления, по которому на первый выход считывается ненулевой код. Так как код команды имеет, как правило, меньшую разрядность, чем полный код адреса микрокоманды,. функ1щя перехода по коду команды должна обеспечивать возможность безусловного хранения и (или) задания дополнительных разрядов адреса. В связи с этим в общем случае при считывании кода управления из блока памяти 12 на выходе с первого по четвертый выкаются некоторые коды, единичные разряды которых обеспечивают прохождение через открытые элементы И блоков элементов И6, 7, 8, 19 на их выходы разрядов соответственно регистра логических условий 14, регистра кода операций 3, безусловного перехода, переданного с. выхода кода безусловного перехода блока памяти микрокоманд 1, и регистра адреса 2. С выходов блоков элементов И 6, 7, 8, 19 эти разряды передаются соответственно на многоразрядные первый, второй, третий, а через элемент задержки 15 - на четвертьш входы первого блока элементов ИЛИ 10, на выходе которого формируется следующий адрес, записываемый в регистр адреса 2 по сигналу на его входе, записи, подаваемого со входа синхронизагщи 25 устройства. В любой микрокоманде могут быть заданы режимы работы с логическими условиями. Рассмотрим эти режимы в предположении, что сигналы запроса прерываний на входе 29 прерывания устройства отсутствуют. При считывании микрокоманды наличие единичного сигнала на выходе управления рриемом логических условий блока памяти микрокоманд 1 соответствует работе с логическими условиями (имеющим место на входе 21 устройства). В этом случае логическое условие со входа 21 логических условий устройст ва поступает через открытый первый элемент И 5 на второй вход второго блока элементов ИЛИ 11, на первый вк которого логическое условие поступает непосредственно со входом 21 логических условий устройства. Одновре менно сигнал с выхода управления при емом логических условий блока памяти микрокоманд 1, пройдя через элемент НЕ 18 ла второй вход четвертого блока элементов И 9, блокирует поступле ние на третий вход второго блока эле ментов ИЛИ 11, кода со входа 22 вектора логических условий устройства. Во втором блоке элементов ИЛИ 11 производится поразрядная дизъюнкция каждого разряда кода на третьем вход с одноразрядным кодом на втором вход и дизъюнкция одноразрядньос кодов на втором и первом входазс. В результате на второй вход шестого блока элементов И 13 поступит многоразрядный код, разрядность которого на единицу больше разрядности кода на третьем входе второго блока элементов ИЛИ 11. При этом указанный код на входе блока 13 будет иметь во всех разрядах либо ед ницы, либо нули, в зависимости от то го, какое значение имел код логического условия, принятый со входа 21 устройства. Если при считывании микрокоманды хотя бы один разряд многоразрядного выхода управления маскированием блока памяти микрокоманд 1 установлен в единицу, то соответствующий разряд поступает вместе с дру гимн разрядами кода, на второй информационный вход регистра логических условий 14. При единичном управляющем сигнале разрешения записи в соответствующий разряд на многоразрядном выходе управления режимами работы регистра логических условий блока памяти микрокоманд 1 по сигналу записи со входа 27 устройства произойдет запись л.огического условия в соответствующий разряд регистра логических условий 14. При этом при нулевых управляющих сигналах разрешения записи в другие разряды регистра 14 на выходе управления режимами работы регистра логических условий блока памяти микрокоманд 1 содержимое этих разрядов не изменится. Необходимость указать дополнительную возможность одновременно с записью кода логического условия в один из разрядов регистра логических условий 14 обнулять один или несколько разрядов содержащих обработанные логические условия. Для этого достаточно в соответствующие разряды выходов управления режимами работы регистра логических условий и маскирования блока памяти микрокоманд 1 установить соответственно коды нулей и единиц. При наличии на выходе управления приемом логических условий нулевого сигнала, что соответствует работе с векторными логическими условиями, происходит блокировка логического условия, поступающего со входа 21 устройства через второй вход первого элемента И 5 на второй вход второго блока элементов ИЛИ 11. Тот же нулевой сигнал, проходя через элемент НЕ 18, открывает соответствующие элементы И четвертого блока элементов И 9. В результате на третий вход второго блока элементов ИЛИ 11 поступят- код со входа 22 векторных логических условий устройства и бит со входа 29 прерьшания устройства. Так как на втором входе блока 11 находится нуль, то на выход блока 11 поступает код с его третьего входа, дополнительный битом со входа 21 устройства. Полученный объединенный код поступит далее на второй вход блока элементов И 13. Управление режимами записи, гашения, хранения и маскирования указанного кода или его разрядов осуществляются с выходов управления режимами работы регистра логических условий и маскирования блока памяти микрокоманд 1 и аналогичного выше описанному режиму работы с логическими условиями (на входе 21). При необходимости независимого т.кода операций перехода по содеримому всего регистра логических усовий 14 или отдельных его разрядов достаточно, чтобы при считывании кода управления из блока памяти 12, соответствующего функции перехода по логическому условию, на второй выход указанного блока был записан нулевой код, блокирующий передачу всех разрядов с выхода регистра кода операций 3 на второй вход формирующего следующий адрес первый блок элементов ИЛИ 10, Ненулевой код на втором выходе блока памяти 12 позволяет произвести переход одновременно по логическим условиям и отдельным разрядам или всему коду операций. При необходимости перехода к микроподпрограмме на выходе управления приемом кода операции устанавливается код 11, Сигналы, соответствующе коду с этого выхода блока памяти мик рокоманд 1, через третий блок элементов ИЛИ 17 поступают на управляющий вход мультиплексора 4 и на первы вход второго элемента И 16, В резуль ,тате на выходе мультиплексора 4 буде вьщан код адреса возврата, поданный на его первый информационный вход. По синхросигналу с входа 28 устройст ва, прошедшему через открытый второй элемент И 16 на соответствующий вход регистра кода операций 3, код адреса возврата запишется в регистр 3, Описанным вьше способом произойдет пере ход к микроподпрограмме. Для обеспечения хранения адреса возврата при выполнении микроподпрограммы необходимо блокировать прохождение сигна ла по выходу записи регистра 3. Блокировка осуществляется установкой на выходе управления приемом кода операций блока памяти микрокоманд 1 кодов 10 или 00, В последней микрокоманде микроподпрограммы на выход кода функш1И выбора следующего адреса блока памяти, устанавливается код функции условного перехода по содержимому регистра кода операций 4, поступающий на первый адресный вход бл ка памяти кодов управления адресацией 12, выходы которого управляют, как уже было описано, формированием следующего адреса. В результате в регистр адреса 2 запишется код адреса возврата в основную микропрограмм Обработка запросов прерываний осу ществляется в режиме обработки век- торных логических условий. На отдельных линиях входа вектора логических условий 22 устройству внешнее устройство, запрашивающее прерывание, устанавливает код (вектор) адреса микропрограммы обработки прерывания. Сигнал запроса, выработанный внешним устройством подается со входа прерывания 29 устройства на третий вход четвертого блока элементов И 9, на первый вход которого поступает векторное логическое условие, содер- жащее код адреса микропрограммы обработки прерывания. Нулевой сигнал с выхода управления приемом логических условий блока памяти NMKPокоманд 1 блокирует прохождение сигнала логического условия со входа 21 устройства через первый элемент И 5 на второй вход второго блока элементов ИЛИ 11 и, пройдя через элемент НЕ 18 на второй вход четвертого блока элементов И 9, разрешает прохождение сигналов с первого и третьего входов блока 9 на его выход. На многоразрядном выходе второго блока элементов ИЛИ 11 будут находиться сигналы векторного логического условия прерывания и дополнительно сигнал логического условия со входа 21 устройства. При отсутствии маскирования на выходе управления маскированием блока памяти микрокоманд 1 прерывания и адрес мик ропрограммь обработки прерывания поступят через шестой блок элементов И 13 на информационный вход регистра логических условий 14. При разрешающих единичных сигналах на выходе управления режимами работы регистра логических условий блока памяти микрокоманд 1 и при поступлении синхро сигнала со входа 27 устройства произойдет запись сигналов (кодов) прерывания и адреса микропрограммы обработки прерывания в регистр 14 логических условий. С первого информационного выхода указанного регистра сигнал прерывания поступает на второй адресный вход блока памяти кодов управления адресацией 12 и одновременно на первый вход третьего блока элементов ИЛИ 17. При поступлении разрешающего сигнала со входа 26 устройства на вход чтения блока памяти 12 из последнего будет считан код управления, соответствующий функции перехода по тем разрядам регистра логических условий 14, в коЁорых записан адрес микропрогракв-ш обработки прерывания. В результате описанных уже действий будет сформирован адрес микропрограммы обработки прерываний и записан в регистр адреса 2. Одновременно с формированием адреса сигнал прерывания, посту пая на каждый из двух элементов ИЛИ, входядах в состав блока 17, сформирует на вьшоде указанного блока код 11. Под управлением данного кода про изводится запоминание адреса возврата, установленного на выходе кода адреса возврата блока памяти микро-, команд 1, в регистре кода операций 3 при переходе к микроподпрограммё. Отличие лишь в том, что при переходе к микроподпрограмме в качестве адреса возврата указывается адрес следую щей микрокоманды, а при переходе к микропрограмме обработки прерывания - адрес текущей прерываемой микрокоманды. После перехода к микропрограмме обработки прерывания для исключения повторной обработки того же самого запроса необходимо в первой же.микрокоманде погасить разряд прерывания в регистре логических условий 14, что осуществляется установкой в нуль соответствующих разрядов на выходе управления маскированием и. в единицу Ц выходе управления режима работы регистра логических условий блока памяти микрокоманд 1 . В последней микрокоманде мик ропрограммы производится возврат в основную микропрограмму таким же образом, как и возврат из микроподпрограммы. Предложенное микропрограммное уст ройство управления обеспечивает по сравнению с прототипом: возмохсность осуществления независимых от кода операций переходов в микропрограммах по коду логических условий как по всему коду, так и по отдельным раз рядам, за счет параллельного управления подключением разрядов кодов оп раций и логических условий, реализуе мого с помощью блока памяти кодов уп равления адресацией 12 с соответствующими связями, переходы в микропро граммах по сдельным полям (разрядам) кода операций, что позволяет сократить объем микропрограммы вьшолнения операций за счет организации последовательных перекодов по функционально различным полям кода операций вместо одного перехода по полному ког ду; во.змажность П1жнимать и обрабатывать запросы на прерывания от внешних устройств; в частности можно маскировать, хранить в специальном разряде регистра логических условий 14 и гасить после выполнения обработки микропрограммы сигнал (код) прерывания; при этом запоминание адреса возврата, производимое под управлением микропрограмьбл в регистре кода операций 3 с последующим переходом по содержимому этого регистра позволяет продолжить выполнение исходной микропрограммы; настройку устройства на конкретное применение, что обеспечивается возможностью изменения набора используемых функций выбора следующего адреса за счет изменения содержимого блока памяти кодов-управления адресацией 12, каждое слово которого однозначно соответствует некоторой функции из набора; дополнительные возможности настройки обеспечивают микропрограммно управляемые режимы работы с одноразрядными (битовыми) логическими ус- , ловиями в режиме их временного разделения и (нпи) с многоразрядными (векторными) логическими условиями; в частности при работе с одноразрядными логическими условияьм, поступающими с входа битовых логических условий, возможна запись кода в любой разряд регистра логических условий его хранения и гашение после его использования;- при работе с многоразрядными логическими условиями, пocтyпaющи iи с входа векторных логических условий, возможна как запись в. регистр логических условий всего кода логический условий и отдельного разряда или полей (группы разрядов), так и их хранение и или) гашение.

Т П

22 23 .

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| З, Авторское свидетельство СССР № 881748, кл.О 06 F 9/22, 1980 (прототип). | |||

Авторы

Даты

1985-01-15—Публикация

1983-08-30—Подача