1

Изобретение относится к вычислительной технике и предназначено для работы в центральном процессоре быстродействующих ЭВМ с уровняNM совмещения выполнения команд (п конечное число уровней совмещения выполнения команд).

Известно устройство мг кропрограммного управления, содержащее группы элементов И/ ИЛИ, НЕ, блоки основной памяти микропрограмм. Из блоков основной и дополнительной глмяти микропрограмм через элементы И, ИЛИ микрокоманда выбираетсяна обвдай регистр микрокоманд. Увеличение производительности достигается путем совмещенного выполнения последней микрокоманды из последовательности микрокоманд, необходимой для выполнения системной команды, с обращением к первой микрокоманде последовательности . следующей системной команды 1 .

Недостатком такого устройства является то, что оно обеспечивает только двухуровневое совмещение.Это не позволяет достигнуть высокой скорости обработки команд, требуемой в больших вычислительных системах.

Наиболее близким к предлагаемому является устройство микропрограм-

много управления, предназначенное для работы в составе процессора с тремя уровнями совмещения команд.Это устройство;содержит группы элементов И, ИЛИ, НЕ, блоки основной и дополнительной памяти.микропрограмм, первый и второй регистры адреса, регистры кода операции первой команды и второй команды, регистры

10 основной и дополнительной микрокоманд и узел модификации адреса микрокоманды. Из двух блоков основной и дополнительной памяти микропрогралпл синхронно звыбираются две микро15команды. Действия, зависящие от кода операции системной команды, управляются основной микрокомандой, а действия, зависящие от такта выполнения команды, управляются микрокомандой, выбираемой из дополнительной памяти микропрограмм. Система адресации микрокоманд обеспечивает обращение к основной или дополнительной памяти микропрограмм без потери времени 2.

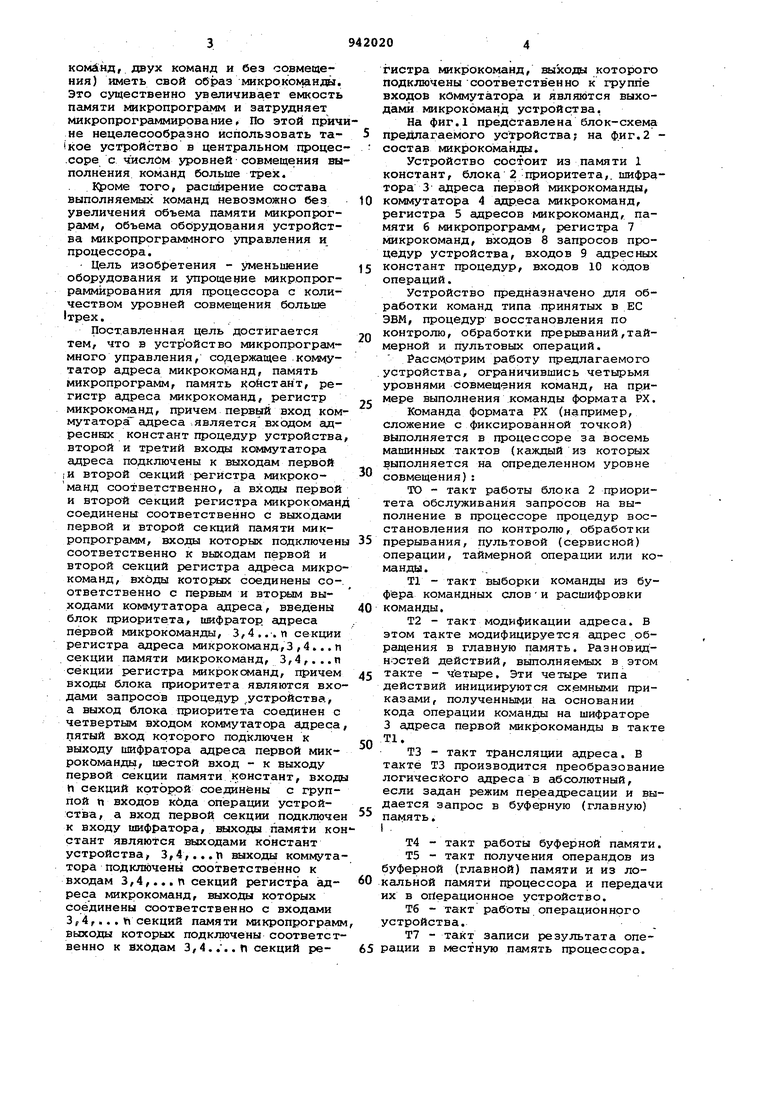

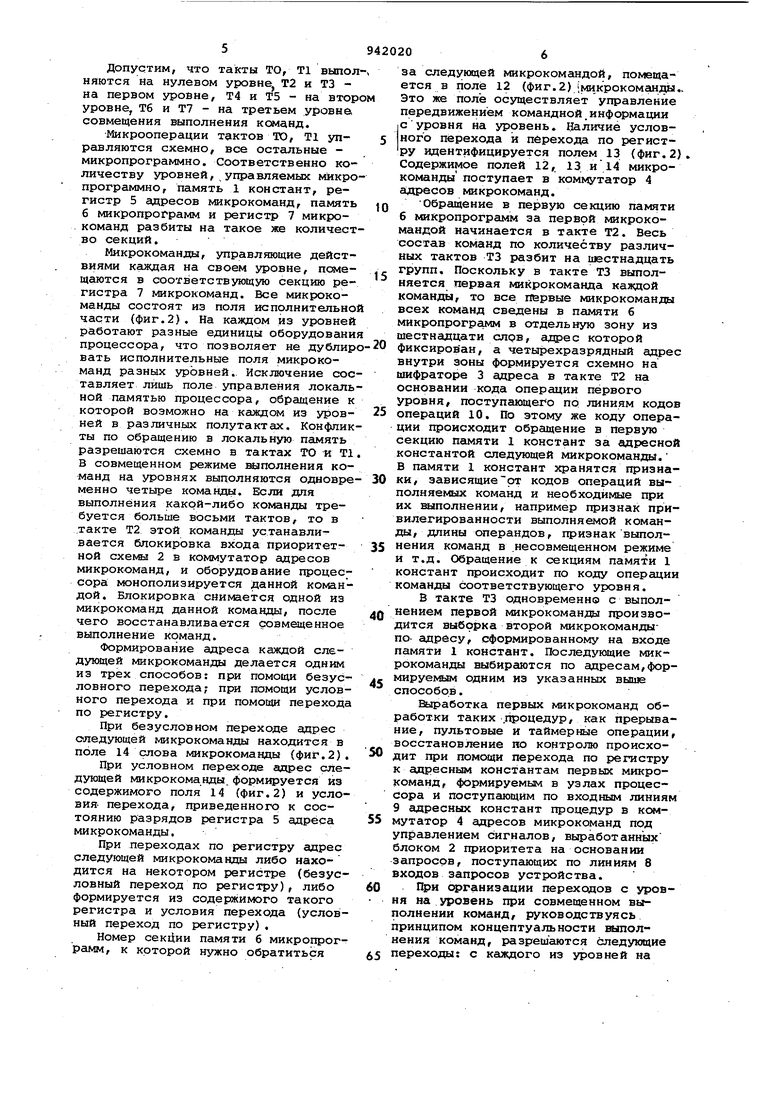

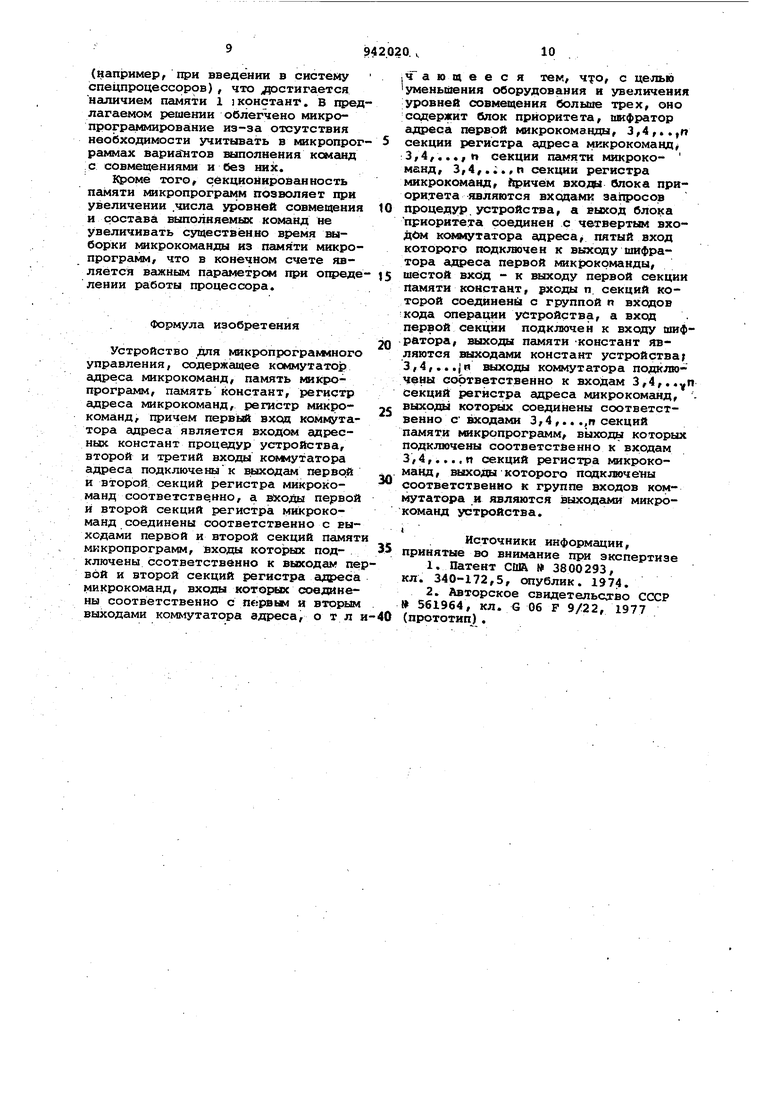

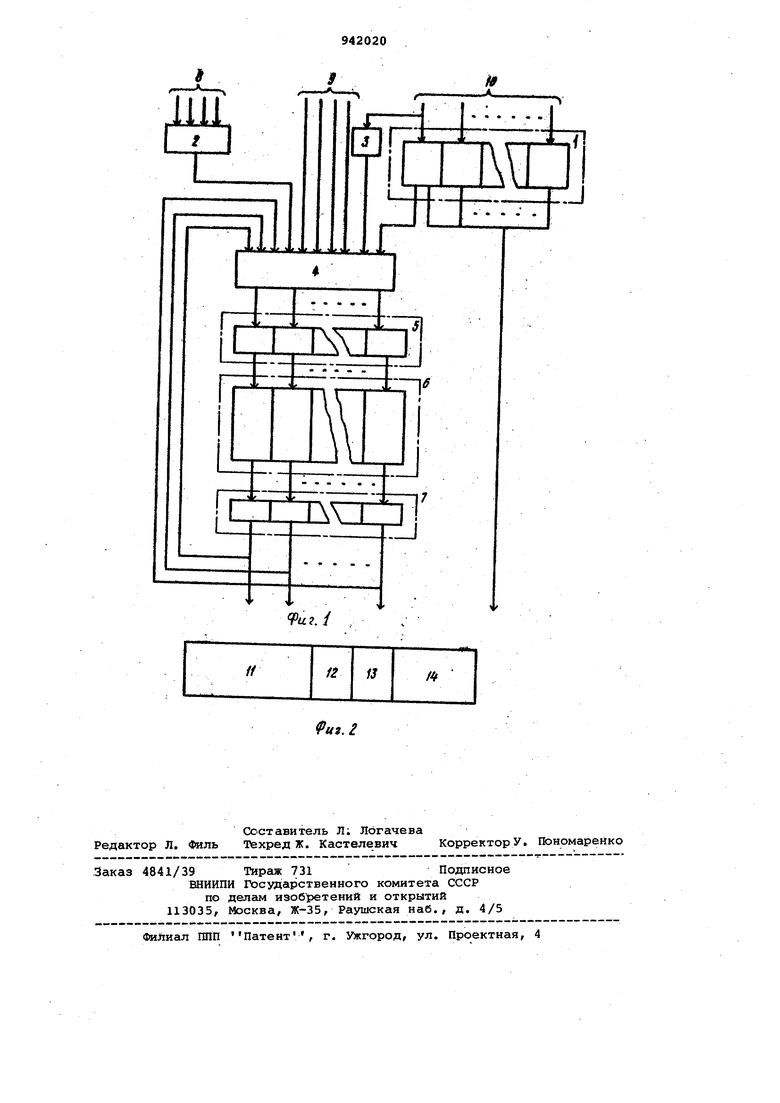

К недостаткам известного устройства относится то, -что в дополнительной памяти микропрограмм необ30 °яимо для каждого случая выполнения команд (с совмещением выполнения трех комйнд, двух команд и без совмещения) иметь свой образ микрокоманда. Это существенно увеличивает емкость памяти микропрограмм и затрудняет микропрограммирование По этой прич не нецелесообразно использовать та(кое устройство в центральном процес .соре с числом уровнейсовмещения вы полнения команд больше трех, KipoMe того, расширение состава выполняемых команд невозможно без увеличения объема памяти микропрограмм, объема оборудования устройства микропрограммного управления и процессора. Цель изоб }етения - уменьшение оборудования и упрощение микропрограммирования для процессора с количеством уровней совмещения больше трех. Поставленная цель достигается тем, что в устройство микропрограммного управления, содержащее коммутатор адреса микрокоманд, память микропрограмм, память койстант, регистр адреса микрокоманд, регистр микроком 1НД, причем первый вход ком мутатора адреса .является входом адpecHKtx констант процедур устройства второй и третий входы коммутатора адреса подключены к выходам первой |И второй секций регистра микрокоманд соответственно, а входы первой и второй секций регистра микрокоман соединены соответственно с выходами первой и второй секций памяти микропрограмм, входы которых подключен соответственно к выходам первой и второй секций регистра адреса микро команд, входы которых соединены соответственно с первым и вторым выходами коммутатора адреса, введены блок приоритета, шифратор, адреса первой микрокоманды, 3,4,.-. п секции регистра адреса микрокоманд,3,4...п .секции памяти микрокоманд, 3,4,...п секции регистра микрокоманд, причем входы блока приоритета являются вхо дами запросов процедур .устройства, а выход блока приоритета соединен с четвертым входом коммутатора адреса пятый вход которого подключен к выходу шифратора адреса первой микрокоманды, шэстой вход - к выходу первой секции памяти констант, вход 1 секций которой соединены с группой п входов кбда операции устройст1ва, а вход первой секции подключе к входу шифратора, выходы памяти ко стант являются выходами констант устройства, 3,4,...п выходы коммута тора подключены соответственнс5 к входам 3,4,...п секций регистра адреса микрокоманд, выходы которых соединены соответственно с входами 3,4,.. . i секций памяти микропрограм выходы которых подключены соответст венно к входам 3, 4.... п секций регистра микрокоманд, выходы которого подключены соответственно к группе входов коммутатора и являются выходами микрокоманд устройства. На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 состав микрокоманды. Устройство состоит из памяти 1 констант, блока 2;приоритета,, шифратора 3 адреса первой микрокоманды, коммутатора 4 адр.еса микрокоманд, регистра 5 адресов микрокоманд, памяти 6 микропрограмм, регистра 7 лОТкрокоманд, входов 8 запросов процедур устройства, входов 9 адресных констант процедур, входов 10 кодов операций. Устройство предназначено для обработки команд типа принятых в ЕС ЭВМ, процедур восстановления по контролю, обработки прерываний,таймерной и пультовых операций. Рассмотрим работу предлагаемого устройства, ограничившись четырьмя уровнями Совмещения команд, на примере выполнения команды формата РХ. Команда формата РХ (например, сложение с фиксированной точкой) выполняется в процессоре за восемь машинных тактов (каждый из которых выполняется на определенном уровне совмещения): ТО - такт работы блока 2 приоритета обслуживания запросов на выполнение в процессоре процедур восстановления по контролю, обработки прерывания, пультовой (сервисной) операции, таймерной операции или команды. Т1 - такт выборки команды из буфера командных слов - и расшифровки команды. Т2 - такт модификации адреса. В этом такте модифицируется адрес обреицения в главную память. Разновидностей действий, вьшолняемых в этом такте - четыре. Эти четыре типа действий инициируются схемными приказами, полученными на основании кода операции команды на шифраторе 3 адреса первой микрокоманды в такте Т1. ТЗ - такт трансляции адреса. В такте ТЗ производится преобразование логического адреса в абсолютный, если задан режим переадресации и выдается запрос в буферную (главную) память. i . Т4 - такт работы буферной памяти. Т5 - такт получения операндов из буферной (главной) памяти и из локальной памяти процессора и передачи их в операционное устройство. Т6 - такт работы операционного устройства. Т7 - такт записи результата операции в местную память процессора. Допустим, что такты ТО, Т1 вьтол няются йа нулевом уровне Т2 и ТЗ на первом уровне, Т4 и Т5 - на втор уровне, Тб и Т7 - на третьем уровне совмещения выполнения команд. Микрооперации тактов ТО, Т1 управляются схемно, все остальные микропрограммно. Соответственно количеству уровней, управляемых микро программно, память 1 констант, регистр 5 адресов микрокоманд, память б микропрограмм и регистр 7 микрокоманд разбиты на такое же количест во секций. Микрокоманды, управляющие действиями каждая на своем уровне, петлещаются в соответствующую секцию регистра 7 микрокоманд. Все микрокоманды состоят из поля испрлнительно части (фиг.2). На каждом из уровней работают разные единицы оборудовани процессора, что позволяет не дублир вать исполнительные поля микрокоманд разных уровней.. Исключение сос тавляет лишь поле управления локаль ной памятью процессора, обращение к которой возможно на каждом из уровней в различных полутактах. Конфлик ты по обращению в локальную память разрешаются схемно в тактах ТО и Т1 В совмещенном режиме ш полнения команд на уровнях выполняются одновре менно четыре команды. Если для выполнения какой-либо команды требуется больше восьми тактов, то в такте Т2 этой команды устанавливается блокировка входа приоритетной схемы 2 в коммутатор адресов микрокоманд, и оборудование процессора монополизируется данной командой. Блокировка снимается одной из микрокоманд данной команды, после чего восстанавливается совмещенное выполнение команд. Формирование адреса каждой следующей микрокоманды делается одним из трех способов: при помощи безусловного перехода; при помощи условного перехода и при помощи перехода по регистру. При безусловном переходе адрес следующей микрокоманды находится в поле 14 слова микрокоманды (фиг.2). При условном переходе адрес следующей микрокоманды.формируется из содержимого поля 14 (фиг.2) и условия- перехода, приведенного к состоянию разрядов регистра 5 адреса микрокоманды. При переходах по регистру адрес следующей микрокоманды либо находится на некотором регистре (безусловный переход по регистру), либо формируется из содержимого такого регистра и условия перехода (условный переход по регистру). Номер сек14ии памяти 6 микропрограмм, к которой нужно обратиться за следующей микрокомандой, помещается в поле 12 (фиг.2) микрокоманды.. Это же поле осуществляет управление передвижением командной.информации с уровня на уровень. Наличие условного перехода и перехода по регистру идентифицируется полем 13 (фиг.2}. Содержимое полей 12, 13 и 14 микрокоманды поступает в коммутатор 4 адресов микрокоманд. Обращение в первую секцию памяти б микропрограмм за первой микрокомандой начинается в такте Т2. Весь состав команд по количеству различных тактов ТЗ разбит на шестнадцать групп. Поскольку в такте ТЗ выполняется первая микрокоманда каждой команды, то все первые микрокоманды всех команд сведены в памяти б микропрограмм в отдельную зону из шестнадцати слов, адрес которой фиксирован, а четырехразрядный адрес внутри зоны формируется схемно на шифраторе 3 адреса в такте Т2 на основании кода операции первого уровня, поступающего по линиям кодов операций 10. По этому же коду операции происходит обращение в первую секцию памяти 1 констант за адресной константой следующей микрокоманда}. 8памяти 1 констант хранятся признаки, зависящие рт кодов операций выполняег зх команд и необходимые при их выполнении, например признак привилегированности выполняемой команды, длины операндов, признак выполнения команд в .несовмещенном режиме и т.д. Обращение к секциям памяти 1 констант происходит по коду операции команды соответствующего уровня. В такте ТЗ одновременно с выполнением первой микрокоманды производится выборка второй микрокомандыпо адресу, сформированному на входе памяти 1 констант. Последующие микрокоманды выбираются по адресам,формируемым одним из указанных выше способов. Выработка первых микрокоманд обработки таких .процедур, как прерывание, пультовые и таймерные операции, восстановление по контролю происходит при помощи перехода по регистру к адресным константам первых микрокоманд, формируемым в узлах процессора и поступающим по входным линиям 9адресных констант процедур в коммутатор 4 адресов микрокоманд под управлением сигналов, выработанных блоком 2 приоритета на основании запросов, поступающих по линиям 8 входов запросов устройства. При организации переходов с уровня на уровень при совмещенном выполнении команд, руководствуясь принципом концептуальности иьтолнения команд, разрешаются следующие переходы: с каждого из уровней на следующий, предьадущий, на тот же самый и на первый. В частных случая не все,возможные переходы необходимы Например, для случая п 4 оказывает ся необязательным переход с третьего на второй уровень.; В общем случае нет необходимости память б микропрограмм делить на равные по объему секции. В рассматриваемом случае rii:4r например, первая секция микропрограмм вдвое больше второй и треть ей секций. Это относится и к памяти 1 констант и к регистру 7 микрокоманд и к регистру 5 адресов микрокоманд. Таким Образом, предлагаемое техническое решение обеспечивает существенное сокращение требуемого объема памяти микропрограмм по сравнению с прототипом. В связи с тем, что при разделении памяти микропрограмм на секции, каждая из которых управляет действиями, выполняемыми на определенном уровне, исчезает необходимость в дублиров.ании упЕ)авляющих полей в микрокомандах и количес ва самих микрокоманд в зависимости от возможных вариантов совмещений в выполнении операций. Произведем количественную оценку уменьшения объема памяти микропрограмм в сравниваемых вариантах. . Представим весь объем требуемой памяти микропрограмм (V) в виде сумм двух составляющих: части памяти микропрограмм (), управляющей совмещаемыми действиями в процес.соре, объем которой зависит от организации устройства.микропрограммного управления и количества уровней совмещения , и части памяти микропрограмм (Vpons-k ) которая управляет несовмещаемыми действиями и не зависит от количества уровней и структуры устройства микропрограммного управления. V Vvar + (1) Длину одной микрокоманды условно представим в виде г ЕИ + Bq, (2) где ly- суммарная длина полей,определяющих выполняемые по данной микрокоманде действия , в.узлах процессора (исполни тельная часть), величина 2 зависит от организации памяти 1«1кропрограмм и количества уровней совмещения (п) , управляемых микропрограммно 20 - суммарная длина полей, составляющих, в основном, адрес ную часть микрокоманды,независящая от варианта структуры памяти микропрограмм и уровней совмещения. При сравнении двух вариантов организации .устройства микропрограммно го управления (1 - предлагаемое техническое решение, 2 - 2) по требуемому объему памяти микропрограмм исходим из следующих предположений: а)в обоих вариантах микропрограммно управляются одни и те же действия процессора, как совмещаемые,так и несовмещаемые, причем V,gt Vcon9t . б)количество функционально различных микрокоманд, определяющих работу всех узлов процессора, одно н то же (для заданного п) независимо от того, является ли память микропрограмм секционированной по уровням совмещений . или нет, и составляет Q-&CV,., где q. - количество микрокоманд, выполняемых на i-oM уровне; в)длина адресной части микрокоманд одинакова для обоих вариантов гУ 2tW 2с,; (4) г)поскольку Q con9i длина исполнительной части микрокоманд всех уровней для первого, варианта, то (считая, что все Б равны} (JUe.(5) д) поскольку во втором варианте B зависимости от возможных типов совмещенного выполнения операций (0,1п, одновременно выполняемых команд) для каждого из типов должен быть предусмотрен собственный образ микрокоманды для каждого из действий, общее количество микрокоманд для второго варианта равно: ыСЧ nQ . Отсюда v};| Vconst + + а) - Vcotis-t + , + Zq) .nQ(nye) Q ())Вд y -L consV - 1л « « ГГ1/5 / f) n 50nSt ieM- C,) М(Г 4onst «() Для системы команд EC ЭВМ и количества микропрограммно управляемых уровней совмещения численные соотношения между 2j, 2а, 4;onst примерно следующие:/ 2v,:2a 3 : 5(10) 4, Q(2n + Sc,) (11) Подставляяв (9) ,а также соотношения (1C) и (11), получаем , 3,125 (12) Предлагаемое техническое решение является также универсальной структурой (т.е. независимой от числа совмещаемых команд) , способной к расширению состава выполняемых команд

(например, при введении в систему спецпроцессоров), что достигается наличием памяти 1 iконстант. В предлагаемом решении облегчено микропрограк|мирование из-за отсутствия необходимости учитывать в микропрограммах вариа нтов выполнения команд с совмещениями и без них.

Кроме того, сёкционированность памяти микропрограмм позволяет при увеличении .числа уровней совмещения и состава выполняемых команд не увеличивать существенно врем;г выборки микрокоманды из памяти микропрограмм/ что в конечном счете является важным параметром при ощ еделении работы процессора.

Формула изобретения

Устройство для микропрограммного управления, содержащее коммутатор сщреса микрокоманд, память микропрограмм. Петлять констант, регистр адреса микрокоманд, регистр микрокоманд, причем первый вход коммутатора адреса является входом адресных констант процедур устройства, второй и третий входы коммутатора адреса подключенык выходам перво и второй, секций регистра микрокоманд соответственно, а йходы первой и второй секций регистра микрокоманд соединены соответственно с выходами первой и второй секций памяти микропрограмм, входы которых подключены соответственно к выходам пер вой и второй секций регистра адреса микрокоманд, входы КОТОЕЯЛС соединены соответственно с первом и вторым выходами коммутатора адреса, о т л я,чающее с я тем, , с целью уменыйения оборудования н увеличения уровней совмещения больше трех, оно содержит блок приоритета, ошфратор адреса первой микрокоманды, 3,4,..,п

секции регистра адреса микрокоманд ;3,4,...,п секции памяти микрокоманд, 3,4,.;.,п секции регистра микрокоманд, причём входа блока приори.тета являются входами запросов

процедур устройства, а выход блока приоритета соединен с четвертым входбм коммутатора адреса пятый вход которого пoдкJSoчeн к выходу шифратора адреса первой микрокоманды,

шестой вход - к выходу первой секции памяти констант, рходы п. секций которой соединен с группой п входов :кода операции устройства, а вход первой секции подключен к входу шифратора, выходы памяти Констант являются выходами констант устройства; 3,4,...jn шшоды коммутатора подключены соответственно к входам 3,4,..уП секций регистра адреса микрокомгшд, выходы которых соединены соответственно с входами 3,4,.. .,п секций памяти микропрограмм, выходы которых подключены соответственно к входам 3,4,....п секций регистра микрюкоманд, выходы которого подключены соответственно к группе входов коммутатора и являются выходами микрокоманд устройства.

Источники информации,

принятые во внимание при зкспертизе

1.Патент США 3800293, кл. 340-172,5, отублик. 1974.

2.Авторское свидетельство СССР 561964, кл. G 06 F 9/22, 1977

(прототип).

ilil

m

T

йШЖг

I fII л I

iL

uH

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Микропрограммное устройство управления | 1975 |

|

SU561964A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммное устройство управления | 1980 |

|

SU940158A1 |

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор | 1985 |

|

SU1280378A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

I I- ITi. , ,11

с

nxicz

иг,г

JJ

ZJ

Авторы

Даты

1982-07-07—Публикация

1980-10-23—Подача