(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управ-лЕНия | 1979 |

|

SU842815A1 |

| Устройство микропрограммного управления | 1984 |

|

SU1226453A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134937A1 |

| Микропрограммный процессор | 1985 |

|

SU1312595A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1156071A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления | 1974 |

|

SU519711A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

Изобретение относится к вычисли«тельной технике, в частности к микропрограммным устройствам упр авления. Известно микропрограко4ное устрой ство управления, содержащее блок па мяти микрокоманд, регистр микрокоманда), регистр адреса микрокоманды де&жфратор ишкрокоманд 1 . Недостатком устройства является необходиьюсть большего количества регистров возврата и элементов связи этих регистров с регистром адреса микрокоманд при организации возв рата из микропрограмм, что приводит к излишним затратам оборудования. Наиболее близким по технической сущности к предлагаемому является мнкропрогршшное устройство управления , содержащее память микрокоман Кзоизхул которой соединены со входом регистра микрокоманд, регистр адреса микрокоманды, выходы которого че реэг деишфратор адреса микрокоманды ярдключены ко входам памяти кшкрококанд, коммутатор, информационные выходы которого соединены с первой группой входов регистра адреса мик.рок(4аиды, дешифратор микрокоманды, .входы которого подключены к первой группе выходов регистра микрокоманд, оперативную память, причем, выход регистра микрокоманд соединен с управляющим входом коммутатора, а вторая группа выходов регистра микрокоманд соединена со второй группой входов регистра адреса микрокоманда. Известное устройство предусматривает использование шифратора, блока реверсивных формирователей тока для организации запоминания и считывания адресов возвратов из микроподпрограмм. При этом используется регистр регенерации, блок усилителей чтения, дешифратор адреса оперативной памяти, а также часть объема памяти микрокоманд для управления указанным оборудованием 2 . Недостатком устройства является необходимость затрат большого количества оборудования. Целью изобретения является сокращение оборудования. Цель достигается тем, что в микропрограммном устройстве управления, содержащем блок памяти микрокоманд, вход которого соединен с выходом дешифратора адреса микрокоманд, а выход - со входом регистра микрокоманд, выход кода команды которого

соединен с информационным входом дешифратора микрокоманд, выход управления регистра микрокоманд соединен с управляющим входом коммутатора, а выход функциональной выборки - с адрестзм входом регистра адреса микрокоманд, разрядный выход которого соединен со входом дешифратора адреса микрокоманд, а информационный вхо регистра, адреса микрокоманд соединен с информационным выходом коммутатора, блок оперативной памяти, выход функциональной выборки регистра шскрокоманд соединен с адресным входом регистра адреса оперативной памяти, управляющий вход которого сгоединен с первым выходом дешифратора микрокоманд, управляющий вход блока оперативной памяти соединен со вторым выходом дешифратора микрокоманд, третий выход которого соединен с управляквдим входом регистра адреса микрокоманд, выход блока памяти 1 шкрокоманд соединен с первым информационнь « входом кокмутатора, второй информационный вход которого соединен с выходом блока оперативной памяти , информационный вход которого сЬединен с информационным выходом коммутатора.

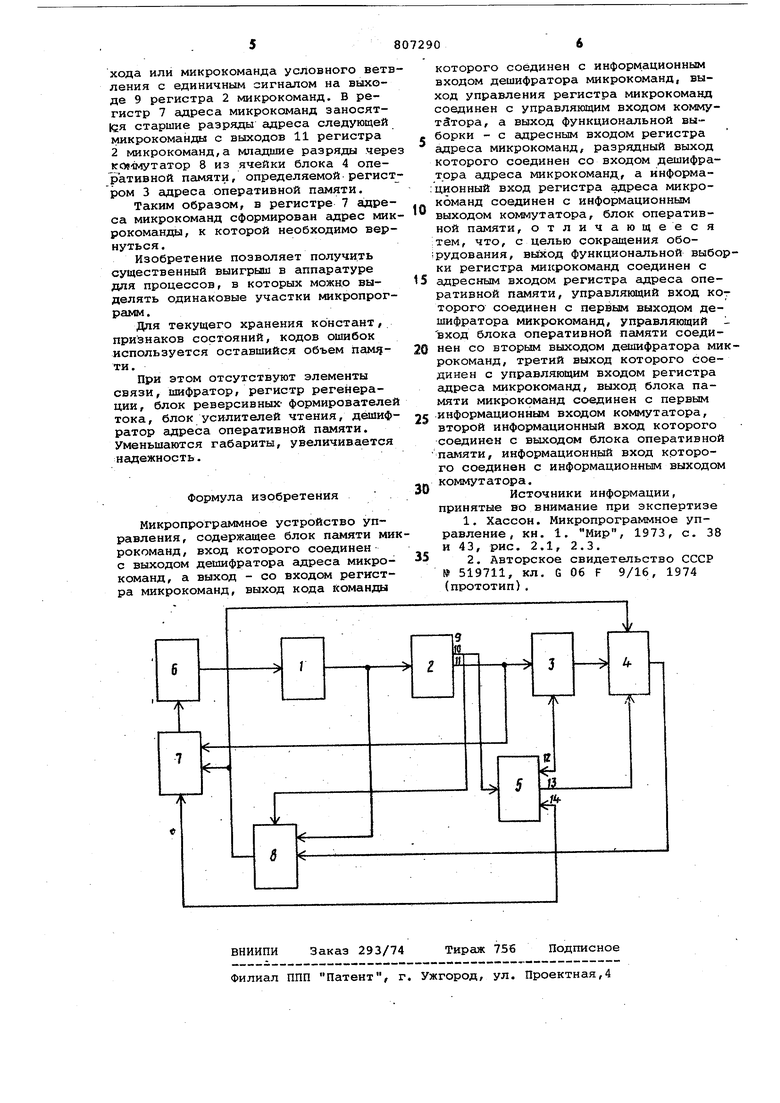

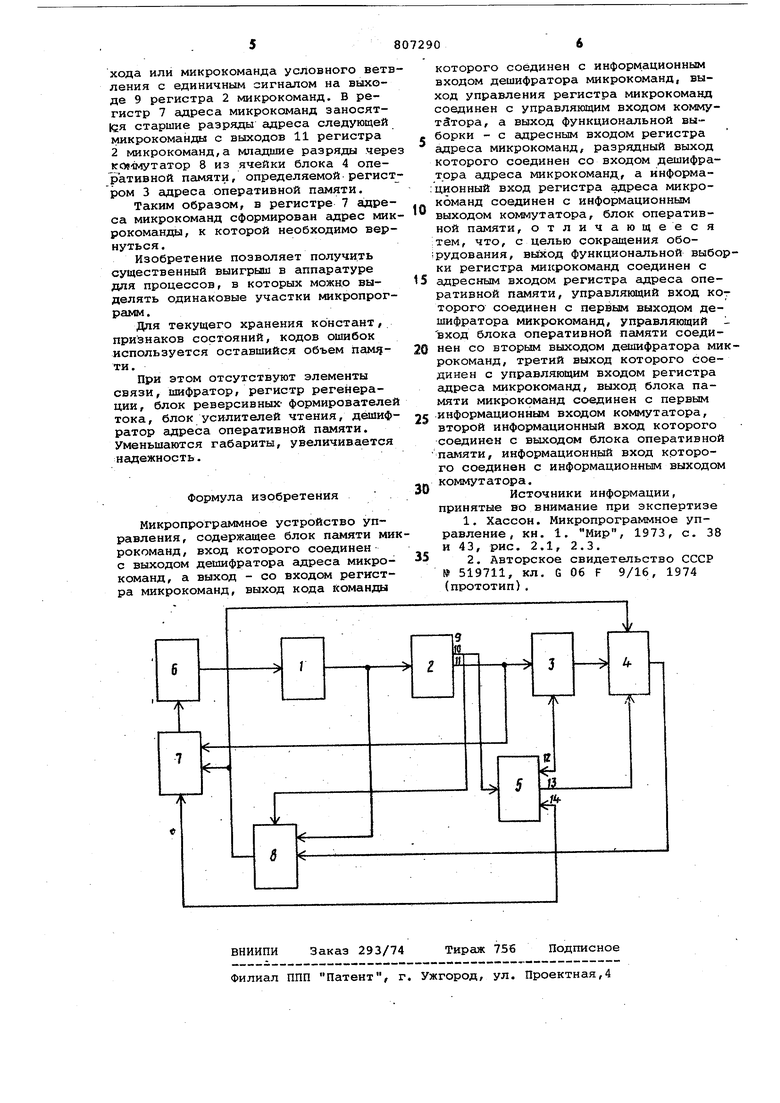

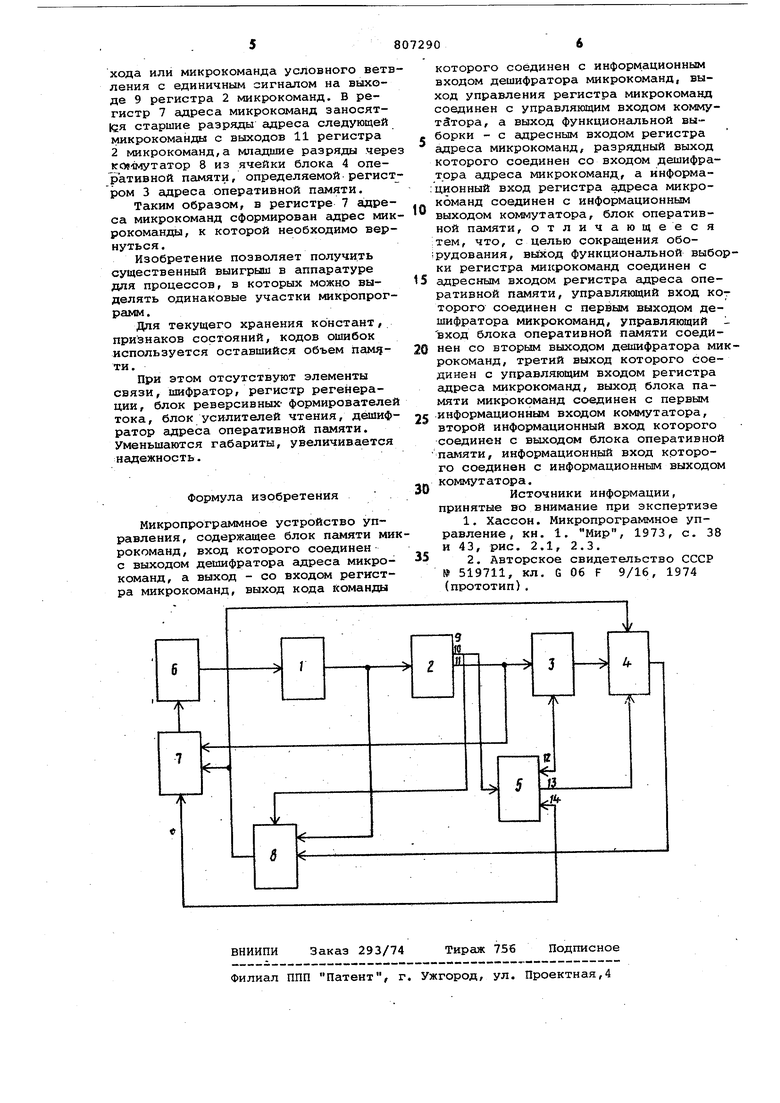

На чертеже представлена блок-схема устройства.

Устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, регистр 3 адреса оперативной памяти, блок 4 оперативнойпамяти, дешифратор 5 микрокоманд, дешифратор 6 адреса микрокоманд, регистр 7 адреса микрокоманд, коммутатор 8, выходам 9-11 регистра микрокоманд, выходы 12-14 дешифратора микрокоманд. Выход 9 является выходом поля управления, управляквдий коммутатором, выход 10 - разряды поля кода команды, выход 11 - выход ПОЛЯ функциональной выборки, использующийся для выбора адреса оперативной памяти и старших разрядов адреса следующей микрокоманды.

Устройство работает следуклцим образом.

Микрокоманды выбираются из блока

1памяти микрокоманд через дешифратор 6 адреса микрокоманд по адресу, хранимому в регистре 7 адреса микрокоманды, и засыпается в регистр

2микрокоманд. Выбранная микрокоманд ра Ьифровывается в дешифраторе 5 микрокоманд и формирует сигналы, управляющие занесением информации в регистр 3 адреса оперативной памяти,

в блок 4 оперативной памяти и в регистр 7 адреса микрокоманд.

Адрес очередной микрокоманды формируется в регистре 7 адреса микрокоманд. Содержимое регистра 7 адреса микрокоманд сигналом с выхода 11 дешифратора 5 микрокоманд увеличивается на единицу при выполнении всех

микрокоманд, кроме микрокоманды безусловного перехода и микрокоманды условного ветвления.

Если выполняется микрокоманда безусловного перехода или микрокоманда условного ветвления, то в регистр 7 адреса микрокоманд заносятся старшие разряды адреса следующе микрокоманды с выхода 11 регистра 2 микрокоманд, а младшие разряды - через коммутатор 8 из блока 1 памяти микрокоманд при наличии логического нуля на выходе 9 регистра 2 микрокоманд или из блока 4 оперативной памяти при наличии логической единицы. Причем, младшие разряды .адреса следующей микрокоманды выбираются из блока 4 оперативной памяти, определяемой регистром 3 адреса Оперативной памяти, или из ячейки блока 1 памяти микрокоманд, адрес которой увеличен на единицу, относительно адреса микрокоманды безусловного перехода или условного ветвления. В последнем случае не происходит дешифрация кода адреса, занесенного и в регистр микрокоманд.

При построении микропрограмм часто возникает ситуация, когда микропрограмма А включает в качестве микроподпрограммы микропрограмму В, которая в свою очередь содержит микропрограмму С и т.д.

Две микропрогра1ммы С и Д будем счтать i-ранга, если они не могут Б стречаться одна внутри другой и не : содержит в себе микропрогра Ф1 ранга i и выше.

Для регистров возврата требуется столько ячеек, сколько рангов в организованных микроподпрограммах. При необходимости обратиться к микроподпрограмме i-го ранга непосредственно перед микроподпрограммой выполняюся микрокоманда Выбор РОН, стробируквдая занесение информации с выходов 11 регистра 2 микрокоманд в регистр 3 адреса оперативной памяти, и микрокоманда Загрузка РОН, формирующая импульс разрешения записи по информационным входги в ячейку блока 4 оперативной памяти, определяемой регистром 3 адреса оперативной памяти, кода адреса возврата, поступающего из ячейки блока 2 памяти микрокоманд, адрес которой увеличен на единицу относительно адреса микрокоманды Загрузка РОН. В последнем случае не происходит дешифрация кода адреса возврата, занесенного и в регистр микрокоманд.

Для выхода из микроподпрограммы после выполнения последней микроко- манды микроподпрограммы должны вьщолЪяться микрокса 1анда Выбор РОН, стрббирующая занесение информации с выходов 11 регистра 2 микрокоманд в регистр адреса оперативной памяти 3. и микрокоманда безусловного перехода или микрокоманда условного вет ления с единичным сигналом на выходе 9 регистра 2 микрокоманд. В регистр 7 адреса микрокоманд заносятКгя старшие разряды адреса следующей микрокоманды с выходов 11 регистра 2 микрокоманд, а младшие разряды .чер дсх- мутатор 8 из ячейки блока 4 оперативной памяти, определяемой-perHC ром 3 адреса оперативной памяти. Таким образом, в регистре 7 адре са микрокоманд сформирован адрес ми рокоманды, к которой необходимо вер нуться. Изобретение позволяет получить существенный выигрыш в аппаратуре для процессов, в которых можно выделять одинаковые участки микропрог Для текущего хранения констант, признаков состояний, кодов ошибок используется оставшийся объем . При этом отсутствуют элементы связи, шифратор, регистр регенерации, блок реверсивных- формирователе тока, блок усилителей чтения, дешиф ратор адреса оперативной памяти. Уменьшаются габариты, увеличивается надежность. Формула изобретения Микропрограммное устройство управления, содержащее блок памяти ми рокоманд, вход которого соединен с выходом дешифратора адреса микрокоманд, а выход - со входом регистра микрокоманд, выход кода команды которого соединен с информационным входом дешифратора микрокоманд, выход управления регистра микрокоманд соединен с управляющим входом коммутЗтора, а выход функциональной выборки - с адресным входом регистра адреса микрокоманд, разрядный выход которого соединен со входом дешифратора адреса микрокоманд, а информационный вход регистра адреса микрокоманд соединен с информационным выходом коммутатора, блок оперативной памяти, отличающееся тем, что, с целью сокращения оборудования, выход функциональной выборки регистра микрокоманд соединен с адресным входом регистра адреса оперативной памяти, управляющий вход ког торого соединен с перёым выходом дешифратора микрокоманд, управляющий 1 вход блока оперативной памяти соединен со вторым выходом дешифратора микрокоманд, третий выход которого соединен с управляющим входом регистра адреса микрокоманд, выход блока памяти микрокоманд соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом блока оперативной памяти, информационньй вход крторого соединен с информационным выходом коммутатора. Источники информации, принятые во внимание при экспертизе 1. Кассой. Микропрограммное управление, кн. 1. Мир, 1973, с. 38 и 43, рис. 2.1, 2.3. 2. Авторское свидетельство СССР № 519711, кл. G 06 F 9/16, 1974 (прототип).

Авторы

Даты

1981-02-23—Публикация

1978-08-11—Подача