Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении микропрограммных устройств управления ЭВМ и вычислит0льных систем, например специализированных процессоров квазиэлектронных и электронных АТС.

Известно микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистры адреса, микроопераций и буферный, триггеры управления, генератор импульсов, коммутатор, элементы И. ИЛИ. Недостатком этого устройства являются ограниченные функциональные возможности, обусловленные отсутствием технических средств реализации механизмов возврата на микроподпрограмму, прерывания и т.д.

Известно микропрограммное устройство управления, содержащее блок памяти, егистры адреса и микроопераций, элемент И, мультиплексоры.

Недостатком данного устройства явля- 5 ется ограниченная область применения вследствие невозможности организации режима прерывания, эмуляции и т.д.

Известно микропрограммное устройство управления, содержащее блок памяти 10 микрокоманд, регистры, блоки сравнения, риггер, генератор импульсов, мультиплексоры адреса и логических условий, элементы И, элемент задержки.

Недостатками указанного устройства 15 являются узкая область применения, что вызвано невозможностью обеспечения режима непосредственного доступа к микропрограммной памяти с программного уровня, а также большой объем блока памя- 20 ти.

Наиболее близким к изобретению является устройство микропрограммного управления, содержащее блок памяти, регистр микрокоманд, регистр адреса микроко- 25 манд, счетчик адреса, преобразователь кода микрокоманд,- дешифратор перехода, ешифратор адреса, первый - четвертый элементы И, блок управления, элемент ИДИ, элемент НЕ и генератор импульсов, 30 причем труппа информационных выходов блока памяти соединена с группой входов регистра микрокоманд, группа выходов которого соединена с группой входов дешифратора перехода и информационными 35 входами первого и второго элементов И, выход которого соединен с входом преобразователя кода микрокоманд, выход преобразователя кода микрокоманд является выходом устройства, второй и третий выхо- 40 ды дешифратора перехода соединены с информационными входами блока управления, группа выходов которого соединена с группой входов элемента ИЛИ, выход элемента ИЛИ соединен с входом элемента НЕ 45 и с управляющим входом второго элемента И, выход которого соединен с первым информационным входом счетчика адреса, группа входов устройства соединена с вторым информационным входом счетчика ад- 50 реса, выход которого соединен с информационным входом третьего элемента И, выход третьего элемента И соединен с входом записи регистра адреса микрокоманд, выход которого соединен с входом 55 дешифратора адреса, первый выход генератора импульсов соединен с первым входом четвертого элемента И, управляющими входами регистра адреса микрокоманд и де- шифря гэра «дпеса. группа выходов

которого соединена с группой входов блока памяти, второй выход генератора импульсов соединен с управляющим входом треть- его элемента И, выход элемента НЕ соединен с вторым входом четвертого элемента И, выход которого соединен со счетным входом счетчика-адреса, управляющий вход устройства соединен с входом блока управления. Блок управления содержит элемент И, причем первый информационный вход блока управления соединен с первым входом элемента И, выход которого соединен с первым выходом блока управления, второй информационный вход блока управления соединен с вторым его выходом, уп- равляющий вход блока управления соединен с вторым входом элемента И.

Недостатком указанного устройства является узкая область применения, что обусловлено следующим.

Устройство не позволяет реализовать режим прерывания как от внешних источников (средств контроля, более приоритетных абонентов и т.д.), так и от пультовых средств при осуществлении отладки микропрограмм, контроля и диагностики системы. Это ограничивает область применения устройства при управлении сложными объектами с несколькими активными разноприоритет- ными источниками выполнения микропрограмм, снижает его контролепригодность.

В указанном устройстве отсутствуют технические средства реализации механизма возврата на микропрограмму, прерванную внутренними источниками прерывания по соответствующим микрооперациям (микрокодам), указанным в микрокомандах. Это обстоятельство существенно увеличивает объем блока памяти, поскольку не позволяет использовать повторяющиеся микроподпрограммы.

Кроме того, данное устройство не обеспечивает возможность оперативной модификации микропрограмм, т.е. перекомпоновки микрокоманд в соответствии с адресами, задаваемыми извне. Это также сужает возможности устройства, мобильность его микропрограмм, способность к эмуляции.

Указанные причины значительно сужают область применения устройства, увеличивают объем микропрограммной памяти, затрудняют его эксплуатацию.

Целью изобретения является расширение области применения.

Поставленная .цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти, регистр микрокоманд, регистр возврата, счетчик адреса, первый элемент ИЛИ, первый -третий элементы И, группу элементов И, генератор импульсов и дешифратор, причем группа информационных выходов блока памяти соединена с группой информационных входов регистра микрокоманд, группа управляющих выходов которого соединена с группой входов дешифратора, второй выход генератора импульсов соединен с вторым входом второго элемента И, первая, вторая и третья группы выходов регистра микрокоманд соединены соответственно с первой, второй и третьей группами входов группы элементов И, дополнительно введены блок управления, блок приема информации, мультиплексоры адреса, выбора и логических условий, пульт управления, группа эле- менто в Й-И Л И, второй .- четвертый элементы ИЛИ, элемент И-ИЛИ, формирЬт вате ль константы, шифратор, причем группа выходов дешифратора соединена с группой информационных входов блока уп- равления, группа выходов которого соединена с входами первого элемента ИЛИ, первая группа выходов блока приема информации соединена с группой входов шифратора, группа выходов которого сое динена с первой группой входов группы элементов И-ИЛИ, и входами второго элемента ИЛИ, вторая группа выходов блока приема информации соединена с первой группой D-входов мультиплексора адреса, группа выходов которого соединена с группой D-входов счетчика адреса, третья группа выходов блока приема информации соединена с второй группой D-входов мультиплексора адреса, группа информацион- ных выходов пульта управления соединена с второй группой входов группы элементов И-ИЛИ, группа выходов которой соединена с третьей группой D-входов мультиплексора адреса, первый управляющий выход пульта управления соединен с первым входом блока управления и прямым инверсным входом группы элементов И-ИЛИ, выход первого элемента ИЛИ соединен с первым инверсным входом первого элемента И элемента И-ИЛИ, выход второго элемента ИЛИ соединен с первым входом третьего элемента .И, четвертая труппа выходов блока приема информации соединена с информационными входами мультиплексора логических уе- ловий, выход которого соединен с вторым, входом блока управления, второй управляющий выход пульта управления соединен с входом генератора импульсов, первый выход генератора импульсов соединен с пер- выми входами второго и третьего элементов И, элемента И-ИЛИ и первым входом пульта управления, второй выход генератора импульсов соединен с вторым входом первого элемента и элемента И-ИЛИ, и вторым входом первого элемента И, выход которого соединен с С-входом счетчика адреса, третий выход генератора импульсов соединен с С-входом регистра микрокоманд и вторым входом пульта управления, первый управляющий выход регистра микрокоманд соединен с вторым входом третьего элемента И, второй управляющий выход регистра микрокоманд соединен с вторым входом второго элемента И, элемента И-ИЛИ и первым входом третьего элемента ИЛИ, выход третьего элемента ИЛИ соединен с вторым входом второго элемента И, выход которого соединен с С-входом регистра возврата, группа выходов мультиплексора выбора соединена с четвертой группой D-входов мультиплексора адреса и группой входов блока памяти, первая группа выходов регистра микрокоманд соединена с группой адресных входов мультиплексора логических условий, вторая группа выходов регистра микрокоманд соединена с пятой и шестой группами D-входов мультиплексора адреса, третьея группа выходов регистра микрокоманд соединена с пятой и седьмой группами D-входов мультиплексора адреса, первая - третья группа выходов группы элементов И и четвертая группа выходов регистра микрокоманд являются соответственно первой- четвертой группами выходов устройства, пятая группа выходов регистра микрокоманд соединена с группой адресных входов мультиплексора выбора и труппой входов четвертого элемента ИЛИ, выход которого соединен с третьим входом блока управления, выход третьего элемента И соединен с вторым входом третьего элемента ИЛИ, с вторым входом третьего элемента И элемента И-ИЛИ и четвертым входом блока управления, группа выходов которого соединена с группой адресных входов мультиплексора адреса, третий и четвертый управляющие выходы регистра микрокоманд соединены соответственно с пятым и шестым входами блока элемента И и первым инверсным входом первого элемента И элемента И-ИЛИ, выход второго элемента ИЛИ соединен с первым входом первого элемента И, четвертая группа выходов блока приема информации соединена с информационными входами мультиплексора логических условий, выход которого соединен с третьим входом блока управления, первый выход генератора импульсов соединен с первым входом пульта управления и первыми входами второго и третьего элементов И элемента И-ИЛИ, второй выход генератора импульсов соединен с первым входом второго элемента И, вторым входом первого элемента И элемента И-ИЛИ, третий выход генератоpa импульсов соединен с С-входом регистра микрокоманд и вторым входом пульта управления, первый управляющий выход регистра микрокоманд соединен с вторым входом второго элемента И элемента И- ИЛИ и первым входом третьего элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И, выход третьего элемента И соединен с С-входом регистра возврата, группа выходов мультиплексора выбора соединена с четвертой группой D- входов мультиплексора вдреса и группой входов блока памяти, первая группа выходов регистра микрокоманд соединена с группой адресных входов мультиплексора логических условий, первая, вторая и третья группы выходов группы элементов И являются соответственно первой-третьей груп пами выходов устройства, вторая группа выходов регистра микрокоманд соединена

с пятой и шестой группами D-входов мультиплексора адреса, третья группа выходов регистра микрокоманд соединена с пятой и седьмой группами D-входов мультиплексора адреса, четвертая группа выходов регистра микрокоманд является четвертой группой выходов устройства, пятая группа выходов регистра микрокоманд соединена с группой адресных входов мультиплексора выбора и группой входов четвертого элемента ИЛИ, выход которого соединен с четвертым входом блока управления, выход первого элемента И соединен с вторым входом третьего элемента ИЛИ, с вторым входом третьего элемента И элемента И-ИЛИ и с пятым входом блока управления, второй и третий управляющие выходы регистра микрокоманд соединены соответственно с шестым и седьмым входами блока управления, выход элемента И-ИЛИ соединен с счетным входом счетчика адреса, группа выходов которого соединена с группой D-входов регистра возврата и первой группой D-входов мультиплексора выбора, полугруппа выходов счетчика адреса соединена с шестой и седьмой группами D-входов мультиплексора адреса, группа выходов дешифратора соединена с группой информационных входов блока управления, группа управляющих выходов регистра микрокоманд соединена с группой входов дешифратора, первый выход которого соединен с управляющими входами группы элементов И, выходы элемента И-ИЛИ соединены с счетным входом счетчика адреса, группа выходов которого соединена с группой D-входов регистра возврата и первой группой D-входов мультиплексора выбора, полугруппа выходов счетчика адреса, содержащая старшие разряды, соединена с шестой и седьмой группами D-входов мультиплексора адреса, группа выходов формирователя константы соединена с второй группой D-входов муль типлексора выбора, группа выходов регистра возврата соединена с третьей группой D-входов мультиплексора выбора, выход первого разряда второй группы выходов блока приема информации соединен с седьмым входом блока управления, второй вы0 ход дешифратора, второй - четвертый выходы регистра микрокоманд соединены с первым - четвертым управляющими выходами устройства, группы входов кода операции, кода прерывания, кода внешнего

5 адреса и кода логических условий соединены соответственно с первой, второй, третьей и четвертой группами информационных входов блока приема информации, первый и третий выходы генератора импуль0 сов соединены соответственно с первым и вторым синхровходами блока приема информации, группа управляющих входов которого образована вторым выходом дешифратора, а также третьим и четвертым

5 управляющими выходами регистра микрокоманд, четвертый выход регистра микрокоманд соединен с входом разрешения прерывания блока приема информации. Сущность изобретения состоит в рас0 ширении области применения устройства путем расширения числа реализуемых режимов микропрограммного управления.

Отличительными признаками механизма функционирования, реализуемого в

5 предлагаемом устройстве, являются обеспечение возможности оперативной модификации выполняемой микропрограммы (изменения последовательности микрокоманд), организация прерывания выполняе0 мых микропрограмм от внешних и внутренних источников, организация механизма возврата при выполнении однотипных операции как к прерванному, так и к фиксированному адресу.

5 Введение блока управления и обусловленных им связей позволяет управлять выбором различных механизмом адресации.

Введение мультиплексора адреса позволяет организовать запись адреса в счет0 чик адреса в семи режимах работы устройства: линейном, внешней адресации, информирования адреса по окончанию команды, прерывания, возврата, безусловного перехода, условного перехода.

5 Введение блоха приема информации позволяет осуществить прием внешней информации с привязкой к сигналам синхронизации устройства.

Введение мультиплексора выбора позволяет организовать режим возврата и считывания начального адреса стандартной подпрограммы.

Введение мультиплексора логических условий позволяет формировать сигнал, информирующий о выполнении проверяемого логического условия.

Введение пульта управления позволяет сформировать адрес начальной микрокоманды.

Введение группы элементов И-ИЛИ по- зволяет сформировать начальный адрес микрокоманды в режиме прерывания и по команде с пульта управления.

Введение второго элемента ИЛИ позволяет сформировать управляющий сигнал при поступлении сигнала на-прерывание извне.

Введение третьего элемента ИЛИ позволяет формировать сигнал, управляющий записью в регистр возврата.

Введение элемента И-ИЛИ позволяет управлять подачей сигнала на счетный вход счетчика адреса.

Введение формирователя константы позволяет получить адрес начальной микро- команды некоторой стандартной микроподпрограммы.

Введение шифратора позволяет формировать адрес микрокоманды при обработке сигнала на прерывание, поступающего из- вне.

При использовании предлагаемого устройства может быть получен положительный эффект, состоящий в расширении области применения устройства, уменьще- нии объема оборудования (памяти микро- программ), упрощения (удешевления) процесса эксплуатации за счет повышения контролепригодности и обеспечения возможности модификации микропрограмм.

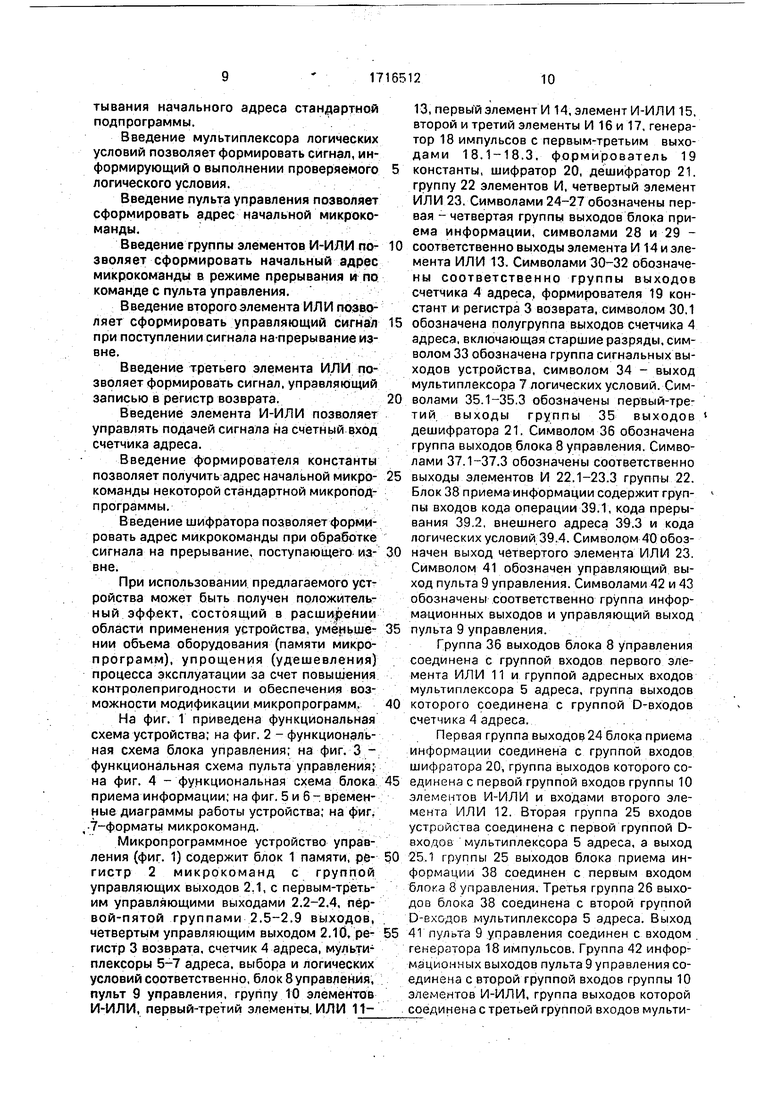

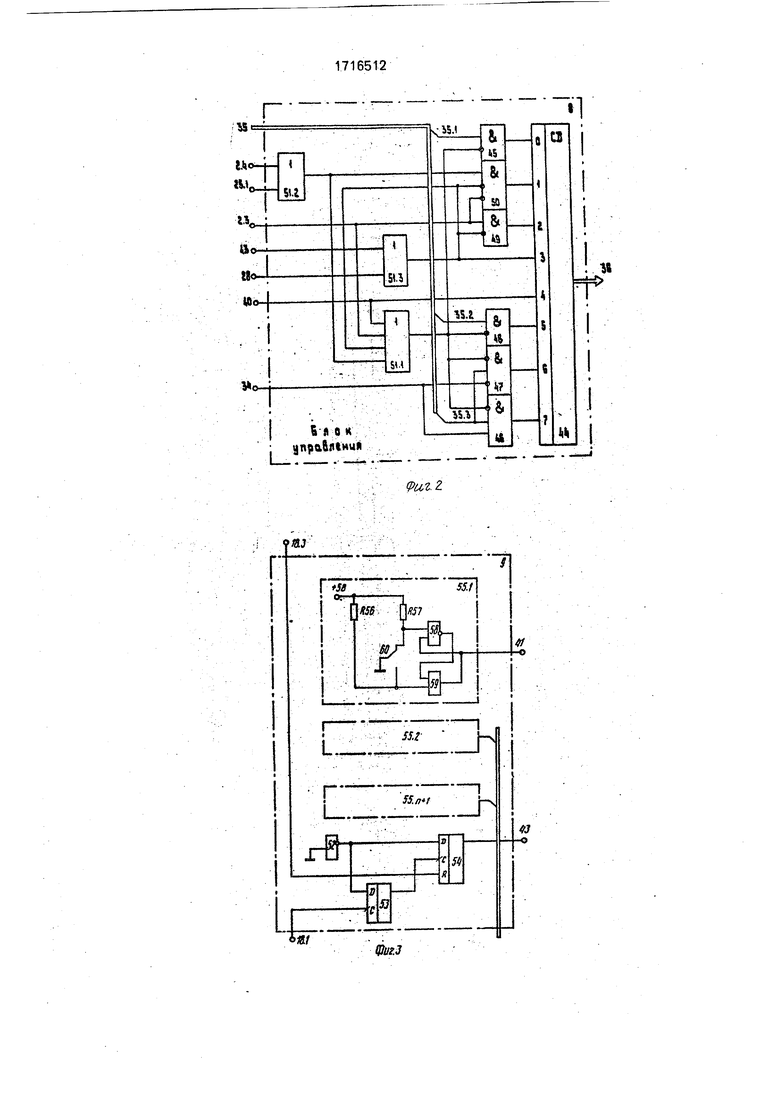

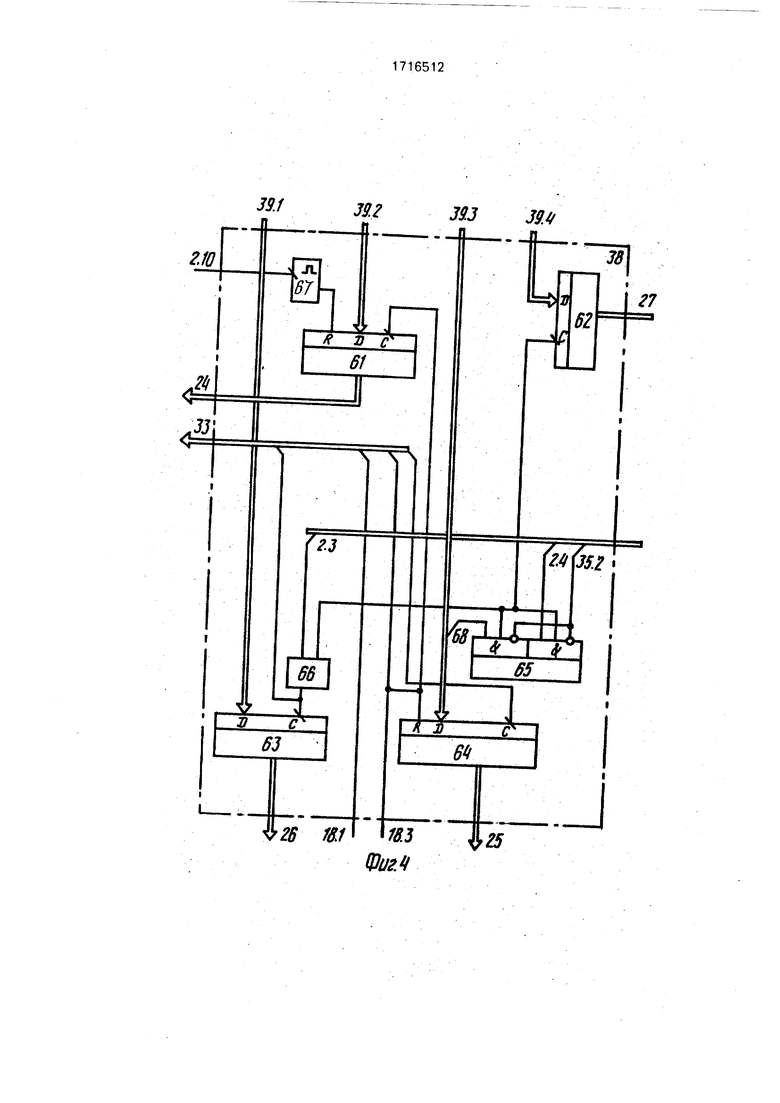

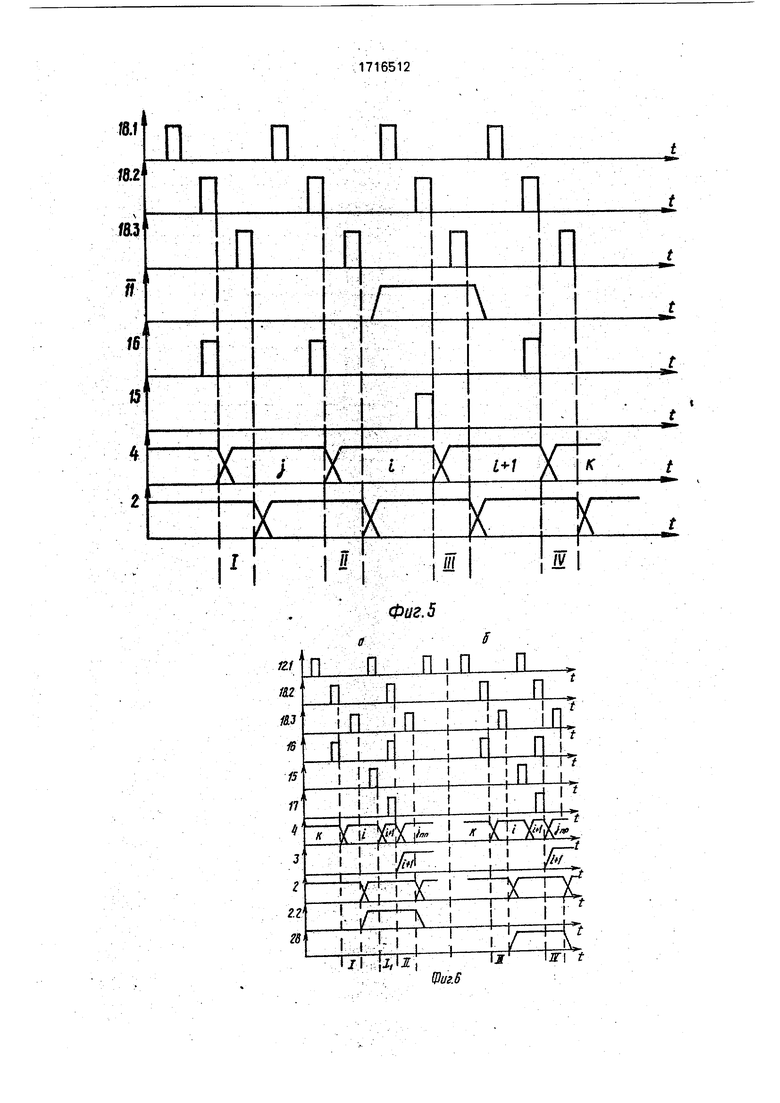

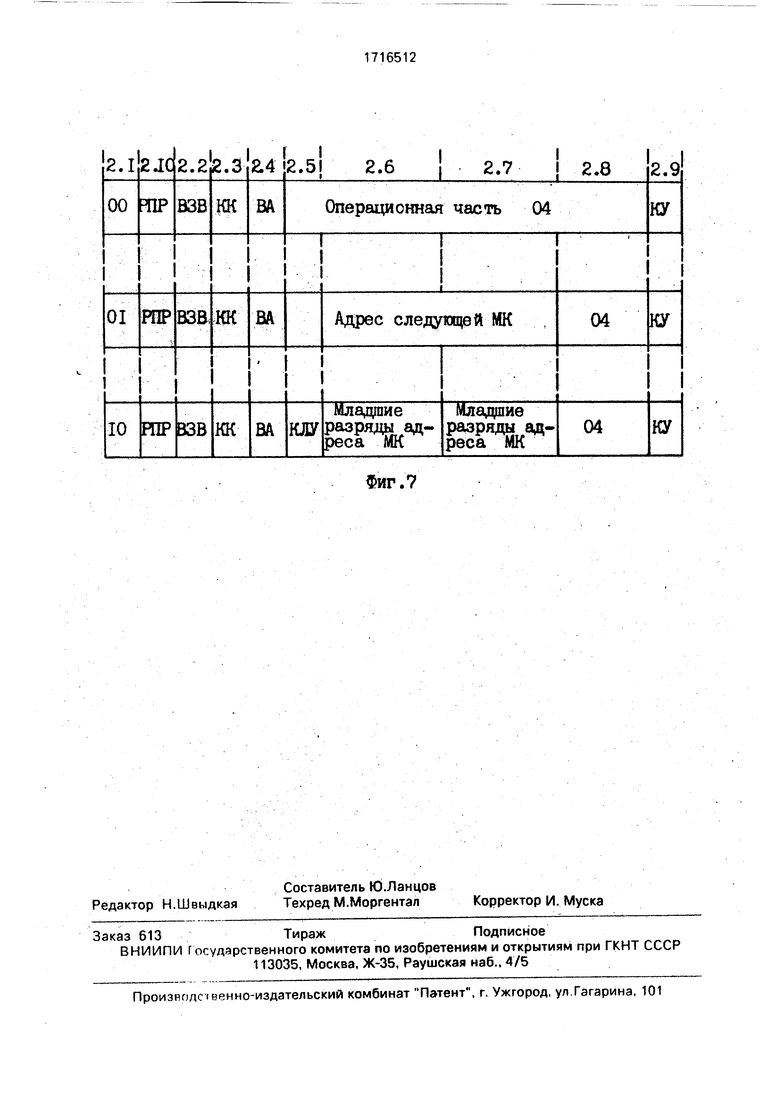

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема пульта управления; на фиг. 4 - функциональная схема блока приема информации; на фиг. 5 и 6 - временные диаграммы работы устройства; на фиг, 7-форматы микрокоманд.

Микропрограммное устройство управления (фиг. 1) содержит блок 1 памяти, ре- гистр 2 микрокоманд с группой управляющих выходов 2,1, с первым-третьим управляющими выходами 2.2-2.4, пёр- вой-пятой группами 2.5-2.9 выходов, четвертым управляющим выходом 2.10. ре- гистр 3 возврата, счетчик 4 адреса, муль-м1 плексоры 5-7 адреса, выбора и логических условий соответственно, блок 8 управления, пульт 9 управления, группу 10 элементов И-ИЛИ, первый-третий элементы. ИЛИ 1113, первы й элемент И 14, элемент И-ИЛИ 15, второй и третий элементы И 16 и 17, генератор 18 импульсов с первым-третьим выходами 18.1-18.3, формирователь 19 константы, шифратор 20, дешифратор 21. группу 22 элементов И, четвертый элемент ИЛИ 23. Символами 24-27 обозначены первая -четвертая группы выходов блока приема информации, символами 28 и 29 - соответственно выходы элемента И 14 и элемента ИЛИ 13. Символами 30-32 обозначены соответственно группы выходов счетчика 4 адреса, формирователя 19 констант и регистра 3 возврата, символом 30,1 обозначена полугруппа выходов счетчика 4 адреса, включающая старшие разряды, символом 33 обозначена группа сигнальных выходов устройства, символом 34 - выход мультиплексора 7 логических условий. Символами 35.1-35.3 обозначены первый-третий выходы группы 35 выходов дешифратора 21. Символом 36 обозначена группа выходов блока 8 управления. Символами 37.1-37.3 обозначены соответственно выходы элементов И 22.1-23.3 группы 22. Блок 38 приема информации содержит группы входов кода операции 39.1, кода прерывания 39,2, внешнего адреса 39.3 и кода логических условий 39.4. Символом 40 обозначен выход четвертого элемента ИЛИ 23. Символом 41 обозначен управляющий выход пульта 9управления. Символами 42 и43 обозначены соответственно группа информационных выходов и управляющий выход пульта 9 управления.

Группа 36 выходов блока 8 управления соединена с группой входов первого элемента ИЛИ 11 и группой адресных входов мультиплексора 5 адреса, группа выходов которого соединена с группой D-входов счетчика 4 адреса..

Первая группа выходов 24 блока приема информации соединена с группой входов шифратора 20, группа выходов которого соединена с первой группой входов группы 10 элементов И-ИЛИ и входами второго элемента ИЛИ 12. Вторая группа 25 входов устройства соединена с первой группой D- входов мультиплексора 5 адреса, а выход 25.1 группы 25 выходов блока приема информации 38 соединен с первым входом блока 8 управления. Третья группа 26 выходов блока 38 соединена с второй группой Р-ЕХОДОВ мультиплексора 5 адреса. Выход 41 пульта 9 управления соединен с входом генератора 18 импульсов. Группа 42 информационных выходов пульта 9 управления соединена с второй группой входов группы 10 элементов И-ИЛИ, группа выходов которой соединена с третьей группой входов мультиплексора 5 адреса. Управляющий выход 43 пульта 9 управления соединен с вторым вхоом блока 8 управления, прямым и инверсным входами группы 10 элементов И-ИЛИ. Выход первого элемента ИЛИ 11 соединен 5 с первым входом второго элемента И 16 и первым инверсным входом первого элемена И элемента И-ИЛИ 15. Выход второго лемента ИЛИ 12 соединен с первым вхоом первого элемента И 14. Четвертая труп- 10 па 27 выходов блока 38 соединена с информационными D-входами мультиплекора 7 логических условий, выход 34 которого соединен с третьим входом блока 8 правления. Первый выход 18.1 генератора 15 18 импульсов соединен с первым входом пульта 9 управления и первыми входами второго и третьего элементов И элемента

И-ИЛИ 15. Второй выход 18.2 генератора 18 импульсов соединен с первым входом вто- 20

рого элемента И 17, вторым входом первого элемента И элемента ИЛИ 15 и вторым вхоом второго элемента И 16, выход которого соединен с ОБХОДОМ счетчика 4 адреса. Треий выход 18.3 генератора 18 импульсов со- 25 единен с С-входом регистра 2 микрокоманд и вторым входом пульта 9 управления, Первый управляющий выход 2.2 регистра 2 микрокоманд соединен с вторым входом второго элемента И элемента И-ИЛИ 15 и 30 первым входом третьего элемента ИЛИ 13, выход 29 которого соединен с вторым вхоом третьего элемента И 17. Выход третьего элемента И 17 соединен с С-входом регистра 3 возврата. Группа выходов мультиплек- 35 сора 6 выбора соединена с четвертой группой D-входов мультиплексора 5 адреса и группой входов блока 1 памяти, группа информационных выходов которого соединена с группой D-входов регистра 2 микро- 40 команд. Первая группа 2.5 выходов регистра 2 микрокоманд соединена с группой адресных входов мультиплексора 7 логических условий и первой группой входов группы 22 элементов И, первая, вторая и 45 третья группы 37.1-37.3 выходов которой являются соответственно первой - третьей группами выходов устройства. Вторая труп- .. па 2.6 выходов регистра 2 микрокоманд соединена с второй группой входов группы 22 50 элементов И и с пятой и шестой группами D-входов мультиплексора 5 адреса. Третья группа 2.7 выходов регистра 2 микрокоманд соединена с третьей группой входов группы 22 элементов И и с пятой и седьмой группа- 55 ми D-входов мультиплексора 5 адреса. Четвертая группа 2.8 выходов регистра 2

микрокоманд является четвертой группой выходов устройства. Пятая группа 2.9 выходов регистра 2 микрокоманд соединена с

группой адресных входов мультиплексора 6 выбора и группой входов элемента ИЛИ 23, выход 40 которого соединен с четвертым входом блока 8 управления. Выход 28 первого элемента И 14 соединен с вторым входом третьего элемента ИЛИ 13, с вторым входом третьего элемента И элемента И- ИЛИ 15 и с пятым входом блока 8 управления. Второй и третий управляющие выходы 2.3 и 2.4 регистры 2 микрокоманд соединены соответственно с шестым и седьмым входами блока 8 управления. Выход элемента И-ИЛИ 15 соединен со счетным входом счетчика 4 адреса, группа выходов которого соединена с группой D-входов регистра 3 возврата и первой группой D-входов мультиплексора 6 выбора. Полугруппа 30.1 выходов счетчика 4 адреса соединена с шестой и седьмой группами D-входов мультиплексора 5 адреса. Группа 2.1 управляющих выходов регистра 2 микрокоманд соединена с. группой входов дешифратора 21, группа 35 выходов которого соединена с группой информационных входов блока 8 управления. Первый выход 35.1 дешифратора 21 соединен с управляющими входами группы 22 элементов И. Группа 31 выходов формирователя 19 констант соединена с второй группой D-входов мультиплексора 6 выбора. Группа 32 выходов регистра 3 возврата соединена с третьей группой D-входов мультиплексора 6 выбора. Второй 35.2 выход дешифратора 21, второй 2.3, третий 2.4, четвертый 2.10 выходы регистра микрокоманд являются первым-четвертым управляющими выходами устройства. Выход 35.2 группы 35 и выходы 2.3 и 2.4 регистра 2 образуют группу управляющих входов блока 38 приема информации.

Четвертый 2.10 управляющий выход регистра 2 микрокоманд соединен с вторым входом первого элемента И 14 и входом разрешения прерывания блока 38 приема информации. Пятая группа выходов блока 38 приема информации является группой сигнальных выходов устройства.

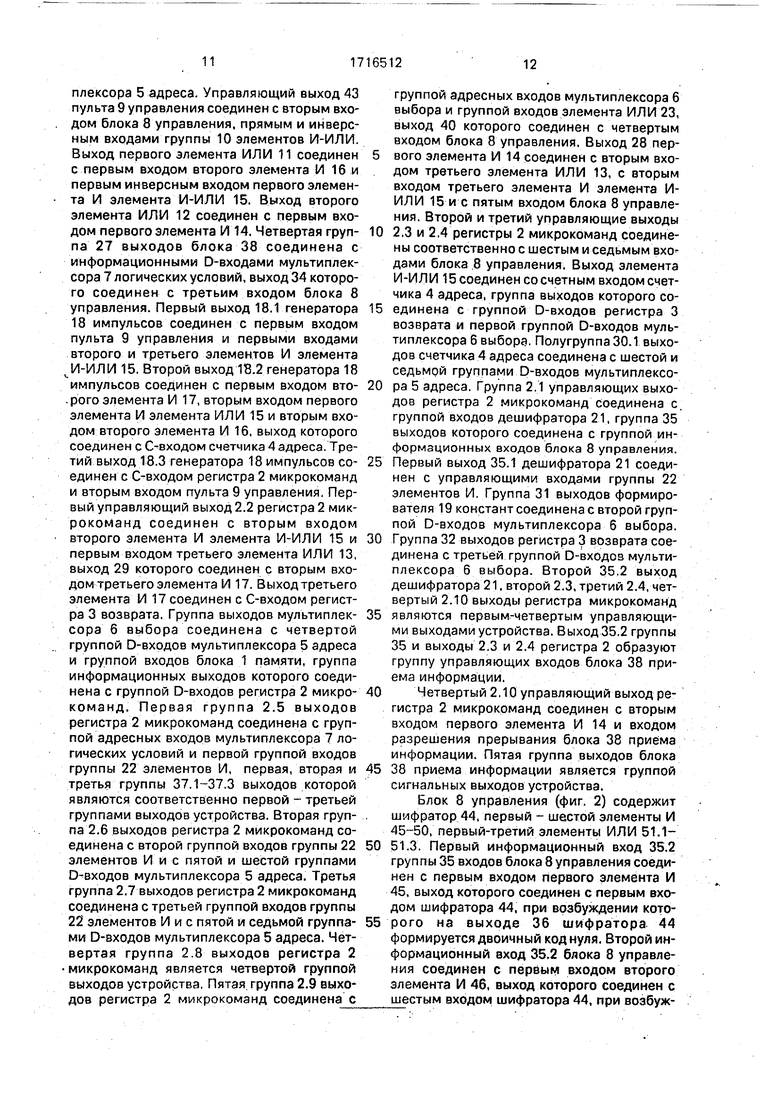

Блок 8 управления (фиг. 2) содержит шифратор 44, первый - шестой элементы И 45-50, первый-третий элементы ИЛИ 51.1- 51.3. Первый информационный вход 35.2 группы 35 входов блока 8 управления соединен с первым входом первого элемента И 45, выход которого соединен с первым входом шифратора 44, при возбуждении которого на выходе 36 шифратора 44 формируется двоичный код нуля. Второй информационный вход 35.2 блока 8 управления соединен с первым входом второго элемента И 46, выход которого соединен с шестым входом шифратора 44, при возбуж.дении которого на выходе шифратора формируется двоичный код пяти. Третий информационный вход 35.3 блока 8 управления соединен с первыми входами третьего 47 и четвертого 48 элементов И. Выход третьего элемента И 47 соединен с седьмым входом шифратора 44, при возбуждении которого на выходе шифратора 44 формируется двск ичный код шести. Выход четвертого элемента И 48 соединен с восьмым входом шифратора 44, при возбуждении которого на выходе шифратора формируется двоичный код семи. Выход первого элемента ИЛИ 51.1 соединен с вторыми инверсными вхр дами первого-четвертого элементов И 45- 48. Вход 34 блока 8 управления соединен с третьим инверсным входом третьего элемента И 47 и третьим прямым входом четвертого элемента И 48. Вход 40 блока 8 управления соединен с первым входом элемента ИЛИ 51.1 и пятым входом шифратора 44, при возбуждении которого на выходе шифратора 44 формируется двоичный код четырех. Управляющий вход 28 блока 8 управления соединен с первым входом элемента ИЛИ 51.3, выход которого соединен с вторым входом элемента ИЛИ 51.1, первыми инверсными входами пятого 49 и шестого 50 элементов И и четвертым входом шифратора 44, при возбуждении которого на выходе шифратора 44 формируется двоичный код трех. Вход 2.3 блока 8 управления соединен с третьим входом элемента ИЛИ 51.1, вторым входом пятого элемента И 49 и вторым инверсным входом шестого элемента И 50, Вход 2.4 блока 8 управления соединен с первым входом элемента ИЛИ 51.2, выход которого соединен с четвертым входом элемента ИЛИ 51.1 и третьим входом шестого элемента И 50. Выход пятого элемента И 49 соединен с третьим входом шифратора 44, при возбуждении которого на выходе шифратора 44 формируется двоич ный код двойки. Выход шестого элемента И 50 соединен с.вторым входом шифратора 44, при возбуждении которого на выходе шифратора формируется код единицы. Вход 25.1 блока 8 управления соединен с вторым входом элемента ИЛИ 51.2. Вход 43 блока 8 управления соединен с вторым входом эй&- мента ИЛИ 51.3. Выход 36 шифратора 44 является выходом блока 8 управления.

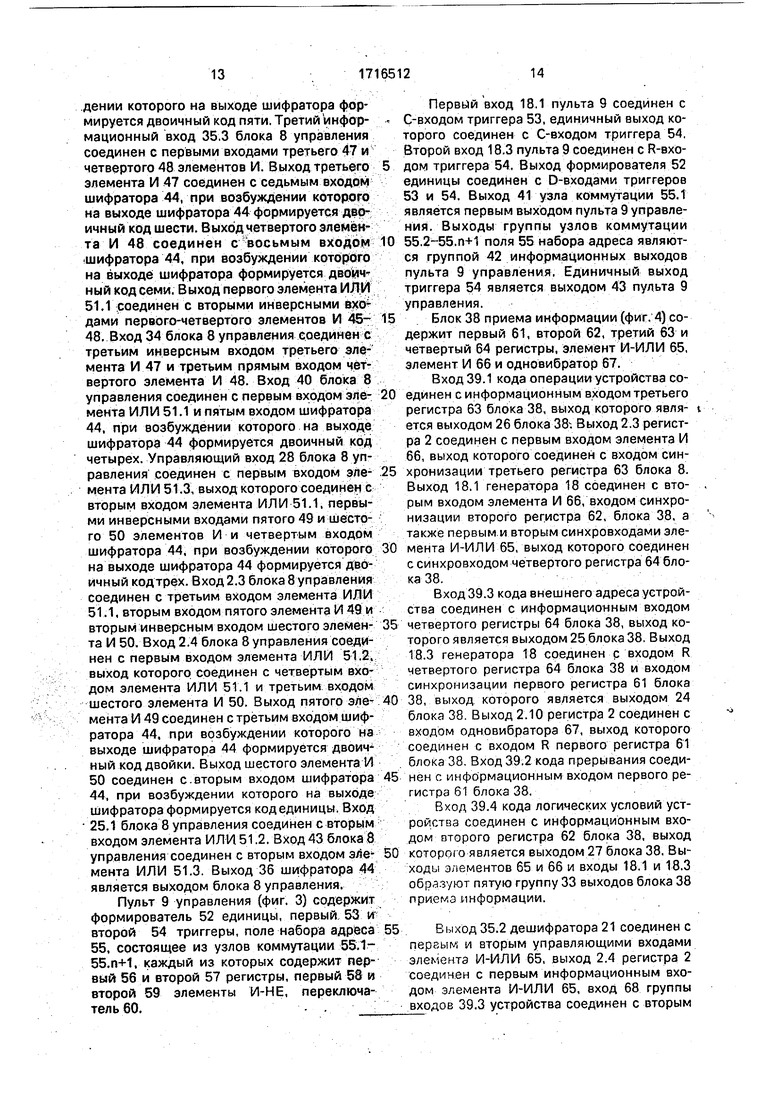

Пульт 9 управления (фиг. 3) содержит формирователь 52 единицы, первый 53 И второй 54 триггеры, поле набора адреса 55, состоящее из узлов коммутации 55.1- 55.n-И, каждый из которых содержит первый 56 и второй 57 регистры, первый 58 и второй 59 элементы И-НЕ, переключатель 60.. .

Первый вход 18.1 пульта 9 соединен с С-входом триггера 53, единичный выход которого соединен с С-входом триггера 54, Второй вход 18.3 пульта 9 соединен с R-входом триггера 54, Выход формирователя 52 единицы соединен с D-входами триггеров 53 и 54. Выход 41 узла коммутации 55.1 является первым выходом пульта 9 управления. Выходы группы узлов коммутации

55.2-55.П+1 поля 55 набора адреса являются группой 42 информационных выходов пульта 9 управления. Единичный выход триггера 54 является выходом 43 пульта 9 управления.

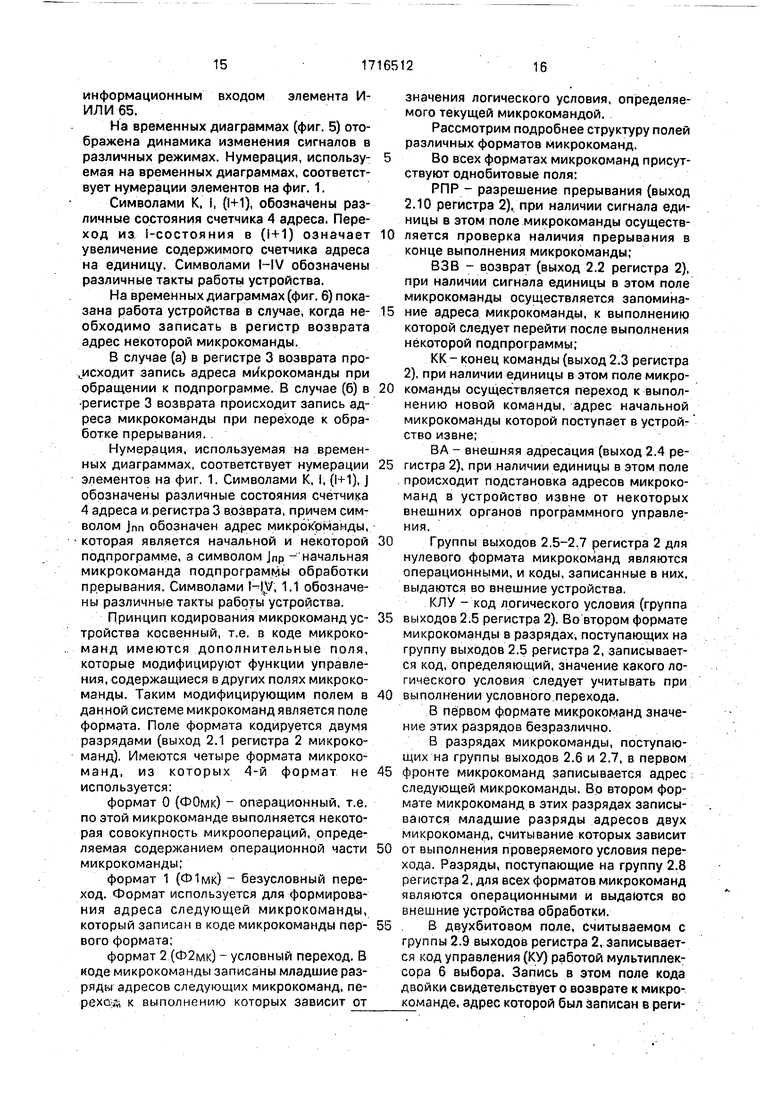

Блок 38 приема информации (фиг. 4) содержит первый 61, второй 62, третий 63 и четвертый 64 регистры, элемент И-ИЛИ 65, элемент И 66 и одновибратор 67.

Вход 39.1 кода операции устройства соединен с информационным входом третьего регистра 63 блока 38, выход которого явля- t ется выходом 26 блока ЗЗгВыход 2.3 регистра 2 соединен с первым входом элемента И 66, выход которого соединен с входом синхронизации третьего регистра 63 блока 8. Выход 18.1 генератора 18 соединен с вто- . рым входом элемента И 66, входом синхронизации второго регистра 62, блока 38, а также первым.и вторым синхровходами элемента И-ИЛИ 65, выход которого соединен с синхровходом четвертого регистра 64 блока 38.

Вход 39.3 кода внешнего адреса уетрой- ства соединен с информационным входом

четвертого регистры 64 блока 38, выход которого является выходом 25 блока 38. Выход 18.3 генератора 18 соединен с входом R четвертого регистра 64 блока 38 и входом синхронизации первого регистра 61 блока

38, выход которого является выходом 24 блока 38. Выход 2.10 регистра 2 соединен с входом одновибратора 67, выход которого соединен с входом R первого регистра 61 блока 38. Вход 39.2 кода прерывания соединем с информационным входом первого регистра 61 блока 38.

Вход 39.4 кода логических условий устройства соединен с информационным входом второго регистра 62 блока 38, выход

которого является выходом 27 блока 38. Выходы элементов 65 и 66 и входы 18.1 и 18.3 образуют пятую группу 33 выходов блока 38 приема информации.

Выход 35.2 дешифратора 21 соединен с первым и вторым управляющими входами элемента И-ИЛИ 65, выход 2.4 регистра 2 соединен с первым информационным входом элемента И-ИЛИ 65, вход 68 группы входов 39.3 устройства соединен с вторым

информационным входом элемента И- ИЛИ65.

На временных диаграммах (фиг. 5) отображена динамика изменения сигналов в различных режимах. Нумерация, использу- 5 емая на временных диаграммах, соответствует нумерации элементов на фиг. 1.

Символами К, I, (1+1), обозначены различные состояния счетчика 4 адреса, Переход иа 1-состояния в (1+1) означает 10 увеличение содержимого счетчика адреса на единицу. Символами MV обозначены различные такты работы устройства.

На временных диаграммах (фиг. 6) показана работа устройства в случае, когда не- 15 обходимо записать в регистр возврата адрес некоторой микрокоманды.

В случае (а) в регистре 3 возврата про- исходит запись адреса микрокоманды при обращении к подпрограмме. В случае (б) в 20 регистре 3 возврата происходит запись адреса микрокоманды при переходе к обработке прерывания.

Нумерация, используемая на временных диаграммах, соответствует нумерации 25 элементов на фиг. 1. Символами К, i, (l+ty, J обозначены различные состояния счетчика 4 адреса и регистра 3 возврата, причем символом jnn обозначен адрес микрокоманды, которая является начальной и некоторой 30 подпрограмме, а символом Пр -- начальная микрокоманда подпрограммы обработки прерывания. Символами t-jA/; 1.1 обозначены различные такты работы устройства.

Принцип кодирования микрокоманд ус- 35 тройства косвенный, т.е. в коде микрокоманд имеются дополнительные поля, которые модифицируют функции управления, содержащиеся в других полях микрокоманды. Таким модифицирующим полем в 40 данной системе микрокоманд является поле формата. Поле формата кодируется двумя разрядами (выход 2.1 регистра 2 микрокоманд). Имеются четыре формата микрокоманд, из которых 4-й формат не 45 используется:

формат 0 (ФОмк) - операционный, т.е. по этой микрокоманде выполняется некоторая совокупность микроопераций, определяемая содержанием операционной части 50 микрокоманды;

формат 1 (Ф1мк) - безусловный переход. Формат используется для формирова ния адреса следующей микрокоманды, который записан в коде микрокоманды пер- 55 вого формата;

формат 2 (Ф2мк) - условный переход. В коде микрокоманды записаны младшие разряды адресов следующих микрокоманд, переход к выполнению которых зависит от

значения логического условия, определяемого текущей микрокомандой.

Рассмотрим подробнее структуру полей различных форматов микрокоманд.

Во всех форматах микрокоманд присутствуют однобитовые поля:

РПР - разрешение прерывания (выход 2.10 регистра 2), при наличии сигнала единицы в этом поле микрокоманды осуществляется проверка наличия прерывания в конце выполнения микрокоманды;

ВЗВ - возврат (выход 2.2 регистра 2), при наличии сигнала единицы в этом поле микрокоманды осуществляется запоминание адреса микрокоманды, к выполнению которой следует перейти после выполнения некоторой подпрограммы;

КК - конец команды (выход 2.3 регистра 2), при наличии единицы в этом поле микро- команды осуществляется переход к выполнению новой команды, адрес начальной микрокоманды которой поступает в устроит ство извне;

ВА - внешняя адресация (выход 2.4 регистра 2), при наличии единицы в этом поле происходит подстановка адресов микрокоманд в устройство извне от некоторых внешних органов программного управления.

Группы выходов 2.5-2.7 регистра 2 для нулевого формата микрокоманд являются операционными, и коды, записанные в них, выдаются во внешние устройства.

КЛУ - код логического условия (группа выходов .2.5 регистра 2). Во втором формате микрокоманды в разрядах, поступающих на группу выходов 2,5 регистра 2, записывается код, определяющий, значение какого логического условия следует учитывать при выполнении условного.перехода.

В первом формате микрокоманд значение этих разрядов безразлично.

В разрядах микрокоманды, поступающих на группы выходов 2.6 и 2.7, в первом фронте микрокоманд записывается адрес, следующей микрокоманды. Во втором формате микрокоманд в этих разрядах записываются младшие разряды адресов двух микрокоманд, считывание которых зависит от выполнения проверяемого условия перехода. Разряды, поступающие на группу 2.8 регистра 2, для всех форматов микрокоманд являются операционными и выдаются во внешние устройства обработки.

В двухбитово.м поле, считываемом с группы 2.9 выходов регистра 2, Записывается код управления (КУ) работой мультиплексора 6 выбора. Запись в этом поле кода двойки свидетельствует о возврате к микро- команде, адрес которой был записан в регистре 3 возврата. Запись кода единицы означает подстановку некоторого адресе), выдаваемого формирователем 19 константы. Запись нулевого кода определяет считывание адреса следующей микрокоманды из счетчика 4 адреса.

Рассмотрим назначение элементов предлагаемого устройства.

Блок 1 памяти предназначен для хранения микрокоманд.

Регистр 2 микрокоманд предназначен для записи микрокоманды, считываемой из блока 1 памяти по заданному адресу.

Регистр 3 возврата предназначен для записи адреса микрокоманды, по которому следует осуществить переход после выполнения некоторой подпрограммы или обработки прерывания,

Счетчик 4 адреса предназначен для формирования адреса микрокоманды, кото- рая должна поступить на обработку.

Мультиплексор 5 адреса предназначен для подачи на группу D-входов счетчика ад-- реса 4 адреса очередной микрокоманды в зависимости от режима работы устройства.

Мультиплексор б выбора предназначен для подачи на группу входов блока 1 памяти адреса считываемой микрокоманды в зависимости от сигнала на его адресных входах.

Мультиплексор 7 логических условий предназначен для передачи в блок 8 управления значения заданного логического условия..

Блок 8 управления предназначен Зря управления мультиплексором 5 адреса.

На информационные входы 35.1-35.3 блока 8 управления поступает унитарный код. Если на управляющих входах 40,43,28, 25.1,2.3 и 2.4 блока 8 управления единичные сигналы отсутствуют, то пятый 49 и шестой 50 элементы И заперты нулевыми сигналами, присутствующими на входе 2.3 и выходе элемента ИЛИ 51.2 блока 8 управления. На втором. - пятом входах шифратора 44 единичные сигналы отсутствуют. На выходе элемента ИЛИ 51.1 формируется .нулевой сигнал, отпирающий первый-четвертый эле- менты И . Пусть сигнал единицы подан на первый информационный вход 35.1. Тогда на выходе первого элемента И 45 форми- руется единичный сигнал, поступающий на первый вход шифратора 44. На выходах вто- рого-четвертого элементов И 46-48, а сяедо- вательно, на шестом-восьмом входах шифратора 44 единичные сигналы отеутет- вуют. На выходе 36 блока 8 формируется двоичный код нуля.

Если сигнал единицы поступает на второй информационный вход 35.2 блока 8 управления, то сигнал единицы формируется

только на выходе второго элемента И 46. Это приводит к тому, что на выходе 36 блока 8 формируется двоичный код пяти.

Если сигнал единицы поступает на третий информационный вход 35.3 блока 8 управления, то запираются первый 45 и второй 46 элементы И и на выходах отсутствуют единичные сигналы. Сигналы на выходах третьего 47 и четвертого 48 элементов И в этом случае определяются сигналом, поступившим на вход 34 блока 8 управления.

Пусть на выходе 34 блока 8 управления присутствует нулевой сигнал, тогда четвертый элемент И 48 запирается, а на выходе третьего элемента И 47 появляется единичный сигнал, что приводит к формированию на выходе 36 блока 8 двоичного кода шести. ; При поступлении на вход 34 блока 8 управления сигнала единицы запирается третий элемент И 47 и открывается четвертый элемент И 48. Следовательно, сигнал единицы присутствует на восьмом-входе шифратора 44 и на выходе 36 блока 8 сформирован двоичный код семи.

Если единичный сигнал поступает хотя бы на один из входов 40, 43, 28, 2.3, 25.1 и 2.4 блока 8 управления, то на выходе элемента ИЛИ 51.1 появляется единичный сигнал, Это приводит к запиранию первого-четвертого элементов И 45-48, на выходах которых независимо от сигналов, поступивших на информационные входы 35.1-35,3 и вход 34 блока 8 управления, также отсутствуют единичные сигналы. Сигналы на втором-пятом входах шифратора 44, а следовательно, и код на выходе 36 блока 8 управления зависят от сигналов, поступивших на управляющие входы 40, 43, 28, 2,3, 2.4 и 25.1 блока 8 управления. Причем если единичный сигнал присутствует на входе 40 блока 8, который поступает на пятый вход шифратора 44, то на входах 28, 43, 2.3, 2.4 и 25.1 сигналы единицы должны отсутствовать. В этом случае только на пятый вход шифратора 44 подан единичный сигнал. Это приводит к формированию на выходе 36 блока 8 управления двоичного кода четверки. При поступлении единичного сигнала на .входы 43, 28, 2,3 или 2.4 и. 25.1 блока 8 управления на его входе 40 обязательно должен присутствовать нулевой сигнал.

Если единичный сигнал присутствует на входе 28 или 43 блока 8 управления, то независимо от сигналов на его входах 2.3, 2.4 и 25.1 сигнал единицы присутствует только на четвертом входе дешифратора 44, так как пятый и шестой элементы И 48 и 50 запираются единичным сигналом с выхода элемента ИЛИ 51.3. На выходе 36 блока 8 формируется двоичный код тройки. Если на

входе 28 или 43 блока 8 управления единичный сигнал отсутствует, то при поступпле- нии на вход 2.3 блока 8 единичного сигнала он проходит на выходе пятого элемента И 49, а шестой элемент И 50 запирает. На выходе 36 блока 8 управления сформирован двоичный код двойки. Если сигнал единицы присутствует только на выходе элемента ИЛИ 51.2, а на выходе элемента ИЛИ 51.3 и входе 2.3 блока 8 отсутствует, то отпирается шестой элемент И 50, единичный сигнал с выхода которого поступает на второй вход шифратора 44. На выходе 36 блока 8 управления формируется двоичный код единицы.

Пульт 9 управления предназначен для формирования адреса начальной микрокоманды и выдачи управляющего сигнала на его считывание.

,. Группа 10 элементов И-ИЛИ предназначена для формирования адреса микроко- -манды в режиме прерывания и по команде с пульта 9 управления. При наличии единичного (нулевого) сигнала на выходе 43 пульта 9 управления через группу 10 элементов И-ИЛИ передается начальный адрес с выхо- да 42 пульта 9 (выхода шифраторами).

Первый элемент ИЛИ 11 предназначен для формирования сигнала, управляющего работой счетчика 4 адреса.

Второй элемент ИЛИ 12 предназначен для формирования управляющего сигнала в режиме прерывания.

Третий элемент ИЛИ 13 предназначен для управления записью в регистр 3 возврата.

Первый элемент И 14 предназначен для формирования сигнала перехода к обработке микропрограммы прерывания.

Элемент И-ИЛИ 15 предназначен для управления поступлением сигналов на счет- чный вход счетчика 4 адреса.

Второй элемент И 16 предназначен для формирования сигнала записи в счетчик 4 адреса.

Третий элемент И 17 предназначен для формирования сигнала записи в регистр 3 возврата,

Генератор 18 импульсов предназначен для синхронизации работы устройства,

Формирователь 19 константы предназ- начен для формирования начального адреса некоторой стандартной микропрограммы.

Шифратор 20 предназначен для формирования адреса микрокоманды при поступлении сигнала на прерывание извне.

Дешифратор 21 предназначен для формирования унитарных информационных сигналов в зависимости от формата считываемой из регистра 2 микрокоманды.

Группа 22 элементов И предназначена для выдачи во внешние устройства операционной части микрокоманд в зависимости от их формата.

Блок 38 приема информации обеспечивает запись, хранение и выдачу сигналов, поступающих в устройство извне по входам 39.1-39.4.

Регистр 61 служит для запоминания и выдачи на выходы 24 блока 38 сигналов прерывания, поступающих на вход 39.2 устройства. Запись сигналов прерывания в регистр 61 осуществляется по заднему фронту импульса с выхода 18.3 генератора 18. Сброс регистра 61 в исходное состояние производится по заднему фронту сигнала на выходе 2.10 регистра 2. Импульс сброса формирует одновибратор 67,

Регистр 62 служит для запоминания и выдачи на выход 27 блока 38 сигналов логических условий, поступающих на вход 39.4 устройства. Запись информации в регистр

62осуществляется по заднему фронту импульса с выхода 18.1 генератора 18.

Регистр 63 предназначен для приема, хранения и выдачи на выход 26 блока 38 кода операции, поступающего на вход 39.1 устройства. Запись информации в регистр

63осуществляется по заднему фронту импульса с выхода 18.1 генератора 18 при наличии сигнала на выходе 2.3 регистра 2. Сигнал записи формирует элемент И 66.

Регистр 64 предназначен для записи, хранения и выдачи на выход 25 блока 38 внешнего адреса, поступающего на вход 39.3 устройства. Запись информации в регистр 64 осуществляется по заднему фронту импульса с выхода 18.1 генератора 18, если отсутствует единичный сигнал на выходе 35.2 дешифратора 35, при наличии сигналов на входе 68 группы входов 39.3 или выходе 2.4 регистра 2. Сигнал записи информации в регистр 64 формирует элемент И-ИЛИ 65. Сигналы записи в регистры 61-64 поступают на группу 33 выходов. По заднему фронту этих сигналов внешняя система снимает информацию с соответствующих входов 39.1- 39.4.

Устройство работает следующим образом.

В исходном состоянии все переключатели 60узлов 55 коммутации пульта 9 управления находятся в нормально замкнутом (верхнем) положении.

После включения питания все элементы памяти устройства устанавливаются в начальное (нулевое) состояние (цепи установки исходного состояния на фиг. 1-4 условно не показаны). В исходном (верхнем) положении переключателей 60 на выходы узлов

56.1-55.П+1 поступают сигналы логического нуля. На выходах 18,1-18.3 генератора 18 импульсы отсутствуют. На выходе 31 формирователя 19 константы сформирован адрес некоторой стандартной микропрограммы.

Перед запуском устройства на узлах 55.2-55.П+1 коммутации с помощью переключателей 60 пульта 9 управления набирается адрес начальной микрокоманды, который с группы 42 информационных вы- ходов пульта 9 поступает на группу 10 элементов И-ИЛИ и далее (после появления сигнала на выходе 43) - на третью группу D-входов мультиплексора 5 адреса. Для запуска устройства переводится в нижнее по- ложение переключатель 60 узла 55.1 пульта 9 управления. Единичный сигнал подается на управляющий вход 41 генератора 18 импульсов и запускает его.

На входы 18.1 и 18.3 пульта 9 управле- ния поступают сдвинутые относительно друг друга тактовые импульсы. По переднему фронту импульса, поступающего с входа 18.1 на С-вход триггера 53 пульта 9 управления, триггер 53 устанавливается в единиц- ное состояние, так как на его D-входё находится единичный сигнал с выхода формирователя 52 единицы. По переднему фронту сигнала с единичного выхода триггера 53 устанавливается в единичное Состоя- ние триггера 54, на D-входе которого также находится сигнал логической единицы с выхода формирователя 52.

На выходах регистра 2 микрокоманд единичные сигналы отсутствующи дешифра- тор 21 формирует единичный сигнал только на выходе 35.1.

Единичный сигнал с управляющего выхода 43 пульта 9 управления поступает на управляющие входы группы 10 элементов И-ИЛИ и разрешает передачу кода с выхода 42 пульта 9 на вход D 3 мультиплексора 5Н, а также на вход блока 8 управления.

На выходе 36 блока б.управления в соответствии с сигналами поступившими на его первый-седьмой управляющие входы 34, 40, 43, 28, 2.3, 2.4 и 25.1 и на информационные входы 35.1-35.3, формируется код тройки, который поступает на группу адресных входов мультиплексора 5 адреса и труп- пу входов первого элемента ИЛИ 11.

Единичный сигнал с выхода первого элемента ИЛИ 11 открывает второй элемент И 16 и запирает первый элемент И элемента И-ИЛИ 15, На выход мультиплексора 5 ад- реса поступает адрес микрокоманды с его третьей группы D-входов. По заднему фронту импульса, поступившего с выхода 18.2 генератора 18 импульсов через элемент И 16 на С-вход счетчика 4 адреса, адрес с

выхода мультиплексора 5 записывается в счетчик 4 адреса. Так как на адресные входы мультиплексора 6 выбора подан нулевой код, то на его выход поступает адрес с выхода 30 счетчика 4 адреса. По этому адресу из блока 1 памяти считываются микрокоманды.

Разряды микрокоманды с выхода блока 1 памяти поступают на D-вход регистра 2 микрокоманд. По переднему фронту сигнала с третьего выхода 18.3 генератора 18 импульсов триггер 54 пульта управления устанавливается в нулевое состояние и с выхода 43 пульта 9 управления снимается единичный сигнал.

По заднему фронту импульса с третьего выхода 18.3 генератора 18 импульсов считанная из блока 1 памяти микрокоманда записывается в регистр 2 микрокоманд. Разряды микрокоманды, определяющие ее формат, с управляющего выхода 2.1 регист- ра 2 микрокоманд поступают на вход дешифратора 21, на выходе 35 которого сформировывается унитарный код. поступающий на группу информационных входов блока 8 управления. Сигнал с первого выхо- да 35.1 дешифратора 21 также поступает на управляющие входы группы 22 элементов И.

В зависимости от формата считываемой микрокоманды и от значений ее управляющих разрядов возможны следующие режимы работы устройства: линейный режим, режим внешней адресации, режим формирования адреса по концу команды, режим прерывания, режим возврата, режим безусловного перехода, режим условного перехода,

В линейном режиме адреса выполняемых микрокоманд увеличиваются на единицу относительно адреса предыдущей микрокоманды. Этот режим осуществляется при нулевом фронте микрокоманды и только при условии, что на выходах2.2-2.4 и группе 2.9 выходов регистра 2 микрокоманд, входе 25.1 блока 8 управления и на выходе 28 элемента И 14 присутствуют нулевые сигналы. Значения остальных разрядов микрокоманды могут быть произвольными.

Единичный сигнал с первого выхода 35.1 дешифратора 21 поступает на группу 22 элементов И и на первый вход элемента И 45 блока 8 управления. На выходе 36 блока 8 формируется нулевой код, так как на остальных входах блока 8 управления единичные сигналы отсутствуют. Код с выхода 36 блока 8 поступает на группу адресных входов мультиплексора 5 адреса и на группу входов первого элемента ИЛИ 11, Нулевой сигнал с выхода первого элемента ИЛИ 11 запирает первый элемент И 16 и отпирает

первый элемент И элемента И-ИЛИ 15. Информация с групп 2.5-2.7 выходов регистра 2 микрокоманд через открытую группу 22 элементов И и с выхода 2.8 поступает на первую-четвертую группы выходов 37, 38, 5 39 и 2.8 устройства.

Импульс с первого выхода 18.1 генератора 18 импульсов не проходит на счетный вход счетчика 4 адреса, так как второй и третий элементы И элемента И-ИЛИ 15 за- 10 крыты нулевым сигналом с выхода 2.2 регистра 2 микрокоманд и с выхода 28 первого элемента И 14 соответственно.

Этот импульс при поступлении на первый вход 18.1 пульта 9 управления не изме- 15 няет его состояние. Импульс с второго выхода 18.2 генератора 18 импульсов через открытый первый элемент И элемента И- ИЛИ 15 поступает на счетный вход счетчика 4 адреса и по заднему фронту увеличивает 20 содержимое счетчика 4 на единицу. На С- входы счетчика 4 адреса и регистра 3 возврата импульсы не поступают, так как второй и третий элементы И 16 и 17 заперты.

Адрес с выхода 30 счетчика адреса че- 25 рез мультиплексор 6 выбора, на группу адресных входов которого подан нулевой код с выхода 2.9 регистра 2 микрокоманд, поступает на вход блока 1 памяти. На выходе блока 1 памяти появляется новая микроко- 30 манда, разряды которой записываются в регистр 2 микрокоманд по заднему фронту импульса с третьего выхода 18.3 генератора 18 импульсов (фиг. 5, такт III). До тех пор, пока считываемые микрокоманды имеют ну- 35 левой формат, а на выходах 2.2-2.4 и 2. регистра 2 микрокоманд и выходе 28 элемента И 14 отсутствуют единичные сигналы, устройство работает в линейном режиме.

Для работы устройства в режиме внеш- 40 ней адресации необходимо наличие сигнала единицы на выходе 2.4 регистра 2 микрокоманд либо на выходе 25.1 группы 25 выходов блока 38. Кроме того, должны отсутствовать единичные сигналы на выхо- 45 дах 2.3 и 2.9 регистра 2 микрокоманд и выходе 28 элемента И 14. Формат микрокоманды и сигналы на остальных выходах регистра 2 микрокоманд могут быть произвольными. В соответствии с указан- 50 ным на выходе 36 блока 8 управления формируется двоичный код единицы. На D-вход счетчика 4 адреса поступает адрес с первой группы D-входов мультиплексора 5 адреса. В этом режиме и во всех остальных сигнал 55 единицы с выхода первого элемента ИЛ И 11 открывает второй элемент И 16 и закрывает первый элемент И элемента И-ИЛИ 15.

Характерны следующие два случая.

В первом случае на выходе 2.2 регистра 2 микрокоманд присутствует единичный сигнал. Этот сигнал поступает на второй вход второго элемента И элемента И-ИЛИ 15 и через третий элемент ИЛИ 13 на второй вход третьего элемента И 17. При поступлении с первого выхода 18.1 генератора 18 импульсов сигнала на первый вход второго элемента И элемента И-ИЛИ 16 на его выходе формируется единичный сигнал, который поступает на счетный вход счетчика 4 адреса и увеличивает его содержимое на единицу (фиг. 6а, такт 1.1). По заднему фронту сигнала с второго выхода 18.2 генератора 18 импульсов в регистр 3 возврата переписывается адрес, хранившийся в счетчике 4, а в счетчик 4 адреса записывается адресе выхода мультиплексора 5 адреса (фиг. 6а, такт II).

Во втором случае на выходе 2.2 регистра 2 микрокоманд отсутствует сигнал единицы. Это приводит к запиранию второго элемента И-ИЛИ 15 и третьего элемента И 17. Импульс с первого выхода 18.1 генератора 18 импульсов не изменяет состояние счетчика 4 адреса.

По заднему фронту сигнала с второго выхода 18.2 генератора 18 импульсов адрес, поступающий на D-вход счетчика 4 адреса, записывается в счетчик (фиг. 5, такты I. II, IV). Считывание новой микрокоманды аналогично.

Достоинством этого режима является возможность модификации выполняемой программы за счет подстановки адресов микрокоманд извне с группы выходов 25 блока 38 при наличии необходимых управляющих сигналов на выходе 2.4 регистра 2 микрокоманд либо на выходе 25.1 группы 25 выходов блока 38.

В режиме формирования адреса по концу команды на выходе 2.3 регистра 2 микрокоманд должен присутствовать единичный сигнал. При этом на выходах 2.2 и 2.9 регистра 2 микрокоманд и на выходе 28 элемента И 14 единичные сигналы отсутствуют. Формат микрокоманды и значения остальных разрядов микрокоманды могут быть произвольными. На выходе 36 блока 8 управления формируется двоичный код двойки. По заднему фронту импульса с второго выхода 18.2 генератора 18 импульсов в счетчик 4 адреса записывается адрес, который проходит на выход мультиплексора 5 адреса с его второй группы D-входов (фиг. 5, такты I, II, IV). Считывание микрокоманды и ее запись в регистр 2 микрокоманд происходит так же, как и в линейном режиме.

В режиме прерывания на выходе 2.10 регистра 2 должен присутствовать единичный сигнал, который открывает первый элемент И 14 и разрешает прерывание. На группе выходов 2.9 нулевой код. Для осуществления режима прерывания на первую группу 24 выходов блока 38 должен поступить сигнал на прерывание от одного из внешних устройств. На выходе шифратора 20 формируется адрес начальной микрокоманды обработки данного вида прерывания, который через группу 10 элементов И-ИЛИ (на выходе 43 присутствует нулевой сигнал) поступает на третью группу D-входов мультиплексора 5 адреса.

На выходе второго элемента ИЛИ 12 сформирован единичный сигнал, который через элемент И 14 поступает на пятый вход 28 блока 8 управления, а также через третий элемент ИЛИ 15 - на второй вход второго элемента И 17 и на вход третьего элемента И элемента И-ИЛИ 15. На выходе 35 блока 8 управления сформирован код тройки, при поступлении которого на адресные входы мультиплексора 5 адреса на его выход поступает адрес с его третьей группы D-вхо- дов.

По импульсу с первого выхода 18.1 гене- ратора 18 импульсов содержимое счетчика 14 увеличивается на единицу, По импульсу 18,2 код с выхода счетчика 4 переписывается в регистр 3 возврата, а адрес с выхода мультиплексора 5 записывается в счетчик 4 адреса (фиг. 66, такт IV). Считывание микрокоманды происходит так же, как и в линейном режиме,

В режиме возврата на вход блока Гпа- мяти подается адрес с выхода 32 регистра 3 возврата, куда он предварительно записывается по приведенному алгоритму. Для осуществления режима возврата необходимо, чтобы на выходе 2.9 регистра 2 микрокоманд . выдавался код двойки, а на управляющих входах 2.2-2.4 этого же регистра и выходе 28 элемента И 14, а также на выходе 25,1 блока 38 единичные сигналы отсутствовали. Формат микрокоманды и значения остальных ее разрядов могут быть произвольными. Сигналы с выхрда.2,9 реп/к стра 2 микрокоманд поступают на входы четвертого элемента ИЛИ 23 и адресные входы мультиплексора б выбора, на выход которого поступает адрес с выхода 32 регй- стра 3 возврата. Этот адрес поступает на вход блока 1 памяти и четвертую группу D-входов мультиплексора 5 адреса.

На выходе 40 четвертого элемента ИЛИ 23 появляется единичный сигнал, который поступает на четвертый вход блока 8 управления, На выходе 36 блока 8 управления сформирован код четверки, который поступает на адресные входы мультиплексора 5 адреса. На D-вход счетчика 4 адреса проходит адрес с четвертой группы D-входов мультиплексора адреса. По заднему фронту импульса с второго выхода 18.2 генератора 18 импульсов этого адрес записывается в счетчик 4 адреса (фиг. 5, такты 1,11,1V). Дальнейшие процессы аналогичны.

Режим безусловного перехода реализуется при первом формате микрокоманды. В разрядах микрокоманды, сигнал с которых поступает на выходы 2.6 и 2.7 регистры 2 микрокоманд, записывается адрес, по которому следует осуществить переход. В разрядах, поступающих на выход 2.5 регистра 2 микрокоманд, записывается произвольный код. На выходе 28 элемента И 14, на управляющих выходах 2.3 и 2.4, на выходе 25.1 группы выходов 25 блока 38 и на группе выходов 2.9 регистра 2 микрокоманд единичные сигналы должны отсутствовать. Значения остальных управляющих разрядов микрокоманды произвольные. При данном формате микрокоманды единичный сигнал появляется на втором выходе 35.2 дешифратора 21, который поступает на второй информационный вход блока 8 управления. Группа 22 элементов И запирается нулевым сигналом с первого выхода 35.1 дешифратора 21. На выходе 36 блока 8 управления сформирован код пяти. В результате на выходе мультиплексора 5 адреса проходит адрес с группы выходов 2.6 и 2,7 регистра 2 микрокоманд. В зависимости от значения сигнала на выходе 2.2 регистра 2 микрокоманд в этом режиме, как ив режиме внешней адресации, возможны два случая.

При наличии на выходе 2,2 регистра 2 единичного сигнала по сигналу с первого выхода 18.1 генератора 18 импульсов содержимое счетчика увеличивается на единицу. По заднему фронту с второго выхода 18.2 генератора 18 содержимое счетчика 4 адреса переписывается в регистр 3 возврата, а в счетчик 4 записывается адрес, поступающий с выхода мультиплексора 5 адреса.

Если на выходе 2.2 регистра 2 микрокоманд единичный сигнал отсутствует, то импульс с первого выхода 18.1 генератора 18 импульсов никак не отражается на работе устройства, а по заднему фронту импульса с второго выхода 18.2 генератора 18 импульсов изменяется содержимое счетчика. Считывание микрокоманды происходит так же, как в линейном режиме.

Режим условного перехода реализуется при втором формате микрокоманды. В разрядах микрокоманды, которые выдаются на выходах 2.6 и 2.7 регистра 2 микрокоманды, записываются младшие разряды адреса следующей микрокоманды. Старшие разряды адреса поступают из счетчик;) 4 адреса.

На группе 2.5 выходов регистра 2 микрокоманд содержится код логического условия, от значения которого зависит выбор адреса условного перехода. На выходе 28 элемента И 14, на управляющих выходах 2.3, 2.4, 2.10 и на группе выходов 2.9 регистра 2 микрокоманд, а также на выходе 25.1 группы выходов 25 блока 38 единичные сигналы должны отсутствовать. Значения остальных управляющих разрядов микрокоманды про- извольные.

При втором формате микрокоманды единичный сигнал появляется на третьем выходе 35.3 дешифратора 21, В зависимости от значения сигнала на третьем входе 34 блока 8 управления на его выходе 36 формируется либо код шести, либо код семи.

Следовательно, при невыполнении ло- гического условия (на вход 34 блока 8 управления поступает нулевой сигнал) на выход .мультиплексора 5 адреса проходит адрес с его шестой группы D-входов.

При выполнении логического условия на выход мультиплексора 5 адреса проходит адрес с его седьмой группы D-входов.

Дальнейшие процессы, проводящие к изменению содержимого счетчика 4 адреса при различных сигналах на выходе 2.2 регистра 2 микрокоманд и считыванию микрокоманды, аналогичны процессам, происходящим при режиме безусловного перехода,

Если на группе выходов 2,9 регистра 2 сформирован код единицы, то из блока 1 памяти считывается микрокоманда по адре- су, выработанному формирователем 19 константы. Так же, как при режиме возврата, код с выхода мультиплексора 6 выбора через четвертую группу D-входов мультиплексора 5 записывается в счетчик 4 адреса по заднему фронту импульса с выхода 18.2 генератора 18 импульсов. При этом единичные сигналы на входах 2.3, 2.4, 25.1 и 28 блока 8 управления должны отсутствовать.

Фор мула изобретения

1. Микропрограммное устройство управления, содержащее блок памяти, регистр микрокоманд, регистр возврата, счетчик адреса, первый элемент ИЛИ, первый - третий элементы И, группу элементов И, генератор импульсов и дешифратор, причем группа выходов блока памяти соединена с группой информационных входов регистра микрокоманд, группа управляющих выходов которого соединена с группой входов дешифратора, первый выход дешифратора соединен с первыми входами элементов И группы, первый выход генератора импульсов - с первым входом второго элемента И, выход которого соединен с синхронизирующим входом счетчика адреса, первый - третий выходы совмещенного поля регистра микрокоманд соединены соответственно с вторыми входами с первого по третий элементов И группы, о т л и чаю - щ е е с я тем, что, с целью расширения области применения путем обеспечения режима прерывания, режима внешней адресации и механизма возврата к выполнению микроподпрограмм, оно дополнительно содержит блок управления, блок приема информации, мультиплексоры адреса, выбора и логических условий, второй - четвертый элементы ИЛИ. элемент И-ИЛИ, группу элементов И-ИЛИ, формирователь константы, шифратор, пульт управления, причем группа выходов блока управления соединена с группой входов первого элемента ИЛИ и группой адресных входов мультиплексора адреса, группа выходов которого соединена с группой D-входов счетчика адреса.первая группа выходов блока приема информации соединена с группой входов шифратора, группа выходов которого соединена с первой группой входов элементов И-ИЛИ группы и входами второго элемента ИЛИ, вторая группа выходов блока приема информации соединена с первой группой D-входрв мультиплексора адреса, а первый выход второй группы выходов блока приема информации

-с первым входом блока управления, третья группа выходов блока приема информации

-со второй группой D-входов мультиплексора адреса, первый выход пульта управления

-с входом запуска генератора импульсов, группа информационых выходов пульта управления -с второй группой входов элементов И-ИЛИ группы, группа выходов которых соединена с третьей группой D-входов мультиплексора адреса, второй выход пульта управления соединен с вторым входом блока управления, прямым и инверсным входами элементов И-ИЛИ группы, выход первого элемента ИЛИ соединен с вторым входом второго элемента И и инверсным входом элемента И-ИЛИ, выход второго элемента ИЛИ соединен с первым входом первого элемента И/четвертая группа выходов блока приема информации -с информационными D-входами мультиплексора логических условий, выход которого соединен с третьим входом блока управления, пятая группа выходов блока приема информации является группой сигнальных выходов устройства, второй выход генератора импульсов соединен с первым входом пульта управления и первыми вторым прямыми входами элемента И-ИЛИ, первый выход генератора импульсов - с первым входом второго элемента И, третьим прямым входом элемента И-ИЛИ, третий выход генератора импульсов - с С-входом регистра микрокоманд и вторым входом пульта управления, первый управляющий выход регистра микрокоманд соединен с четвертым прямым входом элемента И-ИЛИ и первым входом третьего элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И, выход третьего элемента И - с С-входом регистра возврата, группа выходов мультиплексора выбора - с четвертой группой D-входов мультиплексора адреса и группой адресных входов блока памяти, первый выход совмещенного поля регистра микрокоманд - с адресным, входом мультиплексора логине- ских условий, первая -третья группы выходов элементов И группы являются одноименными группами выходов устройства, второй выход совмещенного поля регистра микрокоманд соединен с пятой и шестой группами D-входов мультиплексора адреса, третий выход совмещенного поля регистра микрокоманд - с пятой и седьмой группами D-входов мультиплексора адреса, выход поля микроопераций регистра микро- команд подключен к четвертой группе выходов устройства, выход поля управления адресом регистра микрокоманд соединен с группой адресных входов мультиплексора выбора и группой входов четвертого эле- мента ИЛИ, выход которого соединен с четвертым входом блока управления, выход первого элемента И соединен с вторым входом третьего элемента ИЛИ, с пятым прямым входом элемента -и с пятым входом блока управления, второй и третий управляющие выходы регистра микрокоманд соединены соответственно с шестым и седьмым входами олока управления, выход элемента И-ИЛИ - со счетным входом счет- чика адреса, группа выходов которого соединена с группой D-входов регистра возврата и первой группой D-входов мультиплексора выбора, первая и вторая подгруппы группы выходов счетчика адреса соединены соответственно с шестой и седьмой группами D-входов мультиплексора адреса, группа выходов дешифратора - с группой информационных входов блока управления, группа выходов формирователя констант - с второй группой D-входов мультиплексора выбора, группа выходов регистра возврата - с третьей группой D-входсш мультиплексора выбора, четвертый управляющий выход регистра микрокоманд - с вторым входом первого элемента И, второй выход дешифратора, второй - четвертый управляющие выходы регистра микрокоманд соединены соответственно с первого по четвертый выходами устройства, группы

входов кода операции, кода прерывания, к с да внешнего адреса и кода логических услс вий соединены соответственно с первой четвертой группами информационных вхо дов блока приема информации, первый и третий выходы генератора импульсов соединены соответственно с первым и вторым синхровходзми блока приема информации, группа управляющих входов которого образована вторым выходом дешифратора, а также третьим и четвертым управляющими выходами регистра микрокоманд, четвертый выход регистра микрокоманд соединен с вторым входом разрешения прерывания блока приема информации.

2, Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что блок управления содержит шифратор, с первого по шестой элементы И, с первого по третий элементы ИЛИ, первый информационный вход группы входов блока управления соединен с первым входом первого элемента И, выход которого соединен с первым входом шифратора, второй информационный вход группы входов блока управления - с первым входом второго элемента И, выход которого соединен с вторым входом шифратора, третий информаци- онный вход группы входов блока управления соединен с первыми входами третьего и четвертого элементов И, выход третьего элемента И - с третьим входом шифратора, выход четвертого элемента И - с четвертым входом шифратора, выход первого элемента ИЛИ - с вторым инверсным входом с первого по четвертый элементов И, третий вход блока управления - с третьим инверсным входом третьего элемента И и третьим прямым входом четвертого элемента И, четвертый вход блока управления - с первым входом первого элемента ИЛИ и пятым входом шифратора, пятый вход блока управления - с первым входом третьего элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ, первыми инверсными входами пятого и шестого элементов И и шестым входом шифра- тора, шестой вход блока управления соединен с третьим входом первого элемента ИЛИ, вторым входом пятого элемента И и вторым инверсным входом шестого элемента И, шестой вход блока управления - с первым входом второго элемента ИЛИ, выход которого соединен с четвертым входом первого элемента ИЛИ и третьим входом шестого элемента И, выход пятого элемента И - с седьмым входом шифратора, выход шестого элемента И - с восьмым входом шифратора, первый вход блока управления - с вторым входом второго элемента

ИЛИ, второй вход блока управления - с вто- шифратора является выходом блока управ- рым входом третьего элемента ИЛИ, выход ления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении микропрограммных устройств управления ЭВМ и вычислительных систем, например специализированных процессоров квазиэлектронных и электронных АТС. Цель изобретения состоит в расширении области применения устройства за счет расширения числа реализуемых режимов микропрограммного управления благодаря обеспечению возможности прерывания микропрограммы от внешних и внутренних источников; обеспечению возможности оперативной модификаций микропрограмм на основе изменения порядка следования микрокоманд; реализации механизма возврата и выполнения микроподпрограмм. Микропрограммное устройство управления, состоящее из блока памяти, регистра микрокоманд, регистра возврата, счетчика адреса, элементов И, ИЛИ, дополнительно содержит блок, управления, мультиплексоры адреса, выбора и логических условий, элементы ИЛИ, И- ИЛИ, формирователь константы., шифратор, пульт управления. В зависимости от формата считываемой микрокоманды и от значения управляющих разрядов возможны следующие режимы работы устройства; линейный режим, режим внешней адресации, режим формирования адреса по концу команды, режим прерывания, режим возврата, режим безусловного перехода, режим условного перехода. 1 з.п.ф-лы, 7 ил.

ш л ли ш , Ъ Ъ Ъ Ъ .у

5

Г

дивимо

г±Ж

b&t.. : .

ЩигЗ

: я

FT

26 #/1 «Ш

VutJ

394

Фиг .7

| Микропрограммное устройство управления | 1984 |

|

SU1183964A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Зейс Э | |||

| Синтез и оптимизация программы с использованием Р-функций | |||

| IEEE Transaction Computers, 1982, 31, № 1, с | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосов В.Е | |||

| и Мелехин В.Ф, Проектирование узлов и систем автоматикой вычислительной техники | |||

| Л.: Энергоатомйздат, 1983, с | |||

| Способ очищения сернокислого глинозема от железа | 1920 |

|

SU47A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-02-28—Публикация

1990-02-28—Подача