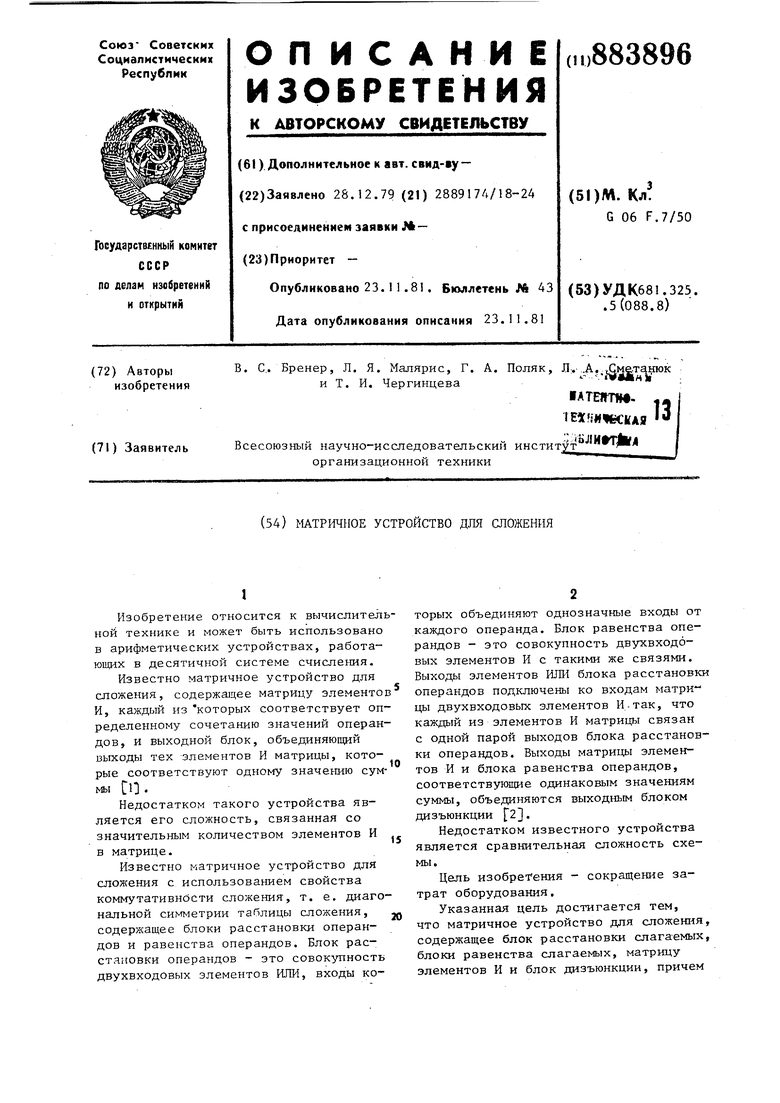

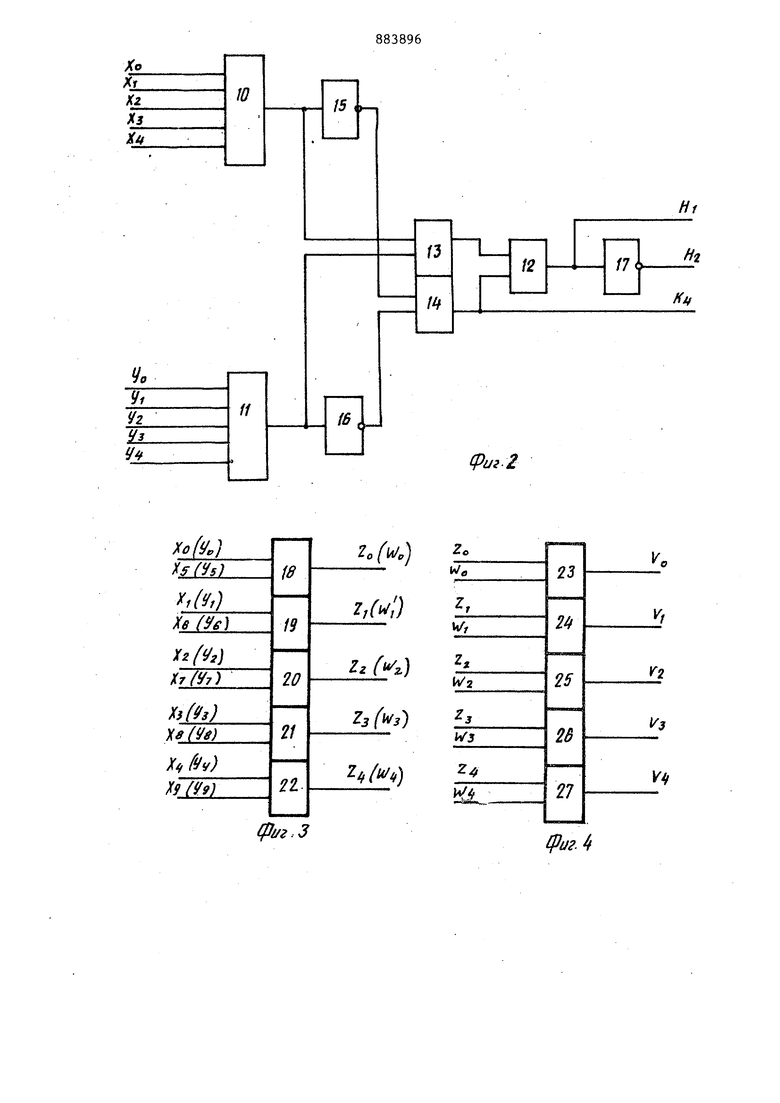

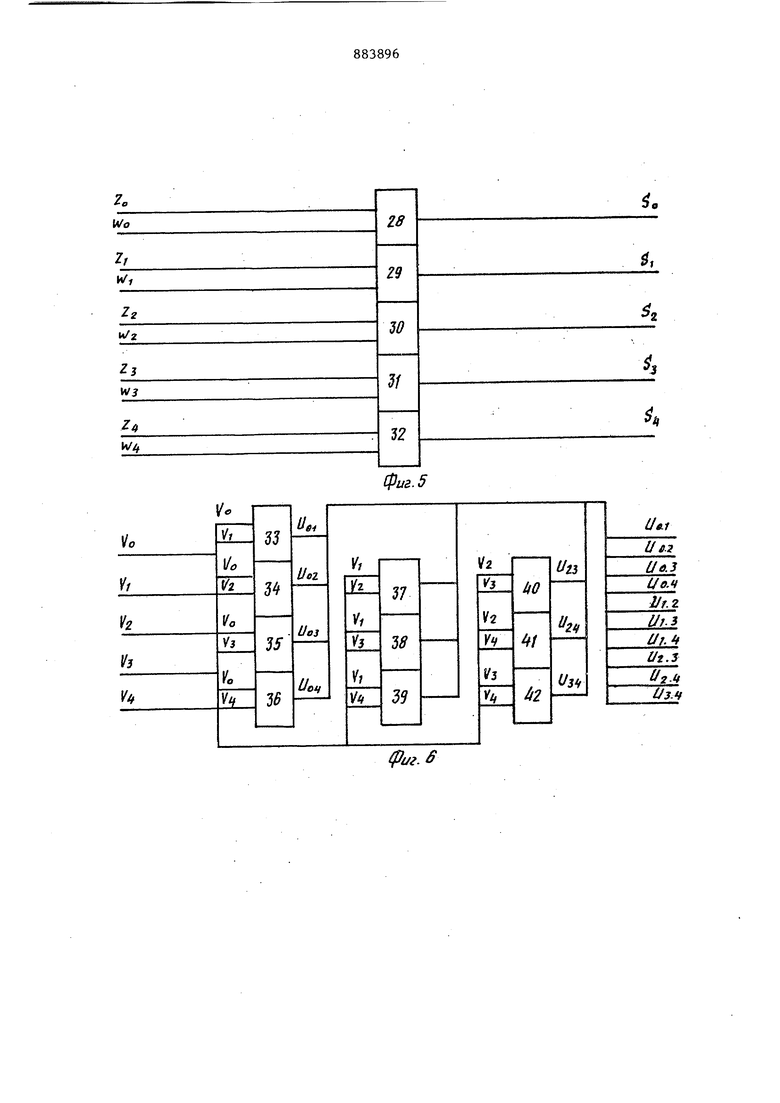

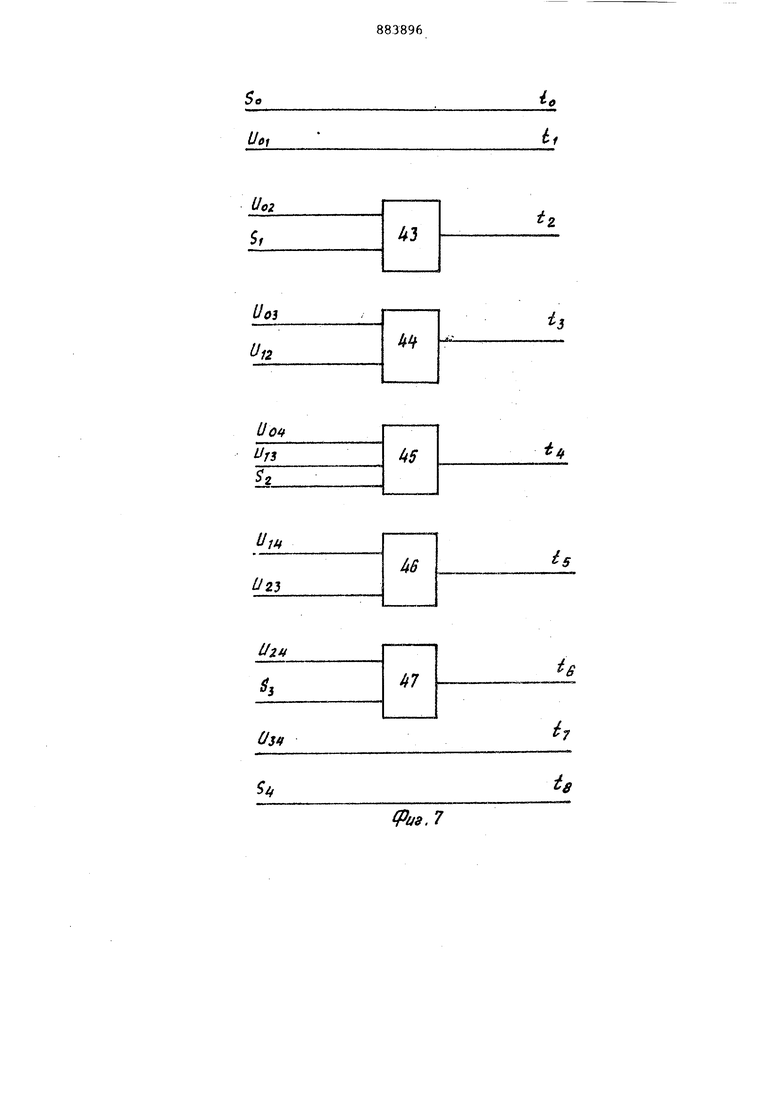

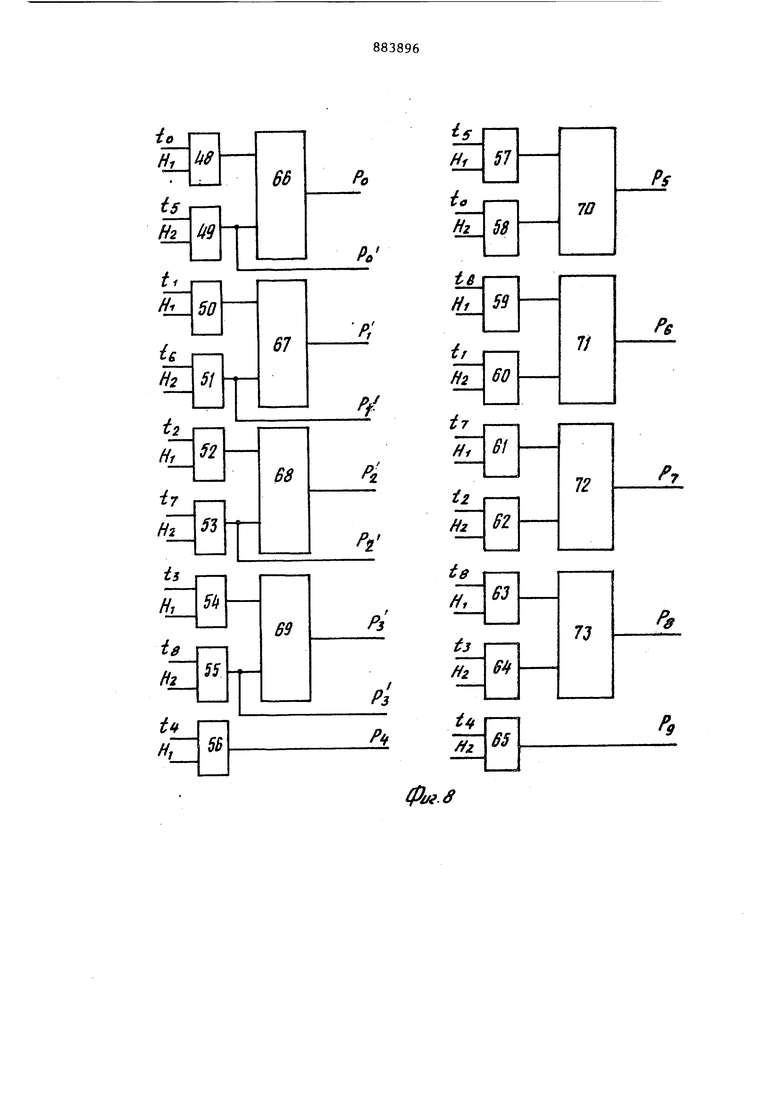

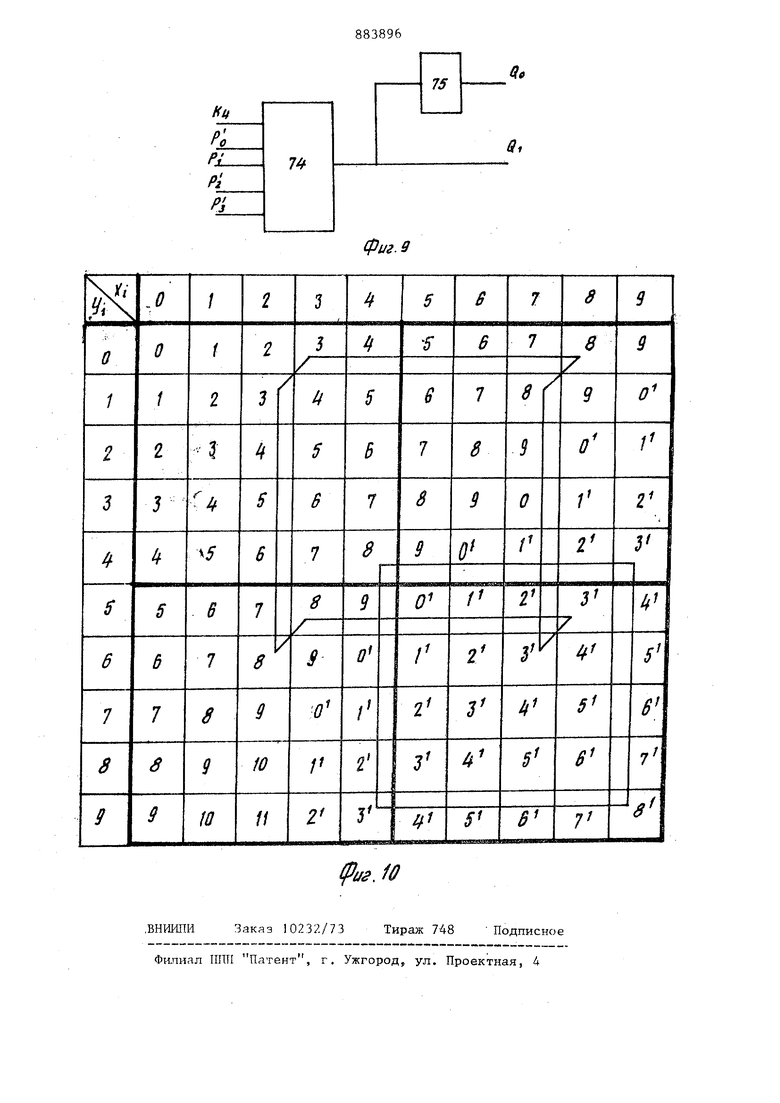

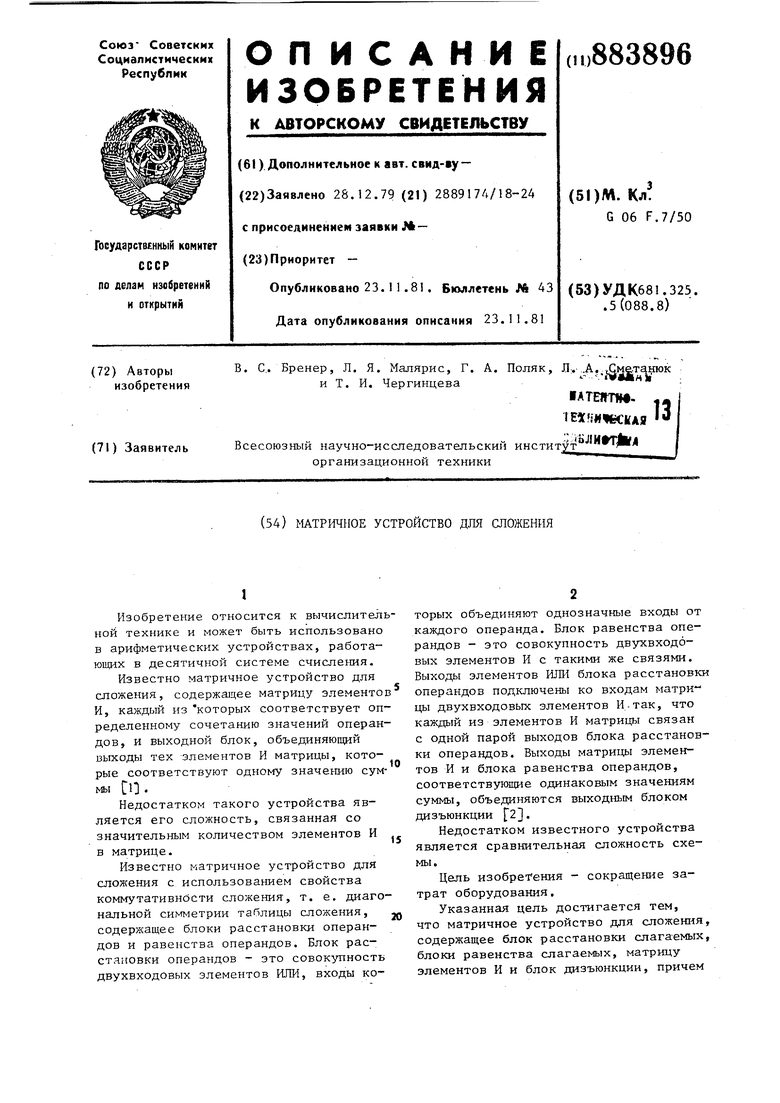

Изобретение относится к вычислител ной технике и может быть использовано в арифметических устройствах, работающих в десятичной системе счисления. Известно матричное устройство для сложения, содержащее матрицу элементо И, каждый из которых соответствует оц ределенному сочетанию значений операн дов, и выходной блок, объединяющий выходы тех элементов И матрицы, которые соответствуют одному значершю сум мы сп Недостатком такого устройства является его сложность, связанная со значительным количеством элементов И в матрице. Известно матричное устройство для сложения с использованием свойства коммутативности сложения, т. е. диаго нальной си 1метрии таблицы сложения, содержащее блоки расстановки операндов и равенства операндов. Блок расстановки операндов - это совокупность двухвходовых элементов ИЛИ, входы которых объединяют однозначные входы от каждого операнда. Блок равенства операндов - это совокупность двухвходовых элементов И с такими же связями. Выходы элементов ИЛИ блока расстановки операндов подключены ко входам матри цы двухвходовых элементов И-так, что каждый из элементов И матрицы связан с одной парой выходов блока расстановки операндов. Выходы матрицы элементов И и блока равенства операндов, соответствующие одинаковым значениям суммы, объединяются выходным блоком дизъюнкции 2. Недостатком известного устройства является сравнительная сложность схемы. Цель изобретения - сокращение затрат оборудования. Указанная цель достигается тем, что матричное устройство для сложения, содержащее блок расстановки слагаемых, блоки равенства слагаемых, матрицу элементов И и блок дизъюнкции, причем входы блока расстановки слагаемых соединены со входами блока равенства слагае№1х, выходы блока расстановки слагаемых соединены со входами матрицы элементов И, выходы которой соединены с первой группй входов блока дизъюнкции, вторая группа входов которого соединена с выходами блока равенства слагаемых, содержит блок выделения пары квадрантов, два блока объединения квадрантов, коммутатор и блок формирования переноса, причем входы первого блока объединения квадрантов соединены с Р входами первого операнда устройства (Р- четное основанне системысчисления, а выходы со входами первых групп блоков расста новки слагаемых и равенства слагаемых входы второго блока объединения квадрантов соединены с Р входами второго операнда устройства, а выходы - со вх дами вторых групп блоков расстановки слагаемых и равенства слагаемых, вход первой и второй групп блока выделения пары квадрантов соединены соответственно с Р/2 младшими входами первого и второго операндовустройства, выходы блока дизъюнкции соединены с инфор мационными входами коммутатора, первый и второй управляющие входы которо го соединены с соответствующими выходами блока выделения пары квадрантов, третий выход которого соединен с первым входом блока формирования переноса, остальные Р/2-1 входов которого подключены к дополнительным выходам коммутатора, выходы которого являются выходами устройства, выходы блока фор мирования переноса являются выxoдa и переноса устройства. При этом, блок выделения пары квад рантов содержит элементы И, ИЛИ, НЕ, причем входы первого элемента .ИЛИ сое динены со входами первой гр-уппы блока входы второго элемента ИЛИ соединены со входами второй группы блока, выходы первого и второго элементов ИЛИ со единены со входами первого элемента И, входы первого и второго элементов НЕ соединены соответственно с выходами первого и второго элементов ИЛИ, а выходы - со входами второго элемента И, выходы первого и второго элементов И соединены со входами третьего элемента ИЛИ, выход которого соединен с первым выходом блока н входом третьег элемента НЕ, выход которого соединен со вторым выходом блока, выход второго элемента И соединен с третьим выходом блока. Кроме того, блок объединения квадрантов содержит Р/2 элементов ИЛИ, причем входы i-ro элемента ИЛИ соединены с i-M и (i )-м входами блока, а выход соединен с i-м выходом блока (1 1,..., Р/2). Кроме того, коммутатор содержит две группы элементов И и группу элементов ИЛИ, причем первый вход j-ro элемента И первой группы соединен с J-M информационным входом коммутатора, а второй вход - с первым управляющим входом коммутатора (j 1,..., P-l), первый вход j-ro элемента И второй группы соединен с К-м информационным входом коммутатора (К j + Р/2, при J Р/2 , К j Р/2 + , при j Р/2), а выход j-ro элемента И первой группы соединен со входом j-ro элемента ИЛИ группы, выход j-ro элемента И второй группы соединен со входом т-го элемента ИЛИ группы (т J , при j Р/2, „, j + 1, при j Р/2) , выход е -го элемента ИЛИ группы соединен с -м выходом коммутатора ( 0 1,..., Р) , выходы элементов И второй группы с первого по (Р/2-1)-й соединены с дополнительными выходами коммутатора. Кроме того блок формирования переноса содержит элемент ИЛИ и эле- мент НЕ, причем входы элемента ИЛИ соединены со входами блока, а выходсо входом элемента НЕ, выходы элемента ИЛИ иэлемента НЕ соединены с выходами блока. На фиг, 1 изображена структурная схема устройства; на фиг. 2 - функциональная схема блока вьщеления пары квадрантов; на фиг. 3 - то же, блока объединения квадрантов; на фиг, 4 - то же, блока расстановки слагаемых; на фиг, 5 - то же, блока равенства слагаемых; на фиг. 6 - то же, матрицы элементов И; на фиг. 7то же, блока дизъюнкции; на фиг. 8то же, коммутатора; на фиг. 9 - то же, блока формирования переноса; на фиг, 10 - таблица сложения. Рассмотрение устройства проводят при , Устройство содержит блок 1 выделения пары квадрантов, блоки 2 и 3 объедине1шя квадрантов, блок 4 расстановки слагаемых, блок 5 равенства слагаемых, матрицу 6 элементов И, блок 7 дизъюнкции, коммутатор 8 и блок 9 формирования переноса. Блок 1 выделения пары квадрантов содержит элементы ИЛИ 10-12, И 13 и 14, НЕ 15-17. Блок 2 (З) объединения квадрантов содержит элементы ИЛИ 1822. Блок 4 расстановки слагаемых содержит элементы ИЛИ 23-27. Блок 5 ра венства слагаемых содержит элементы И 28-32. Матрица 6 содержит элементы И 33-42. Блок 7 дизъюнкции содержит элементы ИЛИ 43-47. Коммутатор 8 содержит элементы И 48-65 и элементы ИЛИ 66-73. Блок 9 формирования переноса содержит элемент ИЛИ 74 и элемент НЕ 75. Устройство работает следукнцим образом. На входы устройства подаются вход ные сигналы операндов XQ-)д и . Блок 1, на входы которого подаются значения младших входов операндов XQ- Хд и Y Y,- реализует на трех сво их выходах сигналы H.lXvXvXvXvX) VvVvY vVv Ol2.i40-iQ JA n)(oVX,vX,vx,vX) (. ,)tV V. указывающие, соответственно, на принадлежность значения суммы первому или четвертому, второму или третьему четвертому квадрантам таблицы сложения (фиг. 10). Блоки 2-5 реализуют на своих выхо дах сигналы

2i Х Х.5

NH/ - , Y V

Z;

V

1 - -1 V -Wi

(i о, 1, 2, 3,4)

s. г, .v/г

Матрица 6 реализует конъюнкцию от взятых попарно значений V; , образуя на своих выходах сигналы

U;ij V.V.J. (J О, 1, 2,3, 4; I j)

Блок 7, объединяя одинаковые значения Ujij и S, реализует на своих выходах сигналы t (К О,...,8), соответствующие таблице сложения для одного (первого) квадранта таблицы сложения (фиг. 10)

to So

Ч Si

t-, UQ

t5 U 4v-Uo,,

tn S,

л tfe 14

4 V Ь4

с .

to J4

Чтобы определить истинное значение результата, производится коммутация Формула изобретения

1. Матричное устройство дпя сложения, содержащее блок расстановю слагаемых, блок равенства слагаемых, матрицу элементов И и блок дизъюнкции, причем входы блока расстановки слагаемых соединены со входами блока равенства слагаемых, выходы блока расстановки слагаемых соединены со входами матрицы элементов И, выходы которой соединены с первой группой входов

блока дизъюнкции, вторая группа входов которого соединена с выходами блока равенства слагаемых, отличаюю щ е е с я тем, что, с целью сокращения затрат оборудования, устройство

содержит блок выделения пары квадрантов, два блока объединения квадрантов, коммутатор и блок формирования переноса, причем входы первого блока объединения квадрантов соединены с Р 6 .4 сигналов tgi t(j коммутатором 8 под управлением ранее определенных значений Н и Н. Значения результата Р.Pq реализуются при этом по формулам где совместно с сигналом Кл реализуют сигналы функции переноса в старший разряд Q, V Р; V Pi V Р1 . образом, используя более глубокие закономерности таблицы сложения, чем простая диагональная симметрия, можно достичь уменьшения затрат обору дования (в основном за счет сокращения числа элементов И в матрице. На- . пример, при предлагаемое устройство требует для своего построения 81 элемент И, 1ШИ, НЕ, в то время, как для построения схемы прототипа требуется 125 элементов. Образуемая ЭКОНОМИЯ 35%. входами первого операнда устройства (Р - четное основание системы счисления) , а выходы - со входами первых групп блоков расстановки слагаемых и равенства слагаемых, входы второго блока объединения квадрантов соединены с Р входами второго операнда устройства, а выходы - со входами вторых групп блоков расстановки слагаемых и равенства слагаемых, входы пер вой и второй групп.блока вьщеления пары квадрантов соединены соответственно с Р/2 вшадшими входами первого и второго операндов устройства, выходы блока дизъюнкции соединены с информационныьв входами коммутатора, первый и второй управляющие входы которого соединены с соответствующими выходами блока выделения пары квадрантов, третий выход которого соединен с первым входом блока формирования переноса, остальные Р/2-1 входов которого подключены к дополнительным выходам коммутатора, выходы которого являются выходами устройства, выходы блока формирования переноса являются выходами переноса устройства. 2, Устройство по п. 1, о.т что блок выдечающееся тем. ления пары квадрантов содержит элементы И, ИЛИ, НЕ, причем входы первого элемента ИЛИ соединены со входами первой группы блока, входа второго элемента ИЛИ соединены со входами второй группы блока, выходы первого и второго элементов ИЛИ соединены со входами первого элемента И, входы первого и второго элементов НЕ соединены соответственно с выходами первого и второго элементов ШШ, а выходысо входами второго элемента И, выходы первого и второго элементов И соединены со входами третьего элемента ШШ, выход которого соединен с первым выходом блока и входом-третьего элемента НЕ, выход которого соединен со вторым выходом блока, выход второ- .го элемента И соединен с третьим выходом блока. 68 3.Устройство по п. 1, отличающееся тем, что блок объединения квадрантов содержит Р/2 элементов ШШ, причем входы i-ro элемента ИЛИ соединены с i-м и (i + Р/2)-м входами блока, а выход соединен с i-м выходом блока (i 1,..., Р/2) 4.Устройство по п. 1, отличающееся тем, что коммутатор содержит две группы элементов И и группу элементов ИЛИ, причем первый вход j-ro элемента И первой группы оединен с j-м информационным входом коммутатора, а второй вход - с первым управляющим входом коммутатора (j 1,...,P-l), первый вход j-ro элемента И второй группы соединен с К-м информационным входом коммутатора (К if j + Р/2, при j Р/2, К j Р/2 + 1, при j Р/2), выход j-ro элемента И первой группы соединен со входом j-ro элемента ИЛИ группы, выход j-ro элемента И второй группы соединен со входом пт-го элемента ИЛИ группы (т - j, при j Р/2, m j + + 1, при j Р/2) , выход -го элемента ИЛИ группы соединен с 2 -м выходом комму.татора ( 5 1,...,Р), выходы элементов И второй группы с первого по (Р/2-1)-й соединены с дополнительными выходами коммутатора. 5. Устройство по п. 1, отличающееся тем, что блок формирования переноса содержит элемент ШШ и элемент НЕ, причем входы элемента ИЛИ соединены со входами блока, а выход - со входом элемента НЕ, выходы элемента ИЛИ и элемента НЕ соединены с выходами блока. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 259479, кл. G 06 F 7/39, 1968. 2,Авторское свидетельство СССР № 496555, кл. G 06 F 7/38, 1974 (прототип) .

фиг./

(р1/г.З

1раг.4

фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Оптоэлектронный сумматор | 1990 |

|

SU1753463A1 |

| Матричное устройство умножения по моD П | 1980 |

|

SU943714A1 |

| Матричное вычислительное устройство | 1974 |

|

SU496555A1 |

| Вычислительное устройство | 1985 |

|

SU1262485A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Оптический модуль для сложения и вычитания | 1990 |

|

SU1775719A1 |

иг. ff

fPus.7

JH2

tj

fh( H2

i7 H2

is HjiB ,

zf« H,

ф1/г.&

фиг. 9

Авторы

Даты

1981-11-23—Публикация

1979-12-28—Подача