Хв

5 ,

Ч

rf

%

15.

ift г ш

мл

V

| название | год | авторы | номер документа |

|---|---|---|---|

| Оптоэлектронный сумматор | 1987 |

|

SU1427364A1 |

| Устройство для вычисления логарифмачиСлА | 1979 |

|

SU849210A1 |

| Сумматор | 1989 |

|

SU1735841A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1981 |

|

SU999062A1 |

| Накапливающий сумматор | 1982 |

|

SU1104506A1 |

| Сумматор в знакоразрядной позиционно-остаточной системе счисления | 1986 |

|

SU1383349A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в арифметических устройствах, работающих в десятичной системе счисления. Целью изобретения является расширение функциональных возможностей устройства за счет выполнения вычитания десятичных чисел. Оптоэлектронный сумматор содержит блок 1 подготовки данных, блок 2 формирования результата, блок 3 переноса, блок 4 выделения квадрантов. 2 табл., 4 з.п. ф-лы, 9 ил.

5

,J6

a «

ШУЮ

$&

&

ffS

wfff№L

&

ж

фф фуффффф

ffifS6fS7 58 fft60 6lf6t/63(Pud

.№

fJS

45

,J9,

fjj

,6

СЛ

с

f4f

MO

xi

СЛ

ы

Twz

f4J

т

JO:

,

,.../№,

J

fS4

CA)

fss

Изобретение относится к автоматике и вычислительной технике и может быть использовано в арифметических устройствах, работающих в десятичной системе счисления.

Известен матричный сумматор, содержащий два элемента ИЛИ, группы элементов ИЛИ, группы элементов И. блоки элементов И, элемент НЕ, коммутаторы, регистр сдвига, блок контроля и блок управле- ния.

Недостатком данного сумматора является низкое быстродействие, обусловленное последовательным прохождением сигналов.

Известен матричн- й сумматор, содержащий восемь комму.аторов, шесть групп элементов ИЛИ, блок элементов И, два элемента контроля, блок управления, логический блок, шесть регистров, четыре элемента ИЛИ, элемент НЕ и четыре элемента И.

Недостаток данного сумматора - невозможность выполнения вычитания.

Наиболее близким по технической сущ- ности к предлагаемому является оптоэлект- ронный сумматор, содержащий блок переноса, блок формирования результата, блок подготовки операндов, преобразователь, 1-е входы первого и второго операндов сумматора, где I 0,9 - разрядность операндов, подключены соответственно к (I + 1)-му и 0 + 11)-му оптическим входам блока подготовки данных, пять старших разрядов обоих операндов связаны соответственно с (J + 1}-м и (j + б)-м 0 О/i) оптическими входами блока переноса, К-й (К 1,15) оптический выход блока подготовки данных связан с К-м оптическим входом блока формирования результата, второй, третий, четвертый, пятый, четырнадцатый и пятнадцатый оптические выходы блока подготовки данных связаны с одиннадцатым, двенадцатым, тринадцатым, четырнадцатым, пятнадцатым и шестнадцатым оптическими входами Злока переноса, первый и второй оптические выходы которого связаны с первым и вторым оптическими входами преобразователя, первый и второй электрические выходы которого подключены к первому и второму электрическим входам блока формирования результата, первый электрический вход которого также связан с электрическим входом блока переноса, третий и четвертый оптические выходы блока переноса являются прямым и инверсным выходами сигнала переноса сумматора, первые десять оптических выводов блока формирования результата соединены с прямыми выходами суммы сумматора, а вторые

десять оптических выходов - с инверсными оптическими выходами суммы сумматора, управляющий вход сумматора подключен к управляющим входам блоков подготовки данных, формирования результата и переноса, блок подготовки данных содержит в каждом q-м разряде, где q Т,4, первый и второй элементы 2-2И-ИЛИ и элемент ИЛИ, первый, второй,третий и четвертый входы j-ro разряда (j 0,4) блока подготовки данных соединены соответственно с J-м разрядом первого операнда сумматора, j-й разряд второго операнда сумматора, 0 + 5)-й разряд первого операнда сумматора и (j + 5)-й разряд второго операнда оптически связаны с соответствующими входами элемента ИЛИ блока подготовки данных, оптический выход которого соединен с первым оптическим выходом разряда блока подготовки данных, оптические выходы первого и второго элементов 2-2И-ИЛИ q- го разряда блока подготовки данных являются соответственно вторым и третьим оптическими выходами разряда блока подготовки данных, первые оптические входы первого и второго элементов 2-2И-ИЛИ q- го разряда блока подготовки данных связаны с первым и третьим оптическими входами разряда блока подготовки данных, а вторые оптические входы первого и второго элементов 2-2И-ИЛИ q-ro разряда блока подготовки данных связаны с вторым и четвертым входами разряда блока подготовки данных соответственно первого и второго элементов 2-2И-ИЛИ блока подготовки данных, причем первый, второй, третий, четвертый оптические входы j-ro разряда блока подготовки данных связаны соответственно с 0 + 1)-м. О + 1)-м, 0 + 1б)-м входами блока, а первые оптические выходы j-x разрядов связаны с 0 + 1)-ми выходами блока подготовки данных, вторые оптические выходы j-x разрядов связаны с Q + 6)-ми выходами блока подготовки данных, третьи оптические выходы j-x разрядов связаны с Q + 11)-ми выходами блока подготовки данных, блок формирования результата содержит десять разрядов, каждый из которых содержит элемент Й-ИЛИ, причем второй электрический вход элемента И-ИЛИ нулевого, восьмого и девятого разрядов блока формирования результата подключены к первому электрическому входу блока формирования результата, электрический вход элементов И-ЙЛИ первого, второго, третьего, четвертого, пятого, шестого и седьмого разрядов блока формирования результата, а также первый электрический вход элементов И- ИЛИ третьего, четвертого и пятого разрядов блока формирования результата подключены к второму электрическому входу блока формирования результата, первый оптический вход блока формирования результата связан с третьими оптическими входами элементов И-ИЛИ первого, второго, треть- его, четвертого разрядов блока формирования результата и с первыми оптическими входами элементов И-ИЛИ шестого, седьмого, восьмого и девятого разрядов блока формирования результата, второй оптиче- ский вход блока формирования результата соединен с первым оптическим входом элементов И-ИЛИ нулевого, третьего, четвертого и пятого разрядов блока формирования результата, с вторыми оптическими входа- ми элементов И-ИЛИ шестого разряда блока формирования результата, третьими оптическими входами элементов И-ИЛИ восьмого и девятого разрядов и с четвертым оптическим входом первого элемента И- ИЛИ разряда блока формирования результата, третий оптический вход блока формирования результата соединен с первым оптическим входом элемента И-ИЛИ первого разряда, с вторыми оптическими входами элементов И-ИЛИ третьего и седьмого разрядов, с третьими оптическими вхо- дами элементов И-ИЛИ нулевого, пятого и шестого разрядов, с четвертыми входами элементов И-ИЛИ второго и восьмого раз- рядов блока формирования результата, четвертый оптический вход блока формирования результата соединен с первым оптическим входом элемента И-ИЛИ второго разряда блока формирования ре- зультата, с вторыми оптическими входами элементов И-ИЛИ четвертого, восьмого разрядов блока формирования результата, с третьим оптическим входом элемента И-ИЛИ седьмого разряда, с четвертыми опти- ческими входами элементов И-ИЛИ нулевого, третьего, пятого и девятого разрядов блока формирования результата, пятый оптический вход блока формирования результата соединен с вторыми оптическими входами элементов И-ИЛИ нулевого, первого, второго, пятого и девятого разрядов, с четвертыми оптическими входами элементов И-ИЛИ четвертого, шестого и седьмого разрядов блока формирования результата, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, тринадцатый, четырнадцатый и пятнадцатый оптические входы блока формирования результата соединены4 с пятыми оптическими входами элементов И-ИЛИ соответственно нулевого, второго, четвертого, шестого, восьмого, пятого, седьмого, девятого, первого и третьего блоков формирования результата, блок формирования переноса содержит четыре элемента

ИЛИ, первый и второй элементы И-ИЛИ, причем первые пять оптических входов блока формирования подключены к входам второго и пятого элементов ИЛИ, а шестой, седьмой, восьмой, девятый и десятый оптические входы блока формирования переноса связаны с входами третьего и четвертого элементов ИЛИ, выходы второго и третьего элементов ИЛИ подключены к первому прямому и инверсным входам первого элемента И-ИЛИ блока формирования переноса, выходы четвертой и пятой схем ИЛИ подключены к вторым прямому и инверсному входам первого элемента И-ИЛИ блока формирования переноса, прямой и инверсный оптические выходы которого связаны соответственно с первым и вторым оптическими входами блока формирования переноса, к входам второго элемента И-ИЛИ блока формирования переноса подключены выходы третьего и четвертого элементов ИЛИ блока формирования переноса, к первым входам второго, третьего, четвертого, пятого элементов И второго элемента И- ИЛИ блока формирования переноса подключен первый электрический вход блока формирования переноса, к вторым входам второго, третьего, четвертого элементов И второго элемента И-ИЛЙ блока формирования переноса подключены одиннадцатый, двенадцатый и тринадцатый оптические входы блока формирования переноса, а к третьим входам второго, третьего и четвертого элементов И второго элемента И-ИЛИ блока формирования переноса подключен четырнадцатый оптический вход блока формирования переноса, второй и третий входы пятого элемента И второго элемента И- ИЛИ блока формирования переноса связаны с двенадцатым и тринадцатым оптическими входами блока формирования переноса, первый и второй оптические входы шестого элемента И второго элемента И-ИЛИ блока формирования переноса связаны с пятнадцатым и шестнадцатым оптическими входами блока формирования переноса, прямой и инверсный выходы второго элемента И-ИЛИ блока формирования переноса связаны соответственно с третьим и четвертым оптическими выходами блока формирования переноса.

Недостатком данного оптоэлектронно- го сумматора является невозможность выполнения операции вычитания.

Целью изобретения является расширение функциональных возможностей устройства за счет выполнения операции вычитания десятичных чисел.

Поставленная цель достигается тем, что оптоэлектронный сумматор, содержащий

блок переноса, блок формирования результата, блок подготовки операндов, причем 1-е входы первого и второго операндов сумматора, где ,9 - разрядность операндов, подключены соответственно к (I + 1)-му и (I + +11)-му входам блока подготовки данных, К-й (К 1,15) выход блока подготовки данных связан с К-м входам блока формирования результата, соответствующие выходы блока подготовки данных связаны с одиннадцатым, двенадцатым, тринадцатым, четырнадцатым, пятнадцатым, шестнадцатым входами блока переноса, десять выводов блока формирования результата соединены с прямыми выходами сумматора, управляющий вход суммг юра подключён к управляющим входам блоков подготовки данных, формирования результата, блок подготовки данных содержит первый и второй элементы 2-2И-ИЛИ и элемент ИЛИ в каждом q-м разряде, где q 0,4, первый, второй, третий и четвертый входы j-ro разряда 0 ) блока подготовки данных соединены соответственно с j-м разрядом первого операнда сумматора, j-м разрядом второго операнда сумматора, 0 + 5)-м разрядом первого и второго операндов, которые связаны с соответствующими входами элемента ИЛИ блока подготовки данных, выходы первого и второго элементов 2-2И-ИЛИ блока подготовки данных являются соответственно вторым и третьим выходами блока подготовки данных, причем первый, второй, третий, четвертый входы j-ro разряда блока подготовки данных связаны соответственно с 0 + 1)-м, 0 + 11)-м, 0 + 6)-м, 0 + 1б)-м входами блока, блок формирования результата содержит десять разрядов, каждый из которых содержит элемент И-ИЛИ, причем входы элементов И-ИЛИ восьмого и девятого разрядов блока формирования результата подключены к первому входу блока формирования результата, входы элементов первого, третьего, четвертого, пятого, шестого разрядов блока формирования результата подключены к второму входу блока формирования результата, блок переноса содержит четыре элемента ИЛИ и элементы И-ИЛИ, содержит блок выделения квадрантов,i-e входы первого и второго операндов сумматора, где I - 0,9 - разрядность операндов, подключены соответственно к (I + 1)-му и (I + 11)-му входам блока выделения квадрантов, разряды второго операнда связаны с входами второй группы блока формирования результата, первый, второй и третий выходы блока выделения квадрантов связаны с двадцать первым, двадцать вторым и двадцать третьим входами блока подготовки данных, первый управляющий вход сумматора, кроме того, подключен к управляющему входу блока выделения квадрантов, а второй управляющий вход сумматора подключен к входам блока подготовки данных,

блока формирования результата и блока выделения квадрантов, четвертый и пятый выходы блока выделения квадрантов связаны с соответствующими входами блока формирования результата, кроме того, входы бло0 ка переноса с первого по десятый и с семнадцатого по двадцатый связаны с соответствующими выходами блока подготовки данных, десять выходов блока переноса подключены к входам третьей группы блока

5 формирования результата, вход внешнего переноса сумматора связан с соответствующим входом блока переноса, одиннадцатый выход которого является выходом группового переноса сумматора.

0 Кроме того, блок подготовки операндов содержит второй элемент ИЛИ в каждом j-м . разряде, где j 0,4, а также элемент 2-2И- ИЛИ, первый, второй и третий мультиплексоры и устройство местного переноса,

5 которое содержит десять групп элементов И-НЕ, пять элементов 4-2И-ИЛИ-НЕ, два элемента 2И-ИЛИ-НЕ, два элемента 4И- НЕ, четыре элемента НЕ и два резистора, причем первые входы вторых элементов

0 ИЛИ j-ro разряда соединены с (S-J)-MH входами разрядов операндов, вторые - с (11 + +J)-MM, третьи - с (1 O-J)-MH, четвертые - с (16+ + jj-ми входами разрядов операндов, выходы вторых элементов ИЛИ нулевого, перво5 го, второго, третьего разрядов подключены к второй группе входов первого мультиплексора, выходы которого являются выходами блока подготовки данных, выходы первого и второго элементов ИЛИ четвертого разряда

0 соединены с соответствующими входами первого элемента 2-2И-ИЛИ, кроме того, третий вход первого элемента 2-2И-ИЛИ, первые входы второго и третьего элементов 2-2И-ИЛИ подключены к второму управля5 ющему входу сумматора, второй вход первого элемента 2-2И-ИЛИ и третьи входы второго и третьего элементов 2-2И-ИЛИ, управляющие входы первого, второго и третьего мультиплексоров подключены к

0 первому управляющему входу сумматора, первый вход блока подготовки данных соединен, кроме того, с вторым входом второго элемента 2-2И-ИЛИ и с соответствующим входом второй группы входов второго муль5 типлексора, пятый вход блока соединен с третьим входом первой группы входов второго мультиплексора и с четвертым входом третьего элемента 2-2И-ИЛИ, выход которого связан с соответствующим выходом блока подготовки данных, шестой вход блока соединен с вторым входом третьего элемента 2-2И-ИЛ И и с третьим входом второй группы входов второго мультиплексора, первые входы третьего мультиплексора соединены соответственно с вторым, седьмым, четвертым, девятым входами блока, вторые входы - с девятым, четвертым, седьмым, вторым входами соответственно, первые входы второго мультиплексора соединены с третьим, восьмым, пятым и десятым входами блока, вторые входы - с восьмым, третьим, шестым и первым входами блока соответственно, а выходы подключены к соответствующим выходам блока, первый вход блока соединен с первыми входами элементов И-НЕ шестой группы, с первыми входами первого элемента 4-2И- ИЛИ и второго элемента 2-2И-ИЛИ-НЕ, второй вход блока подготовки данных соединен с первыми входами первого, второго и третьего элементов И-НЕ седьмой группы, а также с третьими входами первого элемента 4-2И-ИЛИ-НЕ и второго элемента 2-2И-ИЛИ-НЕ, с вторым входом третьего элемента И-НЕ третьей группы, третий вход блока связан с первыми входами первого элемента И-НЕ десятой группы и четвертого элемента И-НЕ седьмой группы, третьего элемента 4-2И-ИЛИ-НЕ, а также с пятым входом первого элемента 4-2И- ИЛИ-НЕ, с восьмым входом второго элемента 4-2И-ИЛИ-НЕ, с вторыми входами четвертого элемента И-НЕ третьей группы и третьего элемента И-НЕ четвертой группы, четвертый вход блока подключен к первому входу второго элемента И-НЕ десятой группы, к вторым входам четвертого и первого элементов И-НЕ четвертой группы и второго элемента И-НЕ пятой группы, а также к седьмому входу первого элемента 4- 2И-ИЛИ-НЕ и к третьему входу третьего элемента 4-2И-ИЛИ-НЕ, пятый вход блока соединен с вторыми входами первого, третьего и четвертого элементов И-НЕ пятой группы, второго элемента И-НЕ четвертой группы, а также с первым входом второго элемента 4-2И-ИЛИ-НЕ и пятым входом третьего элемента 4-2И-ИЛИ-НЕл шестой вход блока связан с первыми входами первого и второго элементов И-НЕ восьмой группы и третьего и четвертого элементов И-НЕ десятой группы, а также с третьим входом второго элемента 4-2И- ИЛИ-НЕ и седьмым входом третьего элемента 4-2И-ИЛИ-НЕ, седьмой вход блока соединен с первыми входами первого элемента И-НЕ девятой группы, второго элемента И-НЕ третьей группы, третьего и четвертого элементов И-НЕ восьмой группы и четвертого элемента 4-2И-ИЛИ-НЕ, а

также с шестым входом второго элемента 4-2И-ИЛИ-НЕ, восьмой вход блока подключен к первым входам первого элемента И-НЕ третьей группы, четвертого элемента

И-НЕ второй группы, второго и третьего элементов И.-НЕ девятой группы, а также к седьмому входу второго элемента 4-2И- ИЛИ-НЕ и к третьему входу четвертого элемента 4-2И-ИЛИ-НЕ, девятый вход блока

0 связан с первыми входами первого, второго и третьего элементов И-НЕ второй группы, четвертого элемента И-НЕ девятой группы, первого элемента 2-2И-ИЛИ-НЕ, а также с пятым входом четвертого элемента 4-2И5 ИЛИ-НЕ, десятый вход блока соединен с первыми входами элементов первой группы, а также с седьмым входом четвертого элемента 4-2И-ИЛИ-НЕ и с третьим входом первого элемента 2-2И-ИЛИ-НЕ,

0 одиннадцатый вход блока подключен к четвертому входу первого элемента 2-2И- ИЛИ-НЕ, к второму входу второго элемента 2-2И-ИЛИ-НЕ, двенадцатый вход блока связан с вторыми входами первых элемен5 тов М-НЕ первой и шестой групп и первого элемента 2-2И-ИЛИ-НЕ, а также с четвертым входом второго элемента 2-2И-ЙЛИ- НЕ, тринадцатый вход блока соединен с вторыми входами первых элементов И-НЕ

0 второй и седьмой групп, вторых элементов И-НЕ первой и шестой групп и третьего элемента 4-2И-ИЛИ-НЕ, четырнадцатый вход блока подключен к вторым входам третьих элементов И-НЕ первой и шестой

5 групп, вторых и четвертых элементов И-НЕ второй и седьмой групп, а также к пятому входу второго элемента 4-2И-ИЛИ-НЕ и четвертому входу третьего элемента 4-2И- ИЛИ-НЕ, пятнадцатый вход блока связан с

0 вторыми входами четвертых элементов И- НЕ первой и шестой групп, третьих элементов И-НЕ второй и седьмой групп и первого и второго элементов И-НЕ третьей и десятой групп, а также с четвертым входом вто5 рого элемента 4-2И-ИЛИ-НЕ и шестым входом третьего элемента 4-2И-ИЛИ-НЕ, шестнадцатый вход блока соединен с вторым входом второго элемента 4-2И-ИЛИ- НЕ и восьмым входом третьего элемента

0 4-2И-ИЛИ-НЕ, семнадцатый вход блока подключен к первому входу четвертого элемента И-НЕ пятой группы, к вторым входам третьего элемента И-НЕ десятой группы и четвертого элемента 4-2И-ИЛИ-НЕ, а так5 же к восьмому входу первого элемента 4- 2И-ИЛИ-НЕ, восемнадцатый вход блока связан с четвертым и шестым входами первого элемента 4-2И-ИЛИ-НЕ, четвертым входом четвертого элемента 4-2И-ЙЛИ- НЕ, с первыми входами второго и третьего

элементов И-НЕ питой группы, а также с вторыми входами третьего элемента И-НЕ восьмой группы и четвертого элемента И- НЕ десятой группы, девятнадцатый вход блока подключен к первым входам третьего и четвертого элементов И-НЕ четвертой группы, первого элемента И-НЕ пятой группы, вторым входам второго элемента И-НЕ девятой группы, первого и четвертого элементов И-НЕ восьмой группы, а также к шестому входу четвертого элемента 4-2И- ИЛИ-НЕ, двадцатый вход блока соединен с первыми входами третьего и четвертого элементов И-Н Е третьей группы, первого и второго элементов И-НЕ четвертой группы, с вторыми входами втс это элемента И-НЕ восьмой группы, первого, третьего и четвертого элементов И-НЕ девятой группы, первого элемента 4-2И-ИЛИ-НЕ, с восьмым входом четвертого элемента 4-2И-ИЛИ- НЕ, первый электрический вход устройства связан с четвертым входом второго элемента 4И-НЕ и с входом первого элемента НЕ, выход которого подключен к входу второго элемента НЕ, второй электрический вход сумматора соединен с первым входом первого элемента 4И-НЕ и с входом третьего элемента НЕ, выход которого подключен к входу четвертого элемента НЕ, выходы элементов И-НЕ первой, второй, третьей, четвертой и пятой групп четвертого элемента НЕ, а также первый и третий входы пятого элемента 4-2И-ИЛИ-НЕ соединены с первым выводом первого резистора, второй вывод которого подключен к шине питания, выходы элементов И-НЕ групп с шестой по десятую, второго элемента НЕ, а также шестой и седьмой входы пятого элемента 4- 2И-ИЛИ-НЕ соединены с первым выводом второго резистора, второй вывод которого подключен к шине питания, выходы первого и-второго элементов 4-2И-ИЛИ-НЕ и первого элемента 2-2И-ИЛИ-НЕ подключены к соответствующим входам первого элемента 4И-НЕ, выходы третьего, четвертого элементов 4-2И-ИЛИ-НЕ, второго элемента 2-2И-ИЛИ-НЕ соединены с соответствующими входами второго элемента 4И-НЕ, двадцать первый вход блока связан с восьмым входом пятого элемента 4-2И-ИЛИ- НЕ, двадцать второй вход блока соединен с вторым входом пятого элемента 4-2И- ИЛИ-НЕ, двадцать третий вход блока подключен куетвертому и пятому входам пятого элемента 4-2И-ИЛИ-НЕ, выходы первого и второго элементов 4И-НЕ, пятого элемента 4-2И-ИЛИ-НЕ связаны с выходами блока. Кроме того, блок выделения квадрантов содержит четыре элемента ИЛИ-НЕ, восемь элементов И-Н Ё, два резистора, входы

первого элемента ИЛИ-НЕ связаны с разрядами первого операнда с нулевого по четвертый, входы второго элемента ИЛИ-НЕ - с пятого по девятый разрядами первого операнда, входы третьего элемента ИЛИ-НЕ - с входами разрядов второго операнда с нулевого по четвертый, входы четвертого элемента ИЛИ-НЕ - с входами разрядов второго операнда с пятого по девятый, вы0 ход первого элемента ИЛИ-НЕ связан соответственно с входами первого, второго, пятого, седьмого элементов И-НЕ, выход второго элемента ИЛИ-НЕ соединен с соответствующими входами второго, четверто5 го, шестого и восьмого элементов И-НЕ, выход третьего элемента ИЛИ-НЕ подключен к соответствующим входам первого, четвертого, шестого и седьмого элементов И-НЕ, выходы первого, третьего и четверто0 го элементов ИЛИ-НЕ являются соответствующими выходами блока выделения квадрантов, первый электрический управляющий вход сумматора соединен с соответствующими входами третьего, четвертого,

5 седьмого и восьмого элементов И-НЕ, второй управляющий вход подключен к соответствующим входам первого, второго, пятого и шестого элементов И-НЕ, выход элементов И-НЕ с первого по четвертый,

0 первый выход блока выделения квадрантов подключены к первому выводу первого резистора, второй вывод которого подключен к шине питания, выходы элементов И-НЕ с пятого по восьмой, второй выход блока вы5 деления квадрантов соединены с первым выводом второго резистора, второй вывод которого подключен к шине питания, выход четвертого элемента ИЛИ-НЕ связан с входами второго, третьего, пятого и восьмого

0 элементов И-НЕ.

Блок переноса содержит три элемента И-ИЛИ, семь групп элементов И, семь элементов ИЛИ, первый и второй входы первого элемента И-ИЛИ подключены к

5 одиннадцатому входу блока переноса, третий и четвертый входы первого элемента И-ИЛИ соединены с первым и двадцать первым входами блока переноса, первый, второй и третий входы второго и третьего

0 элементов И-ИЛИ связаны с двадцать первым, первым и вторым входами блока переноса, четвертый и пятый входы второго элемента И-ИЛИ и пятый и шестой входы третьего элемента И-ИЛИ подключены к

5 одиннадцатому и второму входам блока переноса, шестой и седьмой входы второго элемента И-ИЛИ соединены с двенадцатым входом блока, четвертый, седьмой и девятый входы третьего элемента И-ИЛИ связа- ны с третьим входом блока, восьмой вход

третьего элемента И-ИЛИ связан с двенадцатым входом блока, а десятый и одиннадцатый входы третьего элемента И-ИЛИ подключены к тринадцатому входу блока, который подключен также к первым входам третьего элемента И третьей группы, четвертого элемента И четвертой группы, пятого элемента И пятой группы, шестого, элемента И шестой группы и седьмого элемента И седьмой группы, входы первого элемента И первой группы соединены с тринадцатым и четвертым входами блока, третий и четвертый входы блока соединены с соответствующими входами второго, третьего и четвертого элементов И первой группы, второй вход блока связан с вторым входом третьего элемента И первой группы и третьим входом четвертого элемента И первой группы, одиннадцатый вход блока подключен к первому входу третьего элемента И первой группы, двадцать первый и первый входы блока переноса связаны с соответствующими входами четвертого элемента И первой группы, четырнадцатый и пятый входы блока соединены с входами первого элемента И второй группы,тринадцатый, четвертый и пятый входы блока подключены к входам второго элемента И второй группы, третий, четвертый и пятый входы блока связаны с соответствующими входами третьего, четвертого и пятого элементов И второй группы, двенадцатый вход блока соединен с первыми входами третьего элемента И второй группы, четвертого элемента И третьей группы, пятого элемента И четвертой группы, шестого элемента И пятой группы, а также седьмого элемента И шестой группы и восьмого элемента И седьмой группы, одиннадцатый вход блока под- ключен к первому входу четвертого элемента И второй группы, пятого элемента И третьей группы, шестого элемента И четвертой группы, седьмого элемента И пятой группы, восьмого элемента И шестой группы и девятого элемента И седьмой группы, двадцать первый вход блока связан с первыми входами пятого элемента И второй группы, шестого элемента И третьей группы, седьмого элемента И четвертой группы, восьмого элемента И пятой группы, девятого элемента И шестой группы и десятого элемента И седьмой группы, второй вход блока, кроме того, подключен к второму входу четвертого элемента И и к третьему входу пятого элемента И второй группы, первый вход блока, кроме того, подключен к второму входу пятого элемента И второй группы, пятый, шестой, седьмой входы блока связаны с соответствующими входами третьего, четвертого, пятого, шестого и седьмого элементов И четвертой группы, третий и четвертый входы блока связаны с соответствующими входами пятого, шестого и седьмого элементов И четвертой группы, а также четвертый вход соединен с вторым входом четвертого элемента И, шестой вход-с вторым входом второго элемента И, седьмой вход - с вторым входом первого элемента И и третьим входом второго элемента И четвер0 той группы, шестнадцатый вход блока связан с первыми входами первого элемента И четвертой группы, второго элемента И пятой группы, третьего элемента И шесто группы и четвертого элемента И седьмой

5 группы, пятнадцатый вход блока подключен к первым входам первого элемента И третьей группы, второго элемента И четвертой группы, третьего элемента И пятой группы, четвертого элемента И шестой группы1 и

0 пятого элемента И седьмой группы, четырнадцатый вход блока, кроме того, соединен с первыми входами второго элемента И третьей группы, третьего элемента И четвертой группы, пятого элемента И шестой

5 группы, четвертого элемента И пятой группы и шестого элемента И седьмой группы, третий, четвертый, пятый и шестой входы блока подключены к соответствующим входам четвертого, пятого и шестого элементов

0 И третьей группы, а также четвертый, пятый, шестой входы соединены с входами третьего элемента И третьей группы, шестой вход блока связан, кроме того, с вторым входом первого элемента И и с третьим входом вто5 рого элемента И третьей группы, пятый вход - с вторым входом второго элемента И третьей группы, второй вход - с вторым входом пятого элемента И и с третьим входом шестого элемента И третьей группы, первый

0 вход соединен с вторым входом шестого элемента И третьей группы, семнадцатый вход блока связан с первыми входами первого элемента И пятой группы, второго элемента И шестой группы и третьего элемента

5 И седьмой группы, четвертый, пятый, шестой, седьмой и восьмой входы блока соединены с соответствующими входами пятого, шестого, седьмого и восьмого элементов И пятой группы, а также седьмой и восьмой

0 входы блока связаны с соответствующими входами второго, третьего и четвертого элементов И пятой группы, шестой вход блока подключен к третьему входу четвертого элемента И и к второму входу третьего элемен5 та И пятой группы, первый вход блока связан с вторым входо м восьмого элемента И пятой группы, второй вход блока соединен с вторым входом седьмого элемента И и с третьим входом восьмого элемента И пятой группы, третий вход блока связан с

вторым входом шестого элемента И, с третьим входом седьмого элемента И и с четвертым входом восьмого элемента И пятой группы, восьмой вход блока, кроме того, соединен с вторым входом первого элемента И пятой группы, восемнадцатый вход блока подключен к первым входам первого элемента И шестой группы и второго элемента И седьмой группы, четвертый, пятый, шестой, седьмой, восьмой и девятый входы блока связаны с соответствующими входами седьмого, восьмого и девятого элементов И шестой и седьмой групп, а также с входами шестого элемента И шестой группы и десятого элемента И седьмой группы, второй и третий входы блока соединены с соответствующими входами девятого и восьмого элементов И шестой группы и девятого и десятого элементов И седьмой группы, а также третий вход блока подключен к вторым входам седьмого элемента И шестой группы и восьмого элемента И седьмой группы, первый вход блока связан с вторыми входами десятого элемента И седьмой группы и девятого элемента И шестой группы, пятый, шестой, седьмой, восьмой и девятый входы блока, кроме тог соединены с соответствующими входам пятого элемента И шестой группы и элемента И седьмой группы, шестой, седьмой, восьмой и девятый входы блока подключены также к соответствующим входам четвертого элемента И шестой группы и пятого элемента И седьмой группы, кроме того, девятый вход связан с вторым входом первого элемента И шестой группы, с третьим входом второго элемента И и с четвертым входом третьего элемента И шестой группы, а также с вторым входом второго элемента И, с третьим входом третьего элемента И и с четвертым входом четвертого элемента И седьмой группы, кроме того, восьмой вход блока соединен с вторым входом второго элемента И и с третьим входом третьего элемента И шестой группы, а также с вторым входом третьего элемента И и с третьим входом четвертого элемента И седьмой группы, седьмой вход блока подключен к вторым входам третьего элемента И шестой группы и четвертого элемента И седьмой группы, девятнадцатый вход блока связан с первым входом .первого элемента И седьмой группы, десятый вход блока подключен к соответствующим входам всех элементов И седьмой группы, входы К-ro элемента ИЛИ соединены с (13 + К)-м входом блока и с выходами всех элементов И К-й группы, где К 1,7, выходы первого, второго, третьего элементов И-ИЛИ, двадцать первый вход блока, а также выходы элементов ИЛИ

с первого по седьмой связаны с соответствующими выходами блока.

Блок формирования результата содержит в каждом разряде устройство входной

логики, которое содержит десять элементов И-ИЛИ, и выходное устройство, которое содержит десять элементов И-ИЛИ, одиннадцать элементов НЕ, первый вход первой группы входов блока формирования резуль0 тата соединен с четвертыми входами элементов И-ИЛИ первого, второго, третьего и седьмого разрядов, а также с первыми входами элементов И-ИЛИ четвертого и шестого разрядов, второй вход первой группы

5 входов связан с первым входом элемента И-ИЛИ нулевого разряда и с четвертыми входами восьмого и девятого разрядов, третий вход первой группы входов подключен к первым входам элементов И-ИЛИ первого

0 и седьмого разрядов, к четвертым входам элементов И-ИЛИ пятого, нулевого и шестого разрядов, а также к пятому входу элементов И-ИЛИ второго и восьмого разрядов, к второму входу элемента И-ИЛИ

5 третьего разряда, четвертый вход первой группы входов связан с первым входом элемента И-ИЛИ второго разряда, с пятыми входами элементов И-ИЛИ нулевого, третьего, четвертого, пятого и девятого разрядов,

0 а также с вторыми входами элементов И- ИЛИ седьмого и восьмого разрядов, пятый вход первой группы входов блока соединен с вторыми входами элементов И-ИЛИ нулевого, первого,второго,четвертого, пятого и

5 девятого разрядов, а также с пятыми входами элементов И-ИЛИ шестого и седьмого разрядов, первый, шестой, одиннадцатый и шестнадцатый входы второй группы входов блока соединены с соответствующими вхо0 дами элементов И-ИЛИ нулевого и пятого разрядов, четвертый, четырнадцатый, девятый, девятнадцатый входы второй группы входов подключены к соответствующим входам элементов ИЛИ первого и шестого раз5 рядов, второй, двенадцатый, седьмой и семнадцатый входы второй группы входов блока связаны с соответствующими входами элементов И-ИЛИ второго и седьмого разрядов, пятый, десятый, пятнадцатый и

0 двадцатый входы второй группы входов блока соединены с соответствующими входами элементов И-ИЛИ третьего и восьмого разрядов, третий, восьмой, тринадцатый и восемнадцатый входы второй группы входов

5 подключены к соответствующим входам элементов И-ИЛИ четвертого и девятого разрядов, выходы элементов И-ИЛИ соединены с выходами устройства входной логики блока формирования результата, первый вход блока связан с третьими и шестыми

входами элементов И-ИЛИ нулевого и девятого разрядов, с третьими входами элементов И-ИЛИ первого, шестого, восьмого и второго разрядов, второй вход блока соединен с шестым и третьим входами элементов И-ИЛИ пятого, четвертого и третьего разрядов, с шестыми входами элементов И- ИЛИ первого, шестого, второго и восьмого разрядов, с третьим входом элемента И- ИЛИ седьмого разряда, первый и второй управляющие входы выходного устройства связаны с соответствующими входами всех элементов И-ИЛИ выходного устройства, выходы устройства входной логики соединены с входами десяти элементов НЕ выходного устройства, выходы первого, десятого и девятого элементов НЕ соединены с входами первого и десятого элементов И-ИЛИ, выходы второго, девятого, первого и восьмого элементов НЕ подключены к соответствующим входам второго и девятого элементов И-ИЛИ, выходы третьего, второго, восьмого и седьмого элементов НЕ связаны с соответствующими входами третьего и восьмого элементов И-ИЛИ, выходы четвертого, третьего, шестого и седьмого элементов НЕ соединены с входами четвертого и седьмого элементов И-ИЛИ, выходы четвертого, пятого и шестого элементов НЕ подключены к соответствующим входам пятого и шестого элементов И-ИЛИ, выходы всех элементов И-ИЛИ связаны с, выходами выходного устройства, входы третьей группы входов блока формирования результата соединены в соответствующем разряде с входом одиннадцатого элемента НЕ выходного устройства, а также с соответствующими входами всех элементов И-ИЛИ, выход одиннадцатого элемента НЕ в каждом разряде подключен к соответствующим входам всех элементов И-ИЛИ.

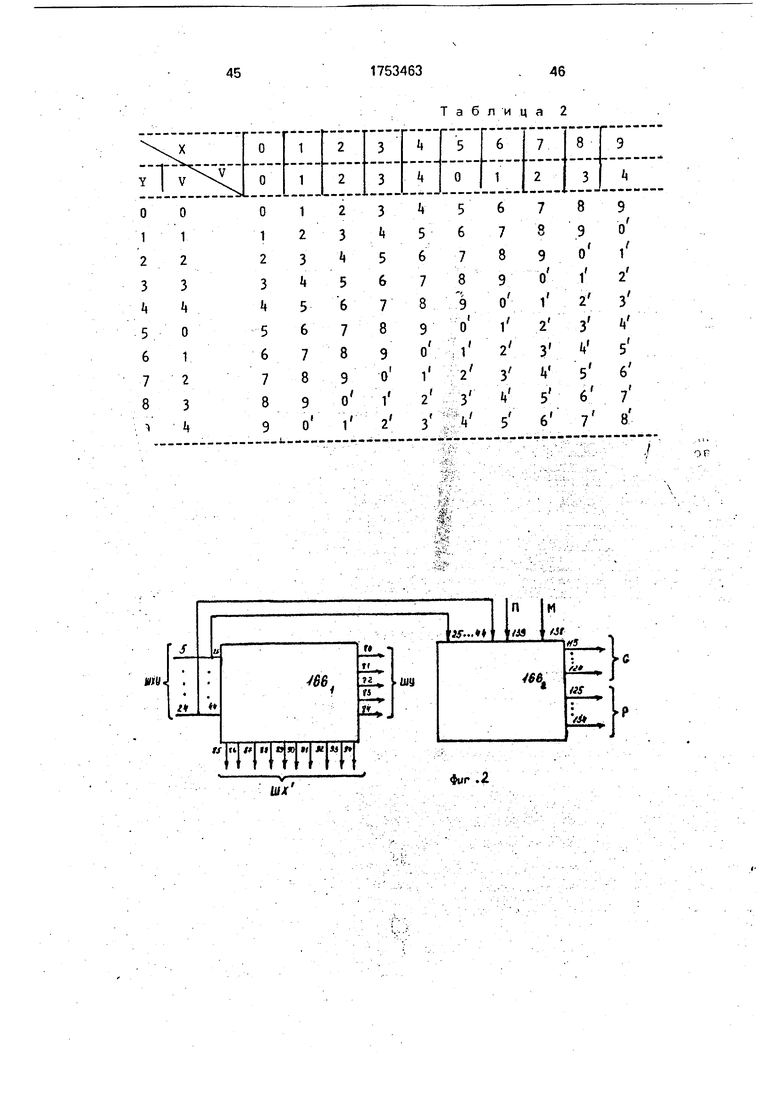

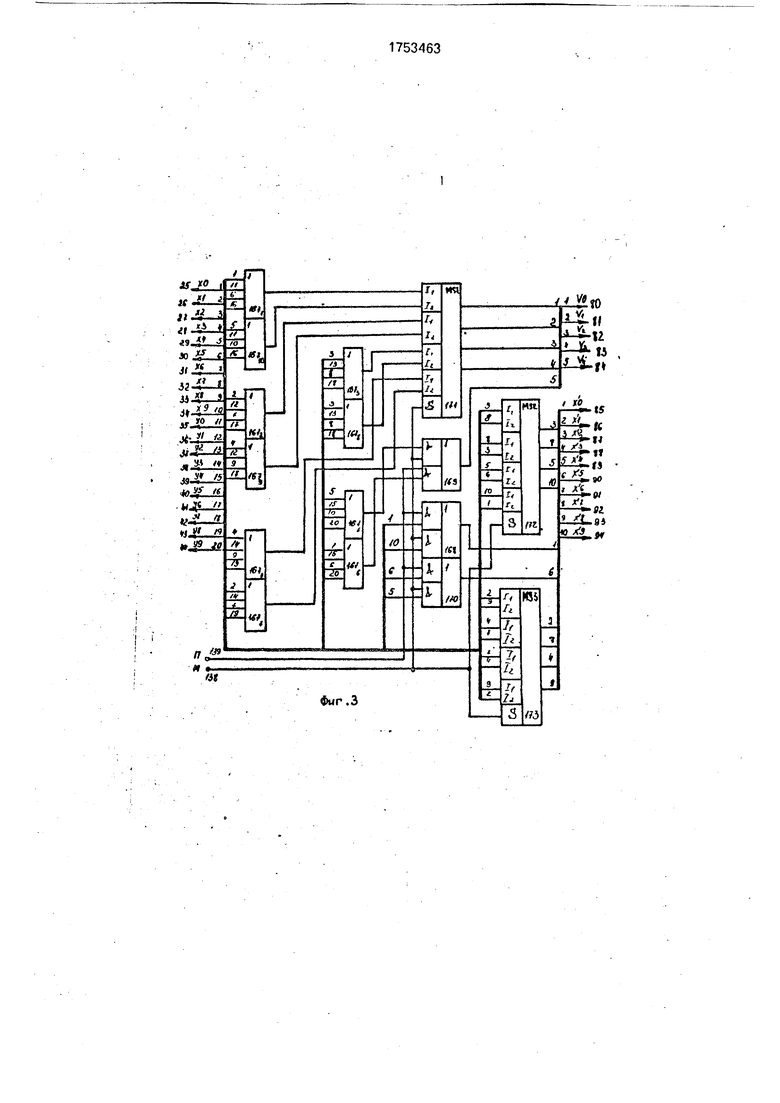

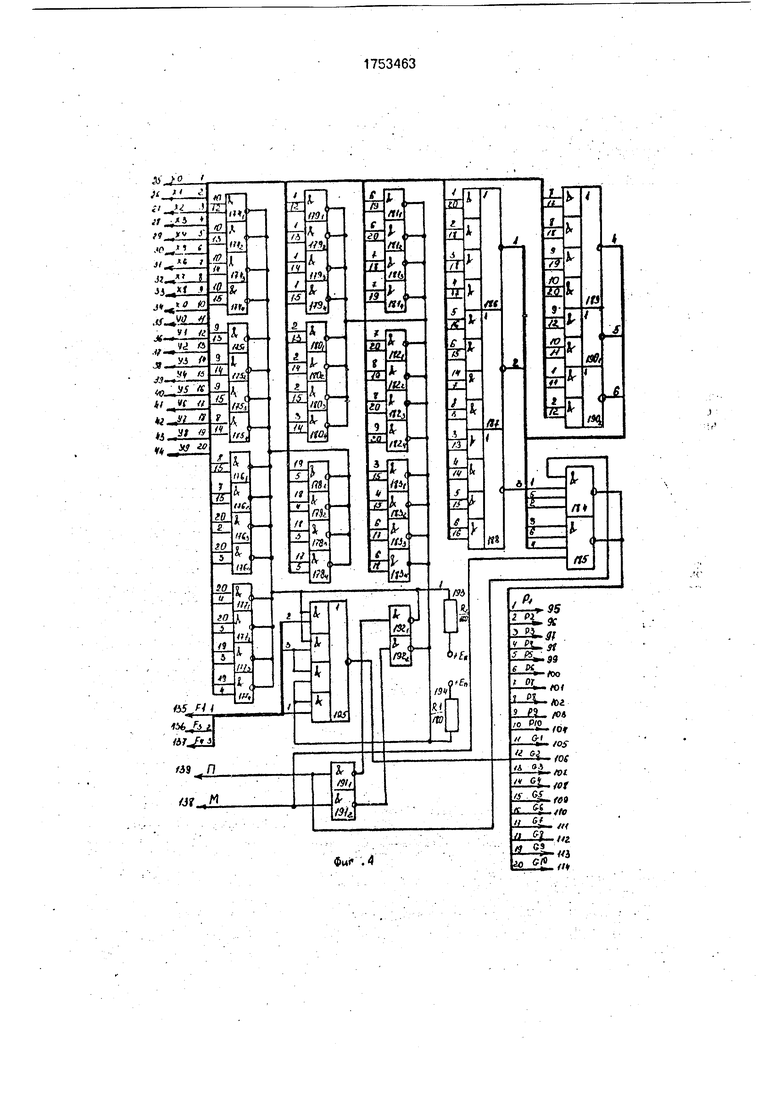

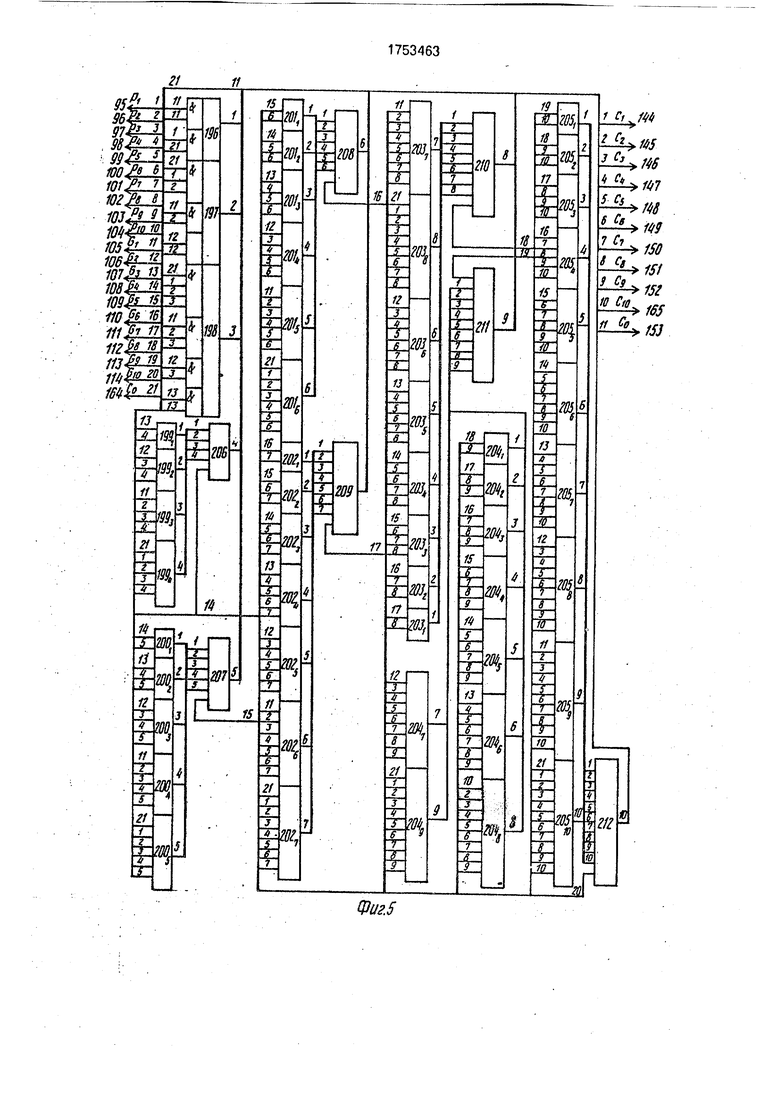

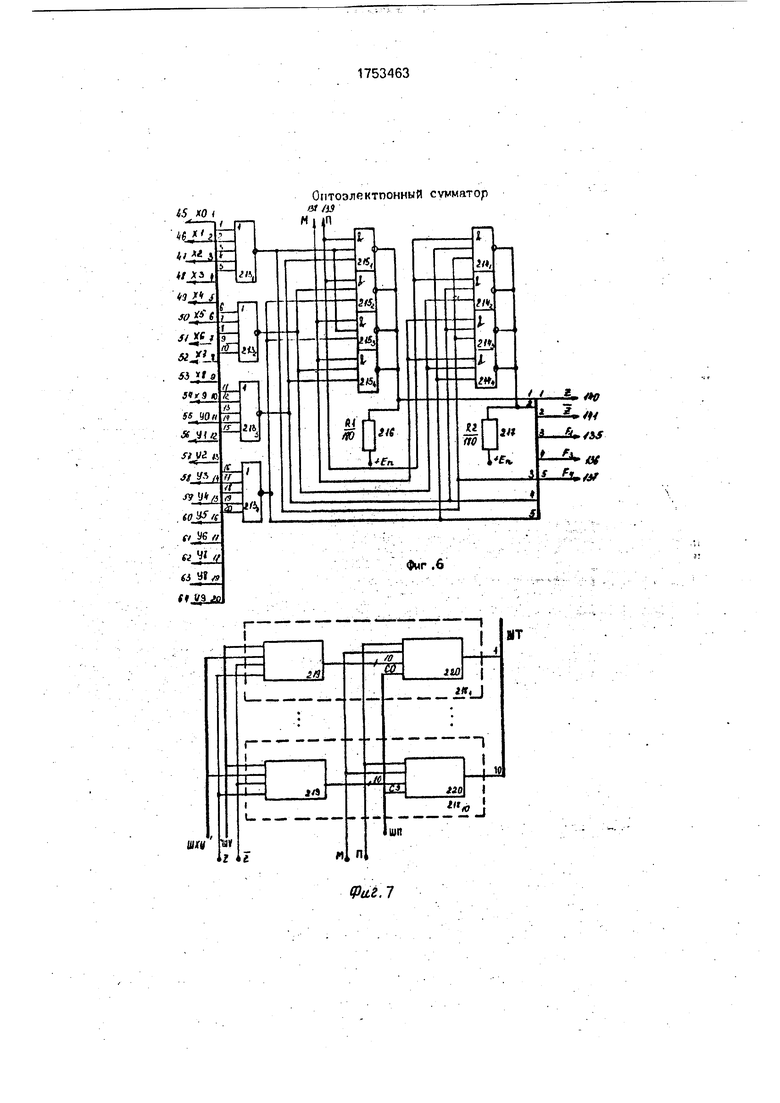

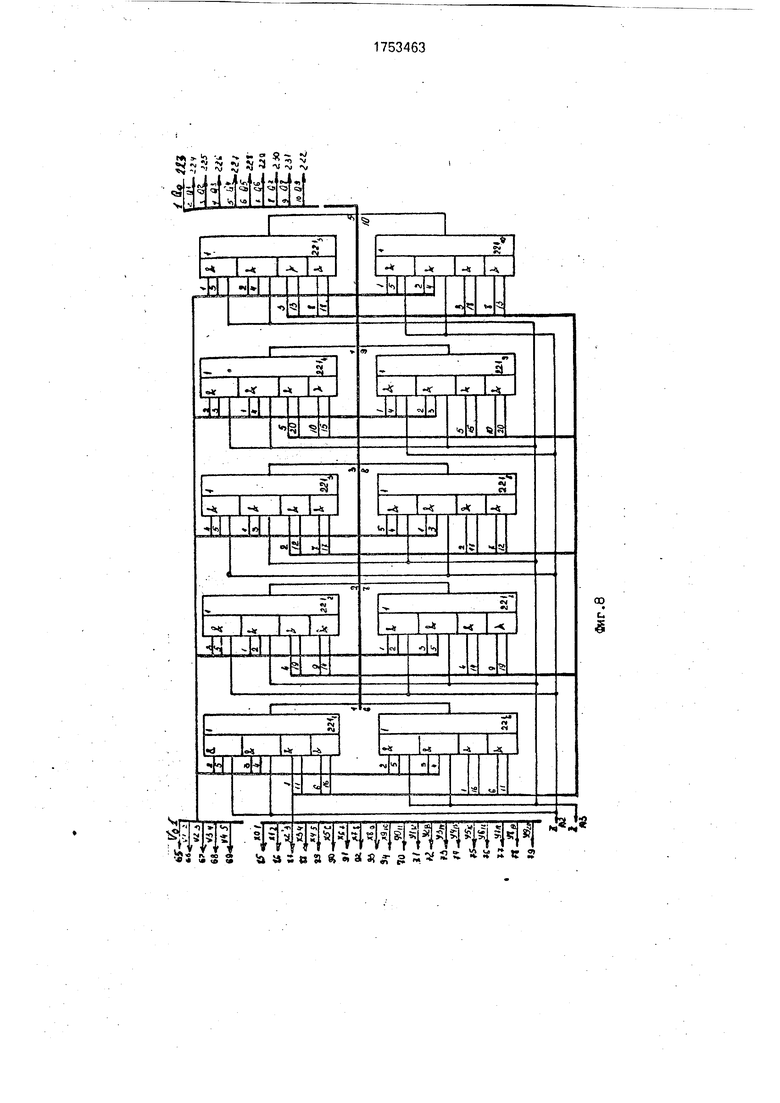

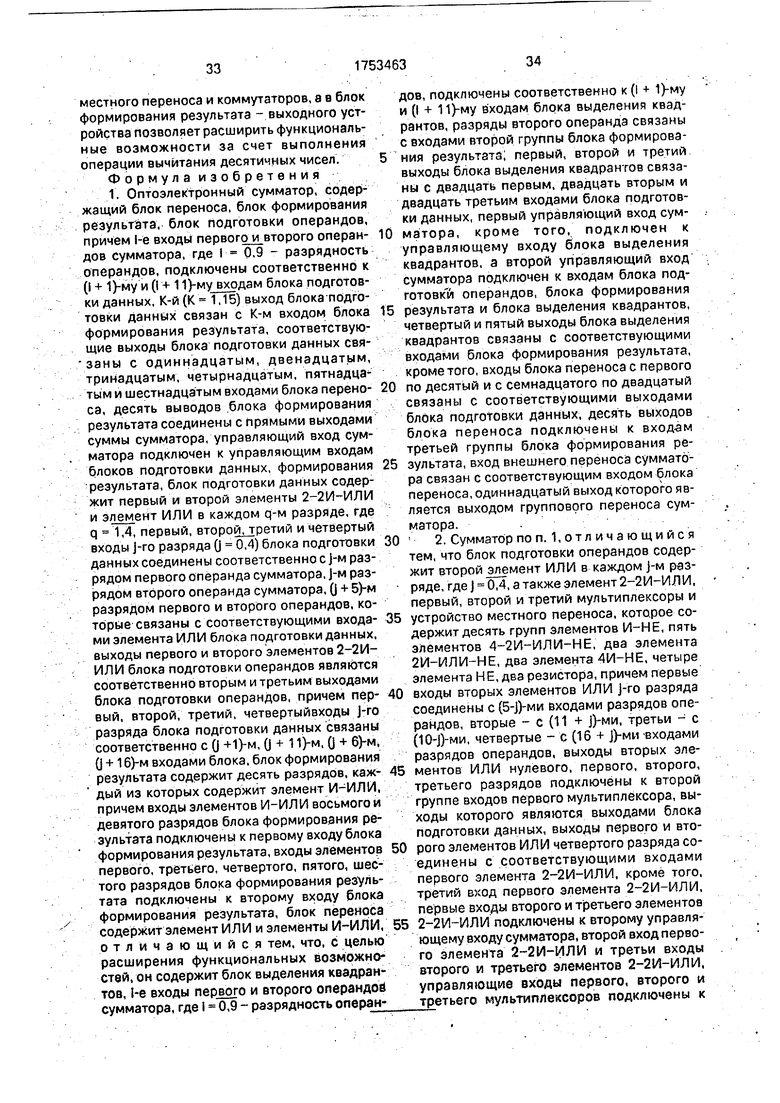

На фиг, 1 представлена структурная схема оптоэлектронного сумматора; на фиг. 2 - функциональная схема блока подготовки данных; на фиг. 3 - функциональная схема устройства расстановки 1-го разряда; на фиг. 4 - функциональная схема устройства местного переноса; на фиг. 5 - функциональная схема блока переносов; на фиг. 6 - функциональная схема блока выделения квадрантов; на фиг. 7 - структурно-функциональная схема блока формирования результата; на фиг. 8 - функциональная схема устройства входной логики; на фиг. 9 - функциональная схема выходного устройства.

Оптоэлектронный сумматор (фиг. 1) содержит блок 1 подготовки данных, блок 2 формирования результата, блокЗ переноса и блок 4 выделения квадрантов. Входы 5-14 первого операнда хо ,..., хд и входы 15-24

второго операндла уоуэ подключены соответственно к входам с первого по десятый 25-34 и с одиннадцатого по двадцатый 35- 44 блока 1 подготовки данных.а также подключены соответственно к входам с первого по десятый 45-54 и с одиннадцатого по двадцатый 55-64 блока 4 выделения квадрантов. Входы блока 2 формирования результата с первого по пятнадцатый 65-79

0 связаны с выходами с первого по пятый 80-84 блока 1 подготовки данных и с входами 15-24 второго операнда. Выходы 85-94 блока 1 подготовки данных подключены к входай блока 2 формирования результата.

5 Входы блока 3 переноса с первого по двадцатый 95-114 соединены с выходами с шестнадцатого по тридцать шестой 115-134 блока 1 подготовки данных, входы которого с двадцать первого по двадцать третий сое0 динены с выходами с первого по третий 135-137 блока 4 выделения квадрантов, а также с входами 138 и 139 устройств М и П (М 1 - вычитание, П 1 - сложение) соответственно, которые, кроме того, подключе5 ны к соответствующим входам блока 4 выделения квадрантов и блока 2 формирования результата. Выходы 140 и 141 блока 4 выделения квадрантов соединены с входами 142 и 143 блока 2 формирования резуль0 тата, входы которого, кроме того, подключены к выходам 144-153 блока 3 переноса. Выходы блока 2 формирования результата с первого по десятый 154-163 являются выходами результата. Двадцать

5 первый вход 164 блока 3 переноса соединен с входом переноса первого разряда Выход 165 блока 3 переноса является выходом группового переноса устройства.

Блок 1 подготовки операндов (фиг, 2)

0 содержит устройство 166i расстановки и устройство 1662 местного переноса.

Устройство 166i расстановки содержит десять разрядов. Функциональная схема I- го разряда устройства расстановки (фиг. 3)

5 содержит десять элементов ИЛИ 167i 167ю. три элемента 2И-ИЛИ 168-170, три мультиплексора 171-173. Первый - четвертый входы элементов ИЛИ 1671167 -ч

167s соединены соответственно с (25 + J)-M,

0 (35 + )-м, (30 + и (40 + j)-M входами блока 1 подготовки операндов, где j 0,4. Входы с первого по четвертый элементов ИЛИ 167е- 167ю связаны соответственно с (25 + )-м, (39-j)-M, (30 + J)-M и (44-j)-M (где j 0,4) вхо5 дами блока 1 подготовки операндов, выходы элементов ИЛИ 1671-1674 подключены к первому, третьему, пятому и седьмому входам мультиплексора 171 соответственно. Выход элемента ИЛИ 167s связан с первым входом элемента 2И-ИЛИ 169, выходы

элементов ИЛИ 1б7 -167ю соединены с вторым, четвертым, шестым и восьмым входами мультиплексора 171. Управляющие входы мультиплексоров 171-173, третьи входы элементов 2И-ИЛИ 168 и 170 и вто- рой вход элемента 2И-ИЛИ 169 подключены к входу 138 устройства. Вторые входы элементов 2И-ИЛИ 168, 170 и третий вход элемента 2И-ИЛИ 169 соединены с входом 139 устройства. Четвертый вход элемента 2И-ИЛИ 169 связан с выходом элемента ИЛИ 167е. Первый вход элемента 2И-ИЛИ 168 и восьмой вход мультиплексора t72 соединены с входом 25 блока подготовки данных, четвертый вход элемента 2И-ИЛИ 168, седьмой вход мульти :ексора 172 - с входом 34 блока 1 подготовки операндов, второй вход элемента 2И-ИЛИ 170 и шестой вход мультиплексора 172 подключены к входу 30 блока 1. Четвертый вход элемента 2И- ИЛИ 170 и пятый вход мультиплексора 172 соединены с входами 29 блока 1, Первый и четвертый входы мультиплексора 172 связаны с входом 27 блока 1, второй и третий - с входом 32. Первый и восьмой входы мульти- плексора 173 подключены к входу 26 блока 1 подготовки операндов, второй и седьмой - к входу 33, третий и шестой - к входу 28, четвертый и пятый - к входу 31 блока 1. Выходы мультиплексора 171 с первого по четвертый связаны с выходами 80-83 блока 1, выходы элементов 2И-ИЛИ 168-170 - с выходами 85, 84 и 90 блока 1 соответственно. Выходы мультиплексора 172 с первого по четвертый соединены с выходами 87, 92, 89 и 94 соответственно. Выходы мультиплексора 173 подключены к выходам 86, 91, 88 и 93 соответственно.

Устройство 1662 местного переноса состоит из десяти разрядов. Функциональная схема устройства местного переноса (УМП) (фиг. 4) содержит группы элементов И-НЕ 174i-1744, 1751-17541831-1834, два элемента 4И-НЕ 184 и 185, элементы 4-2И- ИЛИ-НЕ 186-189, два элемента 2-2И-ИЛИ-НЕ 1901 и 1902, элементы НЕ 1911, 1912, 1921,1922, резисторы 193 и 194 и элемент 4-2И-ИЛИ-НЕ 195. Первые входы группы элементов И-НЕ 174 -1744, третий вход элемента 2-2И-ИЛИ-НЕ 190i, седь- мой вход элемента 4-2И-ИЛИ-НЕ 189 подключены к входу 34 блока 1 подготовки операндов, вторые входы элементов И-НЕ 174i, 17&1, элемента 2-2И-ИЛИ-НЕ 190i, четвертый вход элемента 2-2И-ИЛИ-НЕ 1902 связаны с входом 36 блока 1 подготовки операндов. Вторые входы элементов И-НЕ 1742, 1792, 175i, 180i, элемента 4-2И-ИЛИ-НЕ 188 соединены с входом 37, вторые входы элементов 174з, 1752,1754.179з

1802,1804, пятый вход элемента 4-2И- ИЛИ-НЕ 187, четвертый вход элемента 4- 2И-ИЛИ-НЕ 188 подключены к входу 38 блока 1 подготовки операндов . Вторые входы элементов 1744, 1794, 175з, 176i. 1762,

1803,183i, 1832, четвертый вход элемента 4-2И-ИЛИ-НЕ 187, шестой вход элемента 4-2И-ИЛИ-НЕ 188 соединены с входом 39 блока 1 подготовки операндов. Четвертый вход элемента 2-2И-ИЛИ-НЕ 190i и второй вход элемента 2-2И-ИЛИ-НЕ 1902 связаны с входом 35 блока 1. Первые входы группы элементов И-НЕ 1791-1794, элементов 4- 2И-ИЛИ-НЕ 186и2-2И-ИЛИ-НЕ 1902 связаны с входом 25 блока 1, первые входы элементов И-НЕ 180i, 1802, 180з, второй вход элемента 176з, третьи входы элементов 186, 1902 подключены к входу 26 блока 1. Первые входы элементов И-НЕ 1804, 183i и элемента 4-2 И-И Л И-НЕ 188, вторые входы элементов И-НЕ 1764,177з, пятый вход элемента 4-2И-ИЛИ-НЕ 186, восьмой вход элемента 4-2И-ИЛИ-НЕ 187 связаны с входом 27. вторые входы элементов И-НЕ 177/1, 1782, третий вход элемента 4-2И-ИЛИ-НЕ

188,первый вход элемента И-НЕ 1782, седьмой вход элемента 4-2И-ИЛИ-НЕ 186 соединены с входом 28 блока 1, вторые входы элементов , 178i, 178з, 1784, первый вход элемента 4-2И-ИЛИ-НЕ 187, пятый вход элемента 4-2И-ИЛИ-НЕ 188 подключены к входу 29 блока 1, первые входы элементов И-НЕ 181, 1812, 183з, 1834, третий вход элемента 4-2И-ИЛИ-НЕ 187, седьмой вход элемента 4-2И-ИЛИ-НЕ 188 связаны с входом 30, первые входы элементов И-НЕ 1762, 181з, 1814, 182i, элемента 4-2И-ИЛИ- НЕ 189, шестой вход элемента 4-2И-ИЛИ- НЕ 187 соединены с входом 31. Первые входы элементов И-НЕ 1754, 176i, 1822, 182з, третий вход элемента 4-2И-ИЛИ-НЕ

189,седьмой вход элемента 4-2И-ИЛИ-НЕ 187 подключены к входу 32 блока 1 подготовки данных, первые входы элементов И-НЕ 1751-1753, 1824, элемента 2-2И-ИЛИ-НЕ 190i связаны с входом 33 блока 1 подготовки операндов. Второй вход элемента 4-2И- ИЛИ-НЕ 187, восьмой вход элемента 4-2 И-ИЛ И-НЕ 188 соединены с входом 40. первый вход элемента 1784, вторые входы элемента И-НЕ 183з и элемента 4-2И- ИЛИ-НЕ 189, восьмой вход элемента 4-2И- ИЛИ-НЕ 186 подключены к входу 41, вторые входы элементов И-НЕ 181з, 1834, первые входы элементов И-НЕ 1782, 178з, четвертые входы элементов 4-2И-ИЛИ-НЕ 186,189, шестой вход элемента 4-2И-ИЛИ- НЕ 186 связаны с входом 42, первые входы элементов И-НЕ 178i, 177з, вторые входы

элементов 4-2И-ИЛИ- НЕ 181i, 18U 1822,шестой вход элемента 4-2И-ИЛИ-НЕ 189 соединены с входом 43 блока 1 подготовки операндов, первые входы элементов И-НЕ 176з, 1764, 1771, 1772, вторые входы элементов И-НЕ 1812, 182i, 182з, 1824, элемента 4-2И-ИЛИ-НЕ 186. восьмой вход элемента 4-2И-ИЛИ-НЕ 189 связаны с входом 44, входы элемента И-НЕ 184 подключены к выходам элементов 186, 190i, 187 и входу 139 устройства. Входы элемента И- НЕ 185 связаны с выходами элементов 1902. 189, 188 и входом 138 устройства, входы элементов НЕ 1911, 1912 подключены к входам 139 и 138 соответственно, выходы эле- ментов НЕ 1911, 1912 связаны, с входами элементов НЕ 192т и 1922. Выходы групп

элементов И-НЕ 174i-1744, 175i-1754

178i-1784, элемента НЕ 192i подключены к первому и третьему входу элемента 4-2И- ИЛИ-НЕ 195, а также к первому выводу резистора 193, второй вывод которого соединен с шиной питания. Выходы групп элементов И-НЕ 1791-1794 1831-1834,

элемента НЕ 1922 связаны с шестым и седь- мым входами элемента 4-2И-ИЛИ-НЕ 195, а также с первым выводом резистора 194, второй вывод которого подключен к шине питания. Второй вход элемента 195 соединен с входом 136 блока 1 подготовки one- рандов 1, четвертый и пятый входы - с входом 137, восьмой - входом 135 блока 1. Выходы элементов 184, 185 и 195 подключены соответствующим образом к выходам 95-114 блока 1.

Блок 3 переноса (фиг, 5) содержит три элемента И-ИЛИ 196-198, группы элементов И 1991-1994, 200i-200s, 201i-201e, 2021-202, 203i-203e, 204i-204g, 205i-205io и элементы ИЛИ 206-212. Третий вход эле- мента 196, вторые входы элементов 197, 198, 1994, 200s, 201б, 202, 203s, 204д, 205ю соединены с входом 95 блока 3 переноса. Третий и пятый входы элементов 197 и 198, вторые входы элементов 199з, 2004, 2015, 202е, 203, 204в, 205д, третьи входы элементов 1994, 200s, 201б, 2027, 203а, 204д, 205ю связаны с входом 96 блока 3 переноса. Четвертый, седьмой и девятый входы элемента 198, вторые входы элементов 1992. 200з, 2014,202s, 203е, 204, 205в, четвертые входы элементов 200s, 201б, 202, 203s, 204д, 205ю, третьи входы элементов 199з, 2004, 201э, 202е, 203, 204в, 205д подключены к входу 97 блока 3 переноса. Вторые входы элементов 1991. 2002, 201з, 2024, 2035, 2046, 205,, третьи входы элементов 199з, 200з. 2014, 202б, 203б, 2047, 205s, четвертые входы элементов 199з, 2004, 201s, 202б, 203, 204в, 205э, пятые входы элементов 1994.200s.

201е, 2027, 203в, 204э, 205ю соединены с входом 98 блока 3 переноса. Вторые входы элементов 200i, 2012, 202з, 2034, 204s, 205б, третьи входы элементов 2002. 201з, 2024, 203s, 204e, 2057. четвертые входы элементов 200з, 20U, 202s, 203е. 204, 205а, пятые входы элементов 2004, 201s. 202е, 203, 204а, 205э, шестые входы элементов 200s. 201 е, 202, 203а, 204э, 205ю связаны с входом 99 блока 3 переноса. Вторые входы элементов 2011, 2022, 203з, 2044, 205s, третьи входы элементов 2012, 202з, 2034, 204s, 205e, четвертые входы элементов 201з, 2024, 203s, 204е, 205, пятые входы элементов 20U, 202б, 203е, 2047, 205s, шестые входы элементов 202е, 2037, 204в, 205э. 201s, седьмые входы элементов 201е, 202, 203в, 204д, 205ю подключены к входу 100 блока 3 переноса. Вторые входы элементов 202i, 2032, 204з, 2054, третьи входы элементов 202, 203з, 2044, 205s, четвертые входы элементов 202з, 2034, 204б, 205б, пятые входы элементов 2024, 203s, 204е, 2057, шестые входы элементов 202s, 203б, 204, 205в, седьмые входы элементов 202е, 2037,204в, 205д, восьмые входы элементов 202, 203s,204д,205ю соединены с входом 101, вторые входы элементов 2031.

2042,205з, третьи входы элементов 2032,

2043,2054, четвертые входы элементов 203з,

2044,205s, пятые входы элементов 2034, 204s, 205e, шестые входы элементов 203s,

2046,205, седьмые входы элементов 203е,

2047,205а, восьмые входы элементов 203, 204в, 205э, девятые входы элементов 203а, 204д, 205ю связаны с вхо дом 102 блока 3 переноса. Вторые входы 204i, 2052, третьи входы элементов 2042, 205з, четвертые входы элементов 204з, 2054, пятые входы элементов 2044, 205s, шестые входы элементов 204s, 205е, седьмые входы элементов 204е, 205. восьмые входы элементов 204j, 205s, десятые входы элементов 204з, 205э, десятые входы элементов 204э, 205ю подключены к входу 103 блока 3 переноса. Второй вход элемента 2051, третий вход элемента 2052, четвертый вход элемента 205з, пятый вход элемента 205л, шестой вход элемента 205s, седьмой вход элемента 205б, восьмой вход элемента 205, девятый вход элемента 205в. десятый вход элемента 2059, одиннадцатый вход элемента 205ю связаны с входом 104. Первые входы элементов 196, 199з, 2004, 201s. 202е, 203, 2048, 205э, второй вход элемента 196, четвертый вход элемента 197, пятый вход элементл.198 соединены с входом 105, первые входы элементов 1992, 200з, 2014,, 2025, 203б, 204, 205в, шестой и седьмой входы элемента 19Т, восьмой вход элемента 198 связаны с

входом 106 блока 3 переноса. Первые входы элементов 199i, 2002, 201з, 2024, 2035, 204е. 205, десятый и одиннадцатый входы элемента 198 подключены к входу 107. Первые входы элементов 2001, 2012,202з, 2034,204s, 205б, пятый вход элемента 206 соединены с входом 108. Первые входы элементов 2011, 2022, 203з, 2044, 205s и шестой вход элемента 207 связаны с входом 109, первые входы элементов 2021,2032, 204з, 2054 и седьмой вход элемента 208 подключены к входу 110, первые входы элементов 203i, 204a, 205з и восьмой вход элемента 209 соединены с входом 111, Первые входы элементов 204i, 2052, 210, связаны с входом 112, первый вход элемента 205i, девятый вход элемента 211 связаны с входом 113, первый вход элемента 212 соединен с входом 114, Четвертый вход элемента 196, первые входы элементов 197, 198, 1994, 200з, 201б, 202, 203s, 204g, 205ю подключены к входу 164 блока 3 переноса. Выходы элементов 199t- 1994 связаны с входами элемента 206, выход которого соединен с выходом 147 блока переноса, выходы элементов 200i-2005 подключены к входам элемента 207, выход которого является выходом 148 блока переноса. Выходы элементов 2011-201е связаны с входами элемента 208, выход которого соединен с выходом 149 блока 3 переноса. Выходы элементов 2021-202 подключены к входам элемента 209, выход которого является выходом 150 блока 3 переноса. Выходы элементов 203i-203s связаны с входами элемента 210, выход которого является выходом 151 блока 3 переноса. Выходы элементов 204i-204g соединены с входами элемента 211, выход которого подключен к выходу 152 блока 3 переноса. Выходы элементов 2051-205Ю связаны с входами элемента 212, выход которого является выходом 165 блока 3 переноса. Выходы элементов 196-198 подключены к выходам 144-146 блока 3 переноса соответственно. Вход 164 подключен к выходу 153 блока 3 переноса.

Блок 4 выделения квадрантов (фиг. 6) содержит группы элементов ИЛИ-НЕ 213i- 2134, И-НЕ 2151-2154, 2141-2144. Выходы элемента 213i с первого по пятый соединены с входами 45-49 блока 4 выделения квадрантов, выходы элемента 2132 с первого по пятый - с входами 50-54, выходы элемента 213з - с входами 55-59, выходы элемента 2134-с входами 60-64, вторые входы элементов 215i, 215з, третьи входы элементов 214i, 214з и выход 135 блока выделения квадрантов подключены к выходу элемента 2131, «торые входы элементов , 2154,

2144, третий выход элемента 2142 и выход 136 блока 4 выделения квадрантов связаны с выходом элемента 2132.

Третьи входы элементов 215i, 2154, вторые входы элементов 2142, 214з соединены с выходом элемента 213з. Выход элемента 2134 связан с третьими входами элементов 2152, 215з, 2144, вторым входом элемента

214i и с выходом 137 блока 4 выделения квадрантов. Первые входы элементов 215з, 2154, 214, 2142 подключены к входу 138 устройства, а первые входы элементов 215i, 2152. 214з, 2144 соединены с входом 139

устройства.

Выходы элементов И-НЕ 2151-2154 соединены с первым выводом резистора 216, а также с выходом 140 блока.

вторые выходы резисторов 216 и 217 подключены к шине питания. Выходы элементов И-НЕ 2141-2144, первый вывод резистора 217 связаны с выходом блока 141.

Блок 2 формирования результата (фиг. 7} содержит десять разрядных ячеек 218i- 21810, каждая из которых состоит из устройства 219 входной логики и выходного устройства 220.

Устройство 219 входной логики 1-го разряда (фиг, 8) содержит десять элементов И- ИЛИ 2211-221 ю. Первые входы элементов И-ИЛИ 2217, 221э, 2215, 221 ю, третьи входы

элементов И-ИЛИ 2212,221з, 22U 221sсоединены с входом 65 устройства 219 входной логики. Первые входы элементов И-ИЛИ

2211,2214, 221е, второй вход элемента И- ИЛИ 221, пятый вход элемента 2212. четвертые входы элементов 221s, 221g, 221 ю связаны с входом 66, первый вход элемента

2212,второй вход элемента 2214, четвертые входы элементов 2211,221 е, 221 , пятые входы элементов 221з, 221э, 221е, подключены

к входу 67, вторые входы элементов И-ИЛИ 221s, 221g, первый вход элемента 221з, пятые входы элементов 2211, 2214, 221б, 221е, 221 ю соединены с входом 68, первый вход элемента 221а, вторые входы элементов

2211, 2212. 221з, 2215, 221в. 221 ю, пятый вход элемента 221 связаны с входом 69, седьмые входы элементов 221е, 221i подключены к входу 85 блока 2 формирования результата. Седьмые входы элементов 221з,

221а соединены с входом 86, элементов 221s, 221 ю - с входом 37, элементов 2212, входом 88, элементов 2214, 221э-с входом 89, девятые входы элементов 2211, 221б соединены с входом 90, элементов

221з. 2218-с входом 91, элементов 221s и

221 ю - с входом 92, элементов 2212, 221 с входом 93, элементов 2214 и 221д - с входом 94. Восьмой вход элемента 2211, десятый вход элемента 221е подключены к входу 70 блока формирования результата. Вось- 5 мой вход элемента 221з, десятый вход элемента 221в связаны с входом 71 блока формирования результата. Восьмой вход элемента 221s и десятый вход элемента 221 ю соединены с входом 72, восьмой вход 10 элемента 221, десятый вход элемента 2212 подключены к входу 73, а восьмой вход элемента 221 б и десятый вход элемента 2211 - к входу 75, восьмой вход элемента 221 а и десятый вход элемента 221з - к входу 76, 15 восьмой вход элемента 221 g и десятый вход элемента 2214-к входу 74, восьмой вход элемента 221 ю и десятый вход элемента 221s - к входу 77, восьмой вход элемента 2212 и десятый вход элемента 221 - к входу 78, 20 восьмой вход элемента 2214 и десятый вход элемента 221д - к входу 79 блока. Третьи . входы элементов И-ИЛИ 221i-221s, 221y, 221д, 221 ю и шестые входы элементов И-ИЛИ 2211, 221 ю, 221а соединены с входом 25 142 блока 2 формирования результата. Третьи входы элементов И-ИЛИ . 221а, шестые входы элементов И-ИЛИ 2212-221, 221д подключены к входу 143 блока 2, Выходы элементов И-ИЛИ 221 i-221g соединены 30 с выходами 223-231 устройства 219 входной логики, а выход элемента И-ИЛИ 221 ю - с выходом 222 устройства 219.

В ыходное устройство 220 (фиг, 9) содер- жит элемент НЕ 232, группы элементов НЕ 35 2331-233ю и десять элементов И-ИЛИ 234i-234io. Входы элементов НЕ 233i-233io соединены с выходами 233,..., 231, 222 устройства 219 входной логики. Вход элемента НЕ 232 связан с входом (144 + j) в каждом 40 j-м разряде. Первые и четвертые входы элементов 234i-234io подключены к выходу элемента НЕ 232. Вторые входы элементов 234i-234io, восьмые входы элементов 234i- 234s и седьмые входы элементов 45 соединены с входом 139 устройства, шестые и одиннадцатые входы элементов 234i- 234ю связаны с входом 138 устройства. Седьмые и десятые входы элементов 234i- 50 234s, 234g, девятые и десятые входы элементов , 234ю подключены к входу элемента НЕ 232. Третий вход элемента 234i, девятый вход элемента 234г, двенадцатый вход элемента 234д, пятый вход эле- 55 мента 234ю соединены с выходом элемента НЕ 233i. Третий вход элемента 2342. девятый вход элемента 234з, двенадцатый вход элемента 234е, пятый вход элемента 2349 связаны с выходом элемента НЕ 233а. Третий вход элемента 234з, девятый вход элемента 2344, двенадцатый вход элемента 2347, пятый вход элемента 234е подключены к выходу элемента НЕ 233з- Третий вход элемента 2344, девятый вход элемента 234s. двенадцатый вход элемента 234е, пятый вход элемента 234 соединены с выходом элемента НЕ 2334- Третий и двенадцатый входы элемента 234s, пятый и восьмой входы элемента 234е связаны с выходом элемента НЕ 233s, третий вход элемента 234е. пятый вход элемента 234s, двенадцатый вход элемента 2344, восьмой вход элемента 234 подключены к выходу элемента НЕ 233е.. Двенадцатый вход элемента 234з, пятый вход элемента 2344, третий вход элемента 234, восьмой вход элемента 234s соединены с выходом элемента НЕ 233. Пятый вход элемента 234з, двенадцатый вход элемента 2342, третий вход элемента 234а. восьмой вход элемента 234э связаны с выходом элемента НЕ 233в. Двенадцатый вход элемента 234i, пятый вход элемнта 2342, третий вход элемента 234д, восьмой вход элемента 234ю подключены к выходу элемента НЕ 233д. Пятый и девятый входы элемента 234, третий и двенадцатый входы элемента 234ю соединены с выходом элемента НЕ 233ю. Выходы элементов 2341-234ю являются выходами 154-163 результата.

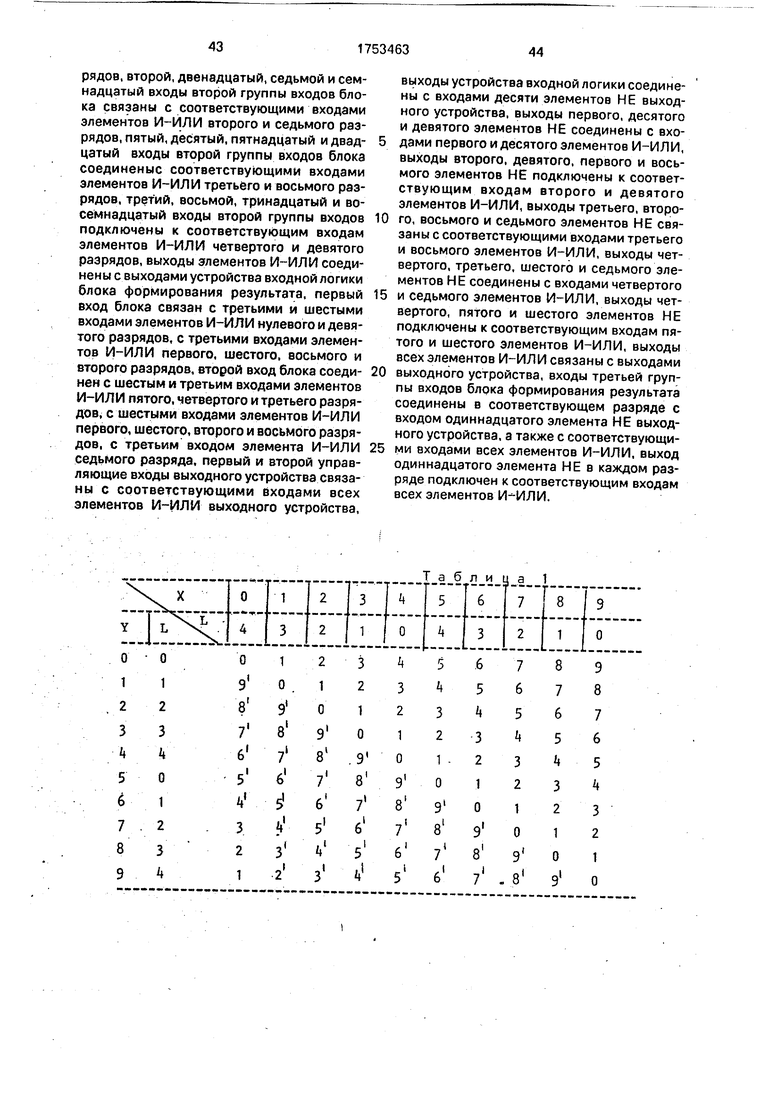

Сумматор-вычитатель функционирует в соответствии с таблицей вычитания (х-у, табл. 1), и таблицей сложения (х + у, табл. 2), Операнды представляются в единично-позиционном коде.

Из табл. 1 видно, что она симметрична и ось симметрии проходит через диагонали первого и третьего квадрантов и центр. Точно также таблица сложения имеет ось симметрии, но проходящую через второй и четвертый квадранты и центр. Номера квадрантов обозначаются следующим образом:

Единицами в верхних углах клеток табл. 1 и 2 обозначены в первом случае - заем, во втором - перенос.

Сумматор работает следующим образом.

На входы 5-14 и 15-24 подают входные сигналы операндов хохд и уоуд соответственно. При выполнении операции сложения единичный сигнал поступает на вход 139 (П 1), а при вычитании - на вход 138 (М 1). На входы 25-44 устройства расстановки 1-го разряда подаются сигналы хо,..., хд уоуэ

соответственно. Информационные сигналы с входов 25-44 устройства рэсстандвки поступают на входы элементов ИЛИ 167i- 167ю. На выходах элементов 167i-167s ре- ал изуются функции соответственно Vo, Vi, V2 , V3 , V41 (фиг. 3):

Vo xotyovxsvys; Vi xivyivxeyye;

V21 X2vy2VX7vy7;

Vaj хзчуз Х8 у8,

(1)

VV X4vy4vX9 y9.

а на выходах элементов 1676 167ip реализуются функции соответственно lU. Ьз l Li jLo1:

L4j XoVy4VX5Vy9

Ц xTvywevys;

L2 X24y2VX7vy ;(2)

Ki xavytvxevye;

Lo X4vy(yX9vy5,

где V)1- слагаемые при сложении;

L| - сформированные операнды при вычитании.

В v и LI входят одни и те же значения У1 и yj+5, в то время как относительно разрядов х, входящих в Vi1 и Li1, наблюдается следующая закономерность: xi и xi+s заменяются на X4-I и хэ-1 соответственно. При выполнении операции сложения М О, П 1 (вычитания М 1, П 0) на выходы 80-83 устройства расстановки поступают сигналы с первых (вторых) входов мультиплексора 171, на выход 84 - с первого (четвертого) входа элемента 169, на выходы 85-94 - сигналы с вторых (четвертых) входов элементов 168 и 170, а также с первых (вторых) входов мультиплексоров 172 и 173. На входы устройства местного переноса с входов 25-44 блока подготовки данных поступают сигналы XQ-ХЭ, уо-уэ соответственно, а также с выходов 135-137 блока выделения квадрантов поступают сигналы Ft, Fa, F4 (фиг. 4). Устройство формирует сигналы местного переноса (заема) в l-м разряде Gt(l 1,10). Перенос вычисляется в соответствии с табл. 2 в первом и третьем квадрантах:

Qn (хад)(Х9 Х «УзХх9У4ХХ8У 2) X X (Х8УЗХХ8У 1ХХ7УЗ)(Х7:У4ХХ6У4) X (Х У9ХХ2У9ХХЗУ9ХХ4У9ХХ2У8) х Х(ХЗУ8(Х4У7ХХ4У6)П.(3)

Переносы четвертого квадранта, как видно из табл. 2, находятся во всем этом квадранте, в любой его клетке. Поэтому достаточно установить принадлежность пары операндов четвертому квадранту, чтобы говорить о наличии единицы переноса. Сигналы с входов 25-44 поступают на входы

10

элементов ИЛИ-НЕ 174i-174 183i1834. На выходах элементов ИЛИ-НЕ 1741-1744,..., 1831-1834 соответственно реализуются конъюнктивные члены выражений (3) и (4), так на выходе элемента 174i реализуется функция xgTyi, на выходе элемента 1742-Х9ЛУ2 и т.д. Заем вычисляется на основании табл. 1 вычитания во втором и четвртом квадрантах (фиг. 4):

дз - (хоу1Ххоу2ХхоузХхоу4Хх1У2)

(Х1УЗХХ1У4ХХ2УЗХХ2У4ХХЗУ4) X (Х5УбХх5у7Хх5У8Хх5У9Хх 6У7) Чх Ххб ХхГУ8Хх7У9Хх8У9)-М.(4)

Заемы третьего квадранта присутствуют в каждой клетке этого квадранта. Первый и второй вентили (при обнуленных третьем и четвертом вентилях) элемента И-ИЛИ-НЕ 195 позволяют реализовать единицу пере- носа на выходе элемента И-ИЛИ-НЕ 195 (фиг. 4):

6| (Из И4 0) .

(5)

30 Третий и четвертый вентили (при обнуленных первом и втором вентилях Hi Из 0) элемента И-ИЛИ-НЕ 195 реалузуют единицу заема на выходе элемента 195 (фиг. 4):

Д

35 Gi(Hi И2 - 0) Р4дз v Fig3,

(6)

. Таким образом, на основании (6) и (5) получают результат

G i gnFn v Р4дз v Fig3 v F4gn . (7)

Функция (7) реализуется на выходе элемента 195. Кроме того, при формировании переноса в каждый разряд для многоразрядного сумматора (или заема для вычитания) необходимо знать разряды, в которых сумма равна девяти (нулю). На выходах элементов 184 и 185 реализуется функция (фиг.

4):

Pi (ХОУЭ V Х1У8 V Х2У7 V ХЗУ6 V Х4У5 V V Х5У4УХ6УЗV Х7У2 V Х8У1V Хдуо) П V V (ХОУО VXiyi V Х2У2 /ХЗУЗ V Х4У4У X5y5V V Х6У6 V Х7У7V 8У8 V Х9У9 ) М.(8)

На входы 45-64 блока 4 выделения квадрантов подаются входные сигналы операндов хо-хэ, соответственно, которые поступают на входы элементов ИЛИ-НЕ 2131-2134, на выходах которых соответствен но реализуются функции (фиг. 6):

Fl д XQYX1 VX2 V ХЗ V X4I

F2 Х5 v хб V х i XB v xg; Рз ° уо v yi v у2 Туз v У4: F4 V6vy7vy8vyg.

Сигналы с выходов элементов 213i 2134 поступают на входы элементов 215i 2154, 2141-2144, на выходах 140 и 141 которых формируются сигналы (фиг. 6):

Z ( V F3F4) П V (FlFz V РзР4Щ

Z (FiF4 V РзР2)Пч (FiF2vF3F4)M. (10)

Сигналы с выходов элементов 213i, 132, 2134, подаются на выходы 135, 136 и 137 блока 2. Рассмотрим четыре примера. Пусть х 2. у 3, тогда FI О, F2 0. Рз 1, F4 1, Z О, Z i gn 1 и, следовательно, Gi 1(1 vi) 0, т.е. сигнал переноса отсутствует при прохождении операндов во втором квадранте. Пусть х 2, у 8, тогда FI О, F2 1, Рз - 1, F4 О, Z I, Z 0, gn О следовательно, Gi 0(1YO)1, т.е. сигнал переноса присутствует. Пусть х б, у .3, тогда FI 1, F2 О, F3 О, F4 - 1. .Z 0, gn 1, следовательно G, 1() О, т.е. перенос отсутствует и, наконец х 5, у 8, тогда FI 1, F2 1, Рз О- F4 0, gn 1 и Gi 1(0 V 07 1,т.е. сигнал переноса присутствует.

Блок 3 переноса работает следующим образом.

На входы подаются сигналы, сформированные в устройстве местного переноса, Р; и Gi, I 1,10. На вход 164 поступает сигнал внешнего переноса Со. Сигналы переноса в каждый разряд I + 1 соответствуют сигналам Ci полученным на выходах элементов И-ИЛИ 196-198, ИЛИ 206, 207-212 следующим образом: на выходе элемента 196 реализуется функция

Ci GiVP1 Go,(11)

на выходе элемента 197

C2 G2VP2GlVGoP2Pb(12)

на выходе элемента 198

C3 G3VP3G2vP3P2GiVp3P2PiG0. (13) На выходах группы элементов 19 -1994 реализуются конъюнктивные члены функции (фиг. 5):

С4 G4 P4G3vP4P3G2VP4P3P2GlV

V Р4РзР2Р1Со..(14)

Так на выходе элемента 199т реализуется конъюнкция СзлР4. на выходе элемента 1992 - С2РзР и т.д. На выходах группы элемен-, тов 200i-200s реализуются конъюнктивные члены функции

Сб - G5 P5G4VP5P4G3 P5P4P3G2V VP5P4P3P2GfP5P4P3P2PlG0.(15)

(9)

на выходе элемента 207 - функция Сг) На выходах элементов 208-212, формируются сигналы, соответствующие функциям (фиг. 5)

Се - Сб v P6Gs V Р6РбС4 V P6P5P4G3V

УРбР5Р4РзС#РбР5Р4РзР2б№оР1Р2РзР4Р5Рб.

10 С G#P7G6VP7P6G P7P6P5G4VP7P6P5P4G3V V Р7РбР5Р4РзС Р7РбР5Р4РзР2С1У УР7РбРбР4РзР2Р1Со;

Св G8vP8G7VPeP7G6vP8P7P6G P8P7P6P5G4V 15v P8P7P6P5P4G3VP8P7P6P5P4P4P3G2V

УР8Р7РбР5Р4РзР2С Р8Р7РбР5Р4РзР2Р2Р1Со:

(16)

Cg G9VP9G P9P8G7VP9P8P7G6vP9PflP7P6G5V V РдРвР7 РбР§С4УР9Р8Р7РбР5Р4СзУ УРдР8Р7РбР5Р4РзС2у V P9P8P P6P5P4P3P2GlV V Р9Р8Р РбР5Р4РзР2Р2 PlGoI Сю G10YP10G9VP10P9G2VP10P9P8G7V

V P10P9P8P G P10P9P8P7P6G5V VG4P5P6P7P8PgPlOVG3P4P5P6P7P8P9PlOV

V С2РзР4РбРбР7Р8Р9РюУ V GlP2P3P4PsP6P7P8P9PlOV V СоР1Р2РзР4РбРбР7Р8Р9Рю

Конъюнктивные члены функции Се,

реализованы на выходах элементов И 201i-2016, 202i-2027, 203i-2038.

204i-204g, 205i 205io. Сигналы с выходов элементов 201i-201e поступают на входы элемента 208, с выходов элемента 2021-202 - на входы элемента 209, с выходов элементов 203i-203s-на входы элемента 2101,свыходов элементов 204i-204g - на вход элемента 211, с выходов элементов 205i 205io - на входы элемента 212. В блоке 3 переноса преобразование информации происходит в два этапа. Вначале параллельно формируются

конъюнктивные члены для каждого Q, а уже затем формируется дизъюнкция полученных конъюнкций. В блоке 3 переноса одинаково происходит обработка как сигналов переноса (при сложении), так и сигналов зэема (при

вычитании), так как и тот и другой поступают в блок переноса в виде сигналов. Всю совокупность полученных при сложении двух чисел значений можно представить следующими выражениями нЈ основании

таблицы сложения, причем Vi Vi, LI Li. QVo - Z(ViV4vV2V3)vxoyovx5y5;

QV1 ZV2V4VZVoVlVX3y8YX8y3: QV2 ZVsV4VZVoV2VXiyiVX6y6; QV3 Z(VlV2V VoV3)VX4y9VX9y4; QV4 - Z(VlV3V VoV4JVX2y2VX7y7:

QVg Z(VoV4v /2V3)Vxoy5VX5yo;

Z VoVi YZV2V3V xsyav xsys; (17) QV Z VoV2vZV3V4Vxiyevxeyi; QVe Z(VoV3YViV2)vx4ygvx3yg;

QVg Z(VoV4VViV3JYX2y7VX7y2

где QVi - сумма двух чисел, равная I, на основании принадлежности обоих операн- дов к одному из квадрантов Z или/ и величины слагаемого расстановки Vi, Также сумма определяется операндами, значения которых лежат на оси симметрии xiyi или на диагонали третьего и первого квадрантов

Х(УН-5(Х|+5У|).

Разности, полученные при вычитании двух чисел, определяются на основании таблицы вычитания, причем QU - величина разности, равная I, Определение QU производится также на основании принадлежности операндов к одному из квадрантов и величины U. Кроме того, разность определяется значениями операндов, лежащих на оси симметрии вычитания X4-I уэ-1, или на диагоналях второго и четвертого операндов, параллельных оси симметрии вычитания:

QLo Z(LoL4vUL2)vX9y2YX7y7;

QLi Z(LoL3YI 2Li)vxoy9vX5y4,

Z LoL2VZUt-3vX3yiVX8y6:

QL3 ZLoLi ZUL2vx6y3Vxiy8; . (18)

QU Z(ULlVL3l 2)YX4yOVX3y5;

QLs Z(l 2UvL3Li X7y2VX2y7;

QLe Z(l 3Lo4L2Li)vxoy4YX5y9;

QL Z LoL2vZUL3 xayivx3y6;

QU Z LoLiYZUL 2vxiy3VX6y8,

QLg Z(LiL4vL3L2)vxgy9VX4y5.

Формально записном и QU совпадают при сомножителях Z и 2 в выражениях (17) и (18) в случаях: I 0 и j 9; I 1 и j 8; j 7 и l 2;i 3 и j 6; i 4 и j 5; i 5 и J 4; i 6HJ 2;t 8nj 1; f 9nj 0, а величины Z в (17) инверсны значениям Z при указанных I nj в выражениях (18).

Кроме того, дизъюнкции конъюнкций х и у в этих выражениях при указанных номерах также имеют свои особенности. Величины у( и yj совпадают, а х, находящиеся при них, заменяются - Х2 на х, х на Х2, Х4 на xs, хэ на хо, xi на ха, хе на хз, хз на хе, ха на XL

Таким образом, заменяя Vt на U и произведя указанные замены х, инвертируя при этом значение Z в выражениях для QVi, получают значения J-x разрядов разности. Поэтому в устройстве расстановки 1-го разяда (фиг. 3) мультиплексором 271 ияроизводит- ся коммутация Vo Vi v Vs при суммировании (Lo Li L La1 при вычитании) на выходную шину UJVi,a V и коммутируются на эту же шину элементом ИЛИ 169, Разряды х коммутируются двумя мультиплексорами 172 и 173 на шину Шх у, а в блоке выделения квадрантов (фиг. 5) при вычитании через

группы элементов И-НЕ 214 и 215 коммутируются на шинуZзначения, противоположные значениям при сложении,

Входные операнды х, преобразованные

в устройстве расстановки, с выходов 85-94 поступают на входы блока 2 формирования результата, на выходы 70-79 которого подаются информационные сигналы уо...уэ. На входы 221i-221 ю каждого разряда устрой0 ства 219 входной логики поступают информационные сигналы с шин HIV и Шх у 70-79, 85-94, На выходах элементов И-ИЛИ 2211- 22110 формируются сигналы, реализующие функции соответственно (фиг. 8);

0

(19)

5 Qo ZVi V4A/2V3Zvxl0yo xl5y5 Qj ZV2V4vZVoViVx зух еуз;

02 ZV3V4vZVoV2Vxi yivxeye;

03 Z(ViV2YVoV3 x Wxg У4,

Qj - Z(VbV4VVlV3JVX2 У2уХ7 у7;

Qj Z(ViV/ivV2V3)vxoly5vx5lyo; Q§ Z VoV VZV2V3VX3 ysvxs ya; Q Z VaV4 2VoV2Vxi yevxe yi; Qj Z VoV3vZVi уч хэ уэ:

Qg Z( У7УХ7)У25 Сигналы Qi(i 0,9) подаются с выходов 223- 231, 222 устройства 219 входной логики на входы выходного устройства 220 и через инверторы 233i 233io поступают на. входы элементов 234i 234io. В выходном устрой- 0 стве происходит коммутация соответствующих разрядов на выход устройства, так как на устройстве входной логики реализуется или сложение, или вычитание. Причем, если сигнал переноса Ск 0, то коммутация на 5 выход сумматора-вычитателя производится в соответствии с (17) при суммировании, т.е. TI QI, тогда при вычитании в соответствии c(18)Ti Qg-i. При наличии сигнала переноса Ск 1 на выход TI коммутируется при сложе- 0 нии значение QM, т.е. Т QM, а при вычитании значение Qe-i, а для Тд в этом случае - Qg. Таким образом (фиг. 9): Т0 C(nQoVMQg C(nQgYMQ8); TI C(nQivMQ8)vC(nQoVMQ7); 5 T2 C(nQ2YMQ7 C(nQivMQ6);

Тз C(nQ3VMQ6)vC(nQ2vMQ5); (20) T4 C(nQ4vMQ5)vC(nQ3vMQ4); Ts C(nQ5VMQ4 C(nQ4WIQ3); Те C()vC(nQ5vMQ2 ); 0 Т C(nQ7vMQ2 C(nQeVMQ 1);

Те C(nQЈf MQi)vCfnQ7vMQo);

Tg C(nQ9vMQo)vC(nQ8VMQg).

Функции (20) реализуется на выходах элементов 234t 234io, с выходов которых 5 подаются на выходную шину ШТ - результата (выходы 154-163).

Введение в схему оптоэлектронного сумматора блока выделения квадрантов с соответствующей структурой, а также введение в блок подготовки данных устройства

местного переноса и коммутаторов, а в блок формирования результата - выходного устройства позволяет расширить функциональ- ные возможности за счет выполнения операции вычитания десятичных чисел.

Формула изобретения 1. Оптоэлектронный сумматор, содержащий блок переноса, блок формирования результата, блок подготовки операндов, причем 1-е входы первого и второго операн- дов сумматора, где 1 0,9 - разрядность операндов, подключены соответственно к (I + 1)-му и (I + 11)-му входам блока подготовки данных, К-й (К 1,15) выход блока подготовки данных связан с К-м входом блока формирования результата, соответствующие выходы блока подготовки данных связаны с одиннадцатым, двенадцатым, тринадцатым, четырнадцатым, пятнадцатым и шестнадцатым входами блока перено- са, десять выводов блока формирования результата соединены с прямыми выходами суммы сумматора, управляющий вход сумматора подключен к управляющим входам блоков подготовки данных, формирования результата, блок подготовки данных содержит первый и второй элементы 2-21/1-ИЛИ и элемент ИЛИ в каждом q-м разряде, где q 1,4, первый, второй ретий и четвертый входы j-ro разряда (j 0,4) блока подготовки данных соединены соответственно с J-м разрядом первого операнда сумматора, j-м разрядом второго операнда сумматора, (J + 5}-м разрядом первого и второго операндов, которые связаны с соответствующими входа- ми элемента ИЛИ блока подготовки данных, выходы первого и второго элементов 2-2И- ИЛИ блока подготовки операндов являются соответственно вторым и третьим выходами блока подготовки операндов, причем пер- вый, второй, третий, четвертыйвходы j-ro разряда блока подготовки данных связаны соответственно с (j -Н)-м, (j + 11)-м, (j + 6)-м, (J +16)-м входами блока, блок формирования результата содержит десять разрядов, каж- дый из которых содержит элемент И-ИЛИ, причем входы элементов И-ИЛИ восьмого и девятого разрядов блока формирования результата подключены к первому входу блока формирования результата, входы элементов первого, третьего, четвертого, пятого, шестого разрядов блока формирования результата подключены к второму входу блока формирования результата, блок переноса содержит элемент ИЛИ и элементы И-ИЛИ, отличающийся тем, что, с целью расширения функциональных возможно стей, он содержит блок выделения квадрантов, 1-е входы первого и второго операндов1 сумматора, где i 0,9 - разрядность операндов, подключены соответственно к (I + 1)-му и (I + 11)-му входам блока выделения квадрантов, разряды второго операнда связаны с входами второй группы блока формирования результата, первый, второй и третий выходы блока выделения квадрантов связаны с двадцать первым, двадцать вторым и двадцать третьим входами блока подготовки данных, первый управляющий вход сумматора, кроме того, подключен к управляющему входу блока выделения квадрантов, а второй управляющий вход сумматора подключен к входам блока подготовки операндов, блока формирования результата и блока выделения квадрантов, четвертый и пятый выходы блока выделения квадрантов связаны с соответствующими входами блока формирования результата, кроме того, входы блока переноса с первого по десятый и с семнадцатого по двадцатый связаны с соответствующими выходами блока подготовки данных, десять выходов блока переноса подключены к входам третьей группы блока формирования результата, вход внешнего переноса сумматора связан с соответствующим входом блока переноса, одиннадцатый выход которого является выходом группового переноса сумматора.

первому управляющему входу сумматора, первый вход блока подготовки данных соединен, кроме того, с вторым входом второго элемента 2-2И-ИЛИ и с соответствующим входом второй группы входов второго мультиплексора, пятый вход блока соединен с третьим входом первой группы входов второго мультиплексора и с четвертым входом третьего элемента 2-2И-ИЛИ, выход которого связан с соответствующим выходом блока подготовки данных, шестой вход блока соединен с вторым входом третьего элемента 2-2И-ИЛИ и с третьим входом второй группы входов второго мультиплексора, первые входы третьего мультиплексора соединены соответственно с вторым, седьмым, четветым, девятым входами блока, вторые входы - с девятым, четвертым, седьмым, вторым входами соответственно, первые входы второго мультиплексора соединены с третьим восьмым,пятым и десятым входами блока, вторые входы - с восьмым, третьим, шестым и первым входами блока соответственно, а выходы подключены к соответствующим выходам блока, первый вход блока соединен с первыми входами элементов И-НЕ шестой группы, с первыми входами первого элемента 4-2И- ИЛИ и второго элемента 2-2И-ИЛИ-НЕ, второй вход блока подготовки данных соединен с первыми входами первого, второго, третьего элементов И-НЕ седьмой группы, а также с третьими входами первого элемента 4-2И-ИЛИ-НЕ и второго элемента 2-2И- ИЛИ-НЕ, с вторым входом третьего элемента И-НЕ третьей группы, третий вход блока связан с первыми входами первого элемента И-НЕ десятой группы и четвертого элементе И-НЕ седьмой группы, третьего элемента 4-2И-ИЛИ-НЕ, а также с пятым входом первого элемента 4-2И-ИЛИ-НЕ, с восьмым входом второго элемента 4-2И- ЙЛИ-НЕ, с вторыми входами четвертого элемента И-НЕ третьей группы и третьего элемента И-НЕ четвертой группы, четвертый вход блока подключен к первому входу второго элемента И-НЕ десятой группы, к вторым входам четвертого и первого элементов И-НЕ четвертой группы и второго элемента И-НЕ пятой группы., а также к седьмому входу первого элемента 4-2И- ИЛИ-НЕ и к третьему входу третьего элемента 4-2И-ИЛИ-НЕ, пятый вход блока соединен с вторыми входами первого, третьего и четвертого элементов И-НЕ пятой группы, второго элемента И-НЕ четвертой группы, а также с первым входом второго элемента 4-2И-ИЛИ-НЕ и пятым входом третьего элемента 4-2И-ИЛИ-НЕ, шестой вход блока связан с первыми входами первого и второго элементов И-НЕ восьмой группы и третьего и четвертого элементов И-НЕ десятой группы, а также с третьим входом второго элемента 4-2 И-И Л И-НЕ и

седьмым входом третьего элемента 4-2И- ИЛИ-НЕ, седьмой вход блока соединен с первыми входами первого элемента И-НЕ девятой группы, второго элемента И-НЕ третьей группы, третьего и четвертого эле0 ментов И-НЕ восьмой группы и четвертого элемента 4-2И-ИЛИ-НЕ, а также с шестым входом второго элемента 4-2И-ИЛИ-НЕ, восьмой вход блока подключен к первым входам первого элемента И-НЕ третьей

5 группы, четвертого элемента И-НЕ второй группы, второго и третьего элементов И-НЕ девятой группы, а также к седьмому входу второго элемента 4-2И-ИЛИ-НЕ и к третьему входу четвертого элемента 4-2И-ИЛИ0 НЕ, девятый вход блока связан с первыми входами первого, второго и третьего элементов И-НЕ второй группы, четвертого элемента И-НЕ девятой группы, первого элемента 2-2И-ИЛИ-НЕ, а также с пятым

5 входом четвертого элемента 4-2И-ИЛИ- НЕ, десятый вход блока соединен с первыми входами элементов И-НЕ первой группы, а также с седьмым входом четвертого элемента 4-2И-ИЛИ-НЕ и с третьим входом пер0 вого элемента 2-2И-ИЛИ-НЕ, одиннадцатый вход блока подключен к четвертому входу первого элемента 2-2И- ИЛИ-НЕ, к второму входу второго элемента 2-2И-ИЛИ-НЕ, двенадцатый вход блока

5 связан с вторыми входами первых элементов первой и шестой групп и первого элемента 2-2И-ИЛИ-НЕ, а также с четвертым входом второго элемента 2-2И-ИЛИ- НЕ, тринадцатый вход блока соединен с

0 вторыми входами первых элементов И-НЕ второй и седьмой групп, вторых элементов И-НЕ первой и шестой групп и третьего элемента 4-2И-ИЛИ-НЕ, четырнадцатый вход блока подключен к вторым входам

5 третьих элементов И-НЕ первой и шестой групп, еторых и четвертых элементов И-НЕ второй и седьмой групп, а также к пятому входу второго элемента 4-2И-ИЛИ-НЕ и четвертому входу третьего элемента 4-2И0 ИЛИ-НЕ, пятнадцатый вход блока связан с вторыми входами четвертых элементов И- НЕ первой и шестой групп, третьих элементов И-НЕ второй седьмой групп и первого и второго элементов И-НЕ третьей и деся5 той групп, а также с четвертым входом второго элемента 4-2И-ИЛИ-НЕ и шестым входом третьего элемента 4-2И-ИЛИ-НЕ. шестнадцатый вход блока соединен с вторым входом второго элемента 4-2И-ИЛИ- НЕ и восьмым входом третьего элемента