(54) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU949789A1 |

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1037420A1 |

| Устройство для умножения частоты следования импульсов | 1982 |

|

SU1040598A1 |

| Умножитель частоты следованияиМпульСОВ | 1979 |

|

SU824418A1 |

| Умножитель частоты следования импульсов | 1976 |

|

SU570064A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU884102A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1038943A1 |

1

Изобретение относится к измерительной и импульсной технике и может найти применение в устройствах, где необходимо умножение частоты следования импульсов.

Известен умножитель частоты следования импульсов, содержащий делитель опорной частоты импульсов, счетчик импульсов, счетчик импульсов опорной частоты, блок управления, запоминаюпшй регистр и блок элементов И fl .

Недостатком данного умножителя является пониженная точность умножения.

Наиболее близким по технической супшости к изобретению является умножитель частоты следования импульсов, содержащий генератор опорной частоты, выход которюго соединен с первым входом первого делителя частоты и первым входом блока управления (вхо/Шого фор(нирователя), второй вход которого подключен к входной шине, а первый выход к установочному входу счетчика лмпупьСОВ, выходы которого соединены с группой входов первого запоминающего регистра, управляющий вход которого сое-, динен с вторым выходом блока управле1тя,. и cy DvfaTOp, группа выходов которого, соединена с группой входов второго запоминающего регистра, выходы которого соединены с первой группой входов сумматора, а также счетчик импульсов опорной частоты, выходной формирова10тель импульсов и блок переноса Г2} .

Недостаток этого .устройства - н&достаточно высокая точность умножения.

Цель изобретения - повьпиение точности умножения.

15

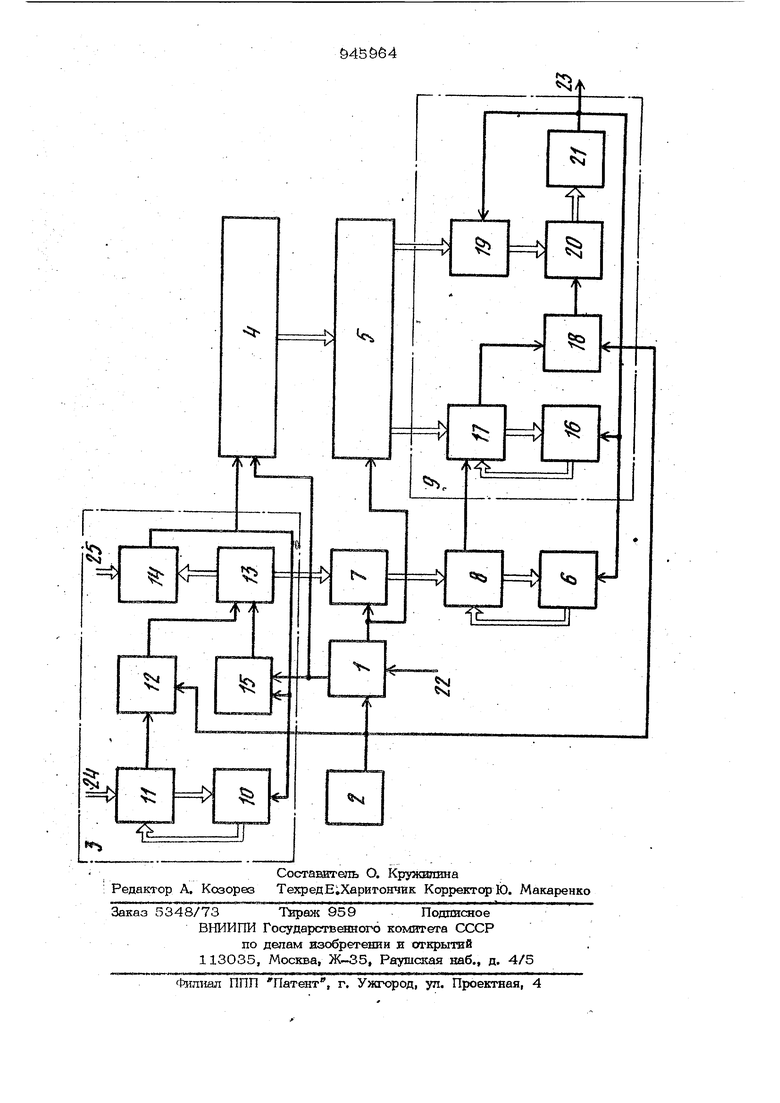

С этой целью в умножитель частоты следования импульсов, содержащий генератор опорной частоты , выход которого соединен с первым входом первого делителя частоты и первьп входом блока управления, втqpoй вход которого подключен к входной шине, а первый выход к установочному входу счетчика импульсов, выхода которого соетхинены с rpjpn.3 . пой входов первого запоминающего регастра, управляющий вход которого соединен с вторым выходом блока управлетгия, и сумматор, группа выходов кото-роге соединена с группой входов второго запоминающего регистра, выходы которого соедщюны с первой группой входов сумматора, введены второй делитель шстоты и третий запоминающий регистр унравляюч.шй вход которого соединен с вторым выходом блока управления, группа входов.- с группой выходов первого делителя частоты, а выходы - с второй грутшой входов сумматора, выход которого соединен с первым входом второго делителя частоты, счетный вход которого соешшен с выходом генератора опорной частоты, первая и вторая группа входов - с первой и второй грухшами выходов первого запоминающего регист ра, а выход - с управляю-тш м входом второго запоминающего регистра, при этом первый выход блока управле1Шя соедш1ен с улравпяюгшхм входом первого делителя частоты, первая группа входов которого соединена с тинами ввода кода дробной части коэффициента деления, вторая группа входов с щинами ввода кода целой части коэффициента деления, а выход с счетным входом счетчика импульсов. Причем первый делитель частоты содержит элемент запрета, элемехет сравне Ш1Я, счетчик импульсов, элемент ИЛИ, запоминающий регистр и сумматор, раз рядные выходы которого подключень к грутше входов заломинакяцего репгстра, выходы которого подютючены к первой грутше входов сум атора, вторая группа входов которого является первой группо входов первого делителя частоты, а вы ход подключен к первому входу элемента запрета, второй вход которого является первым входом первого делителя частоты, а выход -соединен с первым входом счетчика импульсов, второй вход которого соединен с выходом элемента ИЛИ, первая группа выходов счетчика и тульс являе1ся группой выходов первого делителя частоты, а вторая группа .выходов соединена с первой группой входов элемента сравнения, вторая группа входов которого является группой входов первого делителя частоты, а выход элемента сравнения соединен с управляю Ш1М входом запоминающего регистра, nepBbnvi входом элемента ИЛИ и являет™ ся выходом первого де штеля частоты И соединен (;о счеттым входом 4 1тмиульсов, при этом второй вход элемента ИЛИ является управляющим входом первого дейителя частоты. На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит блок 1 управле.ния, генератор 2 опорной частоты, первый делитель 3 частоты с дробным перемейяым каэф4шшентом деления, счетчик 4 импульсов, запоминающие регистры б, 6 и 7, сумматор 8 по переменному модулю, второй делитель 9 частоты с дроб1Пз1м переменным коэффициентом деления. Первый делитель - 3 частоты с дробным перемегшым коэффициентом деления состоит из запоминающего penicTpa 10, сумматора 11, элемента 12 запрета, счетчика 13 импульсов, элемента 14 сравнения, элемента ИЛИ 15. Второй делитель 9 частоты с дробным переменным коэфф5щиентом деления состоит из запоминающего регистра 16, сумматора 17, элемента 18 запрета, элемента 19 переноса кода, вычитающего счетчика 20 импульсов и элемента 21 фиксации нуля. Числами 22 и 23 обозначены входная и выходная цшны, 24 и 25 - щины ввода кода дробной и целой частей коэффициента деления делителя 3. Умно китель частоты следования импульсов работает следующим образом. Пусть требуется реализовать умножение частоты на некоторый коэффшшент К, который в системе счисления по осноь ванию d можно представить в виде: ,a..., где п - чибто разрядов К , а m - целое число { m / 0)i Тогда коэффициент делензш деп 1теля 3 устанавливается равным . , - ,i, ,(,-. . Делитель 3 работает следующим об разом. Пусть в начальный момент состояние регистра 1О нулевое. Тогда на выходах сумматора 11 будет число Д К , пред,зтавляющее собой дробную часть коэфг ициента К . Импульсы генератора 2 поступают через элемент 12 на счетный вход счетчика 13 и увеличивают записанное в нем число. Когда состояние счетчика 13 примет значение d , на выходе элемента 14 появится импульс, который осуществляет запись суммы в регистр 10, установку через элемент ИЛИ счетчика 13 и поступает на выход делителя частоты 3. Значение суммы сумматора 11 составит число 2 ЛК, Далее процесс повторяется. Если на каком-лйёо. этапе число 1ЛК. превысят едэпшцу, то на выходе переноса сумматора появляет-я импульс, а румма принимает значение л8 i Л К -1 Импульс переноса поступает на вход элемента запрета 12 и исключает один импульс из последоватетсьности на входе счетчика 13. Таким образом, очередной импульс на выходе элемента 14 появится через импульсов генератора 2. На выходе сумматора 11 будет число дз д К:, . Таким образом, период следования импульсов на выходе делителя 3 прини.fJ 1 л мает значения q/ и (с()- Т . Можно показать, что средняя частота следования выходных импульсов равна , где TO - период следования опорных импульсов, а f Q - частота опорных импульсов.. Счетчик 4 подсчитывает в течение периода Tg}( умножаемой частоты число выходнь1х импульсов делйтеля.З. Результат подсчета - число Р - равен , . 1N Р к, ГкТ где погрешность представления числа. NQ целым числом импульсов; д N - остаток числа импульсов в счетчике 13 к момогту прихода очередного входного импульса, а Рд (Л дробнай часть от выражения в N скобках. По очередному входному импульсу сигналом блока управления 1 число Р записывается в регистр 5, а число д N в регистр 7. Затем счетчики 4 и 13 устанавливаются в нулевое состояние и начинается новый цикл измерения период Тех Число Р определяет коэффициент деления делителя 9 частоты. Если Р в системе счисления по основанию пред сгавляется в виде ...Ъе, то число P/d имеет вид, ,m i4- e-m-i Разряды регистра 5, содержащие числа е-.ГО е подключаются к входам сумматора 17, а остальные - к элеме ату 19. Делитель 9 работает аналогично делителю 3. Импульсы генератора 2 через элемент 18 поступают на вход счетчика 20 и уменьшают записанное в нем число. При достижегаш нулевого состояния элемент 21 выдает импульс, по которому элемент 19 осуществляет запись числа Ч. из регистра 5 в счетчик 2О, а в регистр 16 даписывается сумма из сумматора 17, Этим же импульсом сумма сумматора 8 записывается в R&гистр 6. Если на каком-либо этапе сумма чисел, поданных на входы сумматора 8, превысят число q , то на выходе переноса сумматора появляется сигнал, кото-, рый поступает на вход переноса младшего разряда сумматора 17. Такое включение дополнительных узлов пртводит к тему. . J. «-.г ыигАл.и л. J ъ:м J..XJ j.EUZi,.u Ж. 1 Л.. коэффшше гт деления 9 определяется числом Р Р т NQ р| . 1 ВХ О ца ЦсЗ с. Частота следования импульсов на выходе умножителя равна Р JrL-K BbKp eWX К с| 1 N.(,J.. а максимальная погрешность, определяв- мая вторым слагаемым, составит вепичи , . и, при условии К, 2, она меньше, чем известном устройстве. Таким образом, предлагаемое, устро; тво позвстяет повысить точность умно-жения, Формула изобретення 1. Умнсакитепь частоты следования и п1ульсов, содержащий генератор onqpной частоты, выход которого соединен с первым входом первого делителя частоты и входом блока управления, второй вход которого пойключен к входной ошве, а первый выход - к установочному входу счетчика импульсов, -выходы которого соединены с группотй входов перво1ч эапсвминаклцего регистра, управляющий вход которого соединен с вторым выходом блока управления, и сумматор, группа выходов которого соединена с грутшой входов второго запоминающего pei-истра, выходы которого соединены- с первой группой входов сумматора, о т -п и ч а ю ,щ и и с я тем, что, с целью повьпиения тогшости умножения, в него введены второй делитель частоты и третий запоминающий регистр, управляющий вход которого соединен с вторым выходом блока увравлешш, группа входов с груотой выходов первого делн еяя час тотЫ| а выходы - с второй группой входов сумматора, выход которого соединен с первым входом второго делителя часто ты, счетный вход которого соединен с выходом генератора опорной частоты, первая и вторая группы входов - с первой н второй гр ггшгами выходов первого запоминающего регистра, а выход - с управляющим входом второго запом шаю.щего регистра, при этом первый выход йггока утграв-ления соединенс-утфавляю1Щ1М входом первого дел1ггеяя частоты, первая грук-па входов которого соединена с щинами ввода кода дробной части коэффициента деления, вторая rpyiffla, вХО дов - с вшнами ввода кода целой части коэффигшента деления, а выход - с счеттаям входом счетчика импульсов.

2, Умножитель по п. 1, отличающийся тем, что первый дели теггь частоты содержит элемент запрета, элемент сравнения, счетчик импульсов.

элемент ИЛИ, запоминающий регистр и - сумматор, разрядные выходы которого под1шючены к группе входов запоминающего регистра, выходы которого подкгао5 чены к первой группе входов сумматора эторая группа входов которого является первой грутшой входов первого делителя частоты, а выход подключен к первому .входу элемента запрета, второй вход

10:которого является первым бходом первого делителя частоты, а выход соединен с первым входом счетчика импульсов, второй вход которого соединен с выходо элемента. ИЛИ, первая группа выходов

15 счетчика 1рлпупьсов является группой выходов первого делителя частоты, а вторая группа выходов соединена с первой группой входов элемента сравнения,вторая группа входов которого является

2(f .в горой группой входов первого делителя частоты, а выход элемента сравнения соединен с управляющим входом запоминающего регастра, первым входом элемента ИЛИ, является выходом первого

25 делителя частоты и соединен со счетным входом счетчика импульсов, при этом второй вход эпемейТа ИЛИ является управляющим входом первого делителя частоты.

30Источники информации,

принятые во внимание при экспертизе

Авторы

Даты

1982-07-23—Публикация

1980-12-29—Подача