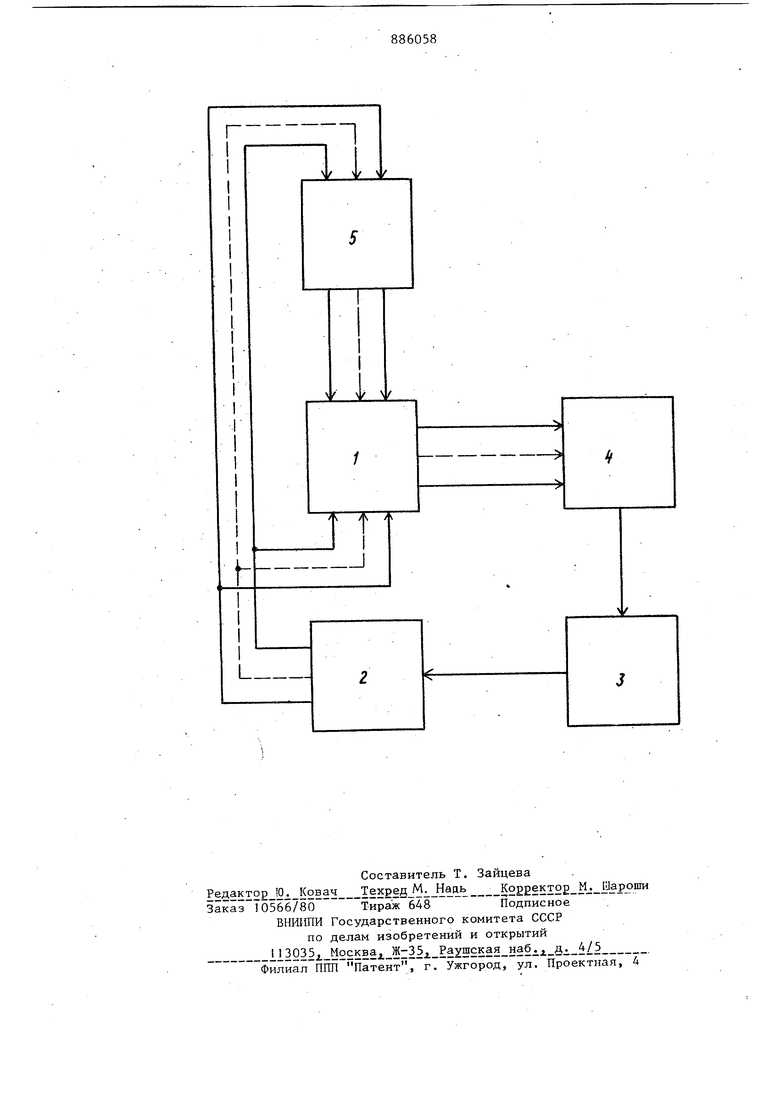

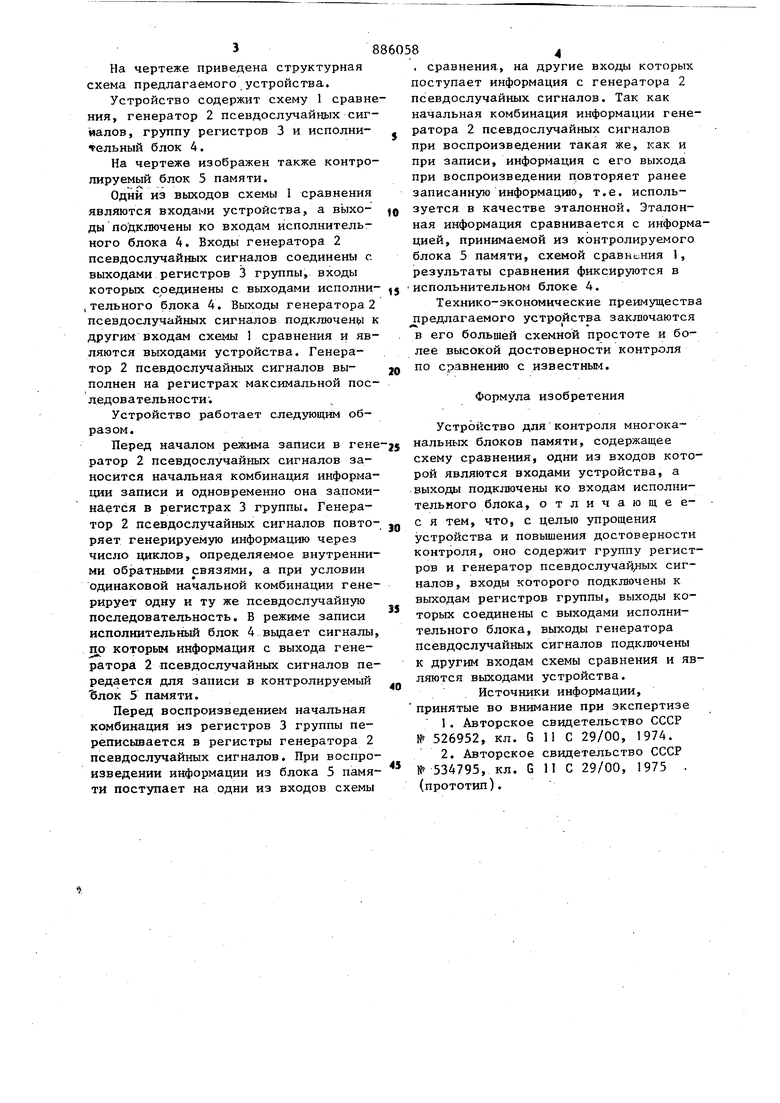

Изобретение относится к запоминающим устройствам. Известно устройство для контроля многоканальных блоков памяти, содержа щее счетчик числа обращений, счетчик математических ожиданий, генератор случайных чисел и сумматор 1 1Недостатком этого устройства является его сложность. Наиболее близким к предлагаемому по технической сущности является устройство для контроля многоканальных блоков памяти, содержащее блок анализа переменной составляющей, блок восстановления, исполнительный блок, и блок сравнения, на первые входы ко торого поступает информация из накопителя, а на вторые входы - информация, прршедщая через блок восстанойле ния 2. Недостатками этого устройства являются низкая достоверность контроля вследствие невозможности проверки накопителя сигналами с точно определенными статистическими параметрами и невозможности анализа ошибок любой кратности, а также схемная сложность блока восстановления и блока анализа переменной составляющей. Цель изобретения - упрощение устройства и повьшение достоверности контроля. Поставленная цель достигается тем, что в устройство для контроля многоканальных блоков памяти, содержащее схему сравнения, одни из входов являются входами устройства, а выходы подключены ко входам исполнительного блока, введены группа регистров и генератор псевдослучайных сигналов, входы которого подключены к выходам регистров группы, входы которых сое- динены с выходами исполнительного блока, выходы генератора псевдослучайных сигналов подключены к другим входам схемы сравнения и являются выходами устройства. На чертеже приведена структурная схема предлагаемого устройства. Устройство содержит схему 1 сравн ния, генератор 2 псевдослучайных сигйалов, группу регистров 3 и исполни1ельный блок 4. На чертеже изображен также контролируемый блок 5 памяти. Одни из выходов схемы 1 сравнения являются входами устройства, а выходы подключены ко входам исполнительного блока 4. Входы генератора 2 псевдослучайных сигналов соединены с выходами регистров 3 группы, входы которых соединены с выходами исполни ,тельного блока 4. Выходы генератора 2 псевдослучайных сигналов подключен к другим входам схемы 1 сравнения и являются выходами устройства. Генератор 2 псевдослучайных сигналов выполнен на регистрах максимальной последовательности;Устройство работает следующим образом. Перед началом режима записи в reHe-jj ратор 2 псевдослучайных сигналов заносится начальная комбинация информации записи и одновременно она запоминается в регистрах 3 группы. Генератор 2 псевдослучайных сигналов повторяет генерируемую информацию через число 1ЩКЛОВ, определяемое внутренними обратными связями, а при условии одинаковой начальной комбинации генерирует одну и ту же псевдослучайную последовательность. В режиме записи исполнительный блок 4 вьщает сигналы, по которым информация с выхода генератора 2 псевдослучайных сигналов передается для записи в контролируемый блок 5 памяти. Перед воспроизведением начальная комбинация из регистров 3 группы переписывается в регистры генератора 2 псевдослучайных сигналов. При воспроизведении информации из блока 5 памяти поступает на одни из входов схемы . сравнения, на другие входы которых поступает информация с генератора 2 псевдослучайных сигналов. Так как начальная комбинация информации генератора 2 псевдослучайных сигналов при воспроизведении такая же, как и при записи, информация с его выхода при воспроизведении повторяет ранее записанную информацию, т.е. используется в качестве эталонной. Эталонная информация сравнивается с информацией, принимаемой из контролируемого блока 5 памяти, схемой сравнения 1, результаты сравнения фиксируются в испольнительном блоке 4. Технико-экономические преимущества предлагаемого устройства заключаются в его большей схемной простоте и более высокой достоверности контроля по сравнению с известным. Формула изобретения Устройство дляконтроля многоканальных блоков памяти, содержащее схему сравнения, одни из входов которой являются входами устройства, а выходы подключены ко входам исполнительного блока, отличающеес я тем, что, с целью упрощения устройства и повышения достоверности контроля, оно содержит группу регистров и генератор псевдослуча%€ых сигналов , входы которого подключены к выходам регистров группы, выходы которых соединены с выходами исполнительного блока, выходы генератора псевдослучайных сигналов подключены к другим входам схемы сравнения и являются выходами устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 526952, кл. G 11 С 29/00, 1974. 2.Авторское свидетельство СССР № 534795, кл. G 11 С 29/00, 1975 . (прототип).

f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля многоканальных магнитных накопителей | 1984 |

|

SU1231538A1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Устройство для контроля цифровых блоков памяти | 1985 |

|

SU1256101A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля многоканального аппарата цифровой магнитной записи | 1988 |

|

SU1607011A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1985 |

|

SU1282212A1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

Л

/V

I

1I

V

Авторы

Даты

1981-11-30—Публикация

1980-02-04—Подача