Г77

7

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода Грея в параллельный двоичный код | 1982 |

|

SU1070541A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ В ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ КОД | 2003 |

|

RU2248033C1 |

| Преобразователь кода грея в параллельный двоичный код | 1978 |

|

SU788104A1 |

| Преобразователь перемещения в код | 1990 |

|

SU1783608A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Устройство для преобразования двоичного кода в код грея и обратно | 1974 |

|

SU560222A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Устройство для кодирования изображения | 1990 |

|

SU1839264A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

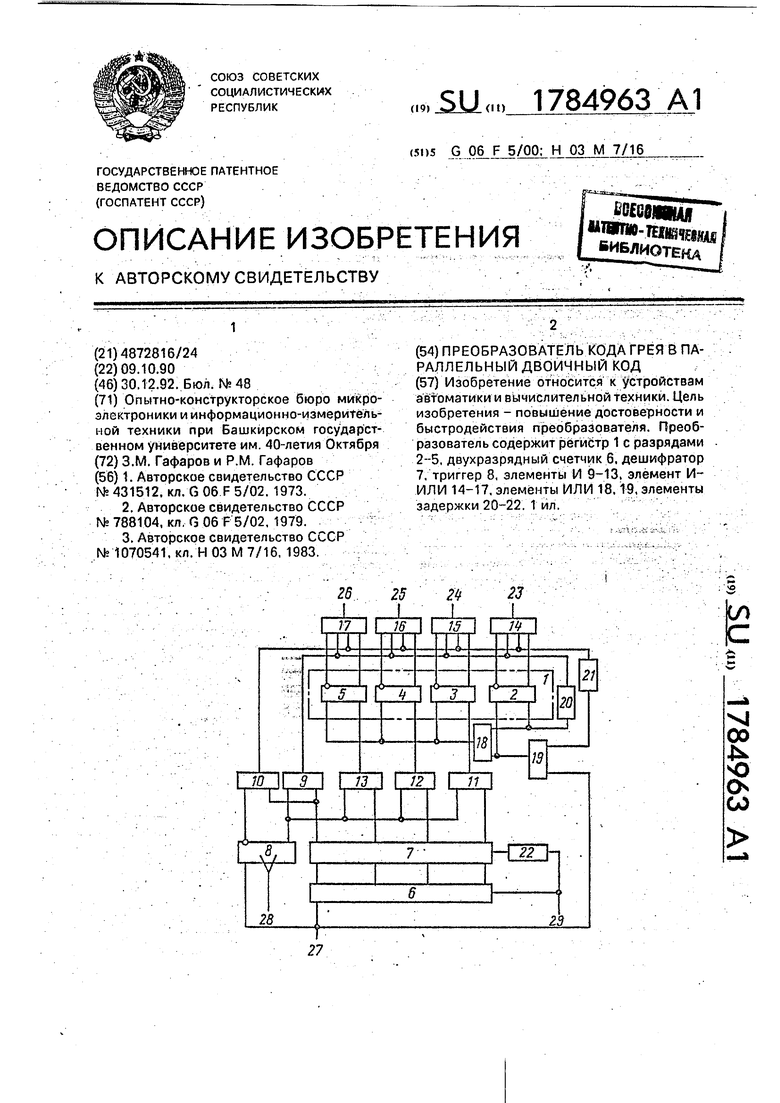

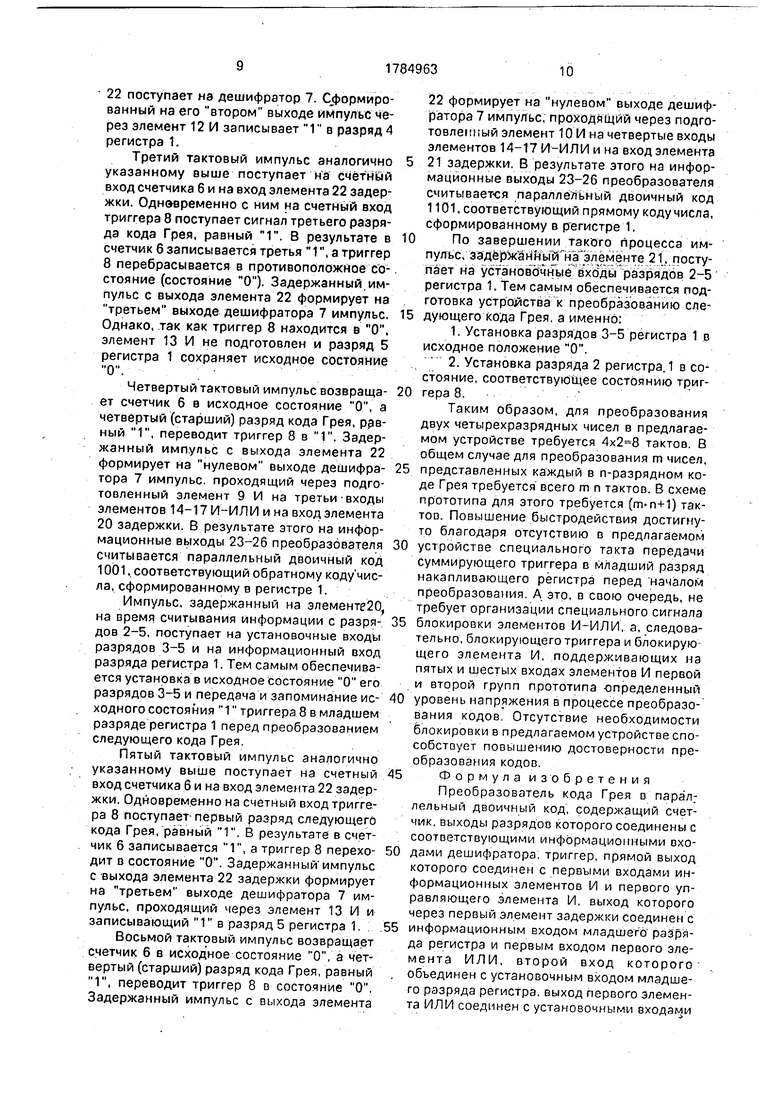

Изобретение относится к устройствам автоматики и вычислительной техники. Цель изобретения - повышение достоверности и быстродействия преобразователя. Преобразователь содержит регистр 1 с разрядами 2-5, двухразрядный счетчик 6. дешифратор 7, триггер 8, элементы И 9-13, элемент И- ИЛИ 14-17. элементы ИЛИ 18,19, элементы задержки 20-22. 1 ил.

28

23

Изобретение относится к устройствам автоматике и вычислительной техники, а бо- лее конкретно - к преобразователям кодов, и может быть использовано, например, в преобразователях перемещение-код по- движных звеньев роботов.

Известен преобразователь кода Грея в параллельный двоичный код 1, содержа- щий регистр, триггер, информационные и управляющие элементы И, элемент задерж- ки и распределитель импульсов. Импульсы кода Грея, поступающего младшими разрядами вперед, подаются на счетный вход триггера, определяющего четность данного кода. При этом в регистр записывается на- чальное состояние триггера, а также состояние триггера, вызванные поступлением на его счетный вход импульсов, определяющих младшие разряды кода Грея. После поступления на счетный вход импульса старшего разряда кода Грея с одного из выходов распределителя подается последний импульс Если в момент его подачи триггер находится в единичном состоянии, то на выходе управляющего элемента И возникает импульс, по- ступающий одновременно на счетные входы всех триггеров регистра, инвертируя их состояния. Если же триггер-находится в О, инвертирование содержимого регистра не происходит

Особенностью работы данного устройства является то, что исходное состояние триггера безразлично, а перед преобразованием происходит (за один такт) установка младшего разряда регистра в то же состоя- ние, что и у триггера.

Недостаток данного устройства заключается в его низком быстродействии. Для преобразования m чисел, каждый из которых представляет в n-разрядном коде Грея, требуется не менее m(n+3) тактов (с учетом такта выдачи информации с регистра).

Известен преобразователь кода Грея в параллельный двоичный код 2, содержащий регистр, триггер, информационные и управляющие элементы И, элемент задержки и распределитель импульсов. Особенностью схемы данного устройства является то, что установочный вход триггера и установочные входы всех разрядов регистра, включая установочный вход его младшего разряда, соединены вместе и подключены к соответствующему выходу распределителя импульсов. В итоге перед преобразованием каждого очередного числа в коде Грея про- изводится установка триггера и всех разрядов регистра, включая его младший разряд, в исходное состояние О.

Недостатком данного устройства является также его низкое быстродействие, Для

преобразования m чисел, каждый из которых представлен в n-разрядном коде Грея, требуется m(n+1)тактов

Наиболее близким изобретением к предлагаемому по технической сущности и схемному решению является преобразователь кода Грея в параллельный двоичный код, описанный в 3. Такой преобразователь,, выбранный в качестве прототипа, содержит счетчик, выходы разрядов которого соединены с соответствующими информационными входами дешифратора, триггер, прямой выход которого соединен с первыми входами информационных элементов И и первого управляющего элемента И, выход которого через первый элемент задержки соединен с информационным входом младшего разряда регистра и первым входом первого элемента ИЛИ, второй вход которого объединен с установочным входом младшего разряда регистра, выход первого элемента ИЛИ соединен с установочными входами всех разрядов регистра, кроме младшего, выходы информационных элементов И соединены с информационными входами соответствующих разрядов регистра, кроме младшего, инверсный выход триггера соединен с первым входом второго управляющего элемента И, выход которого соединен с входом второго элемента задержки, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен со вторым входом первого элемента ИЛИ, прямые и инверсные выходы разрядов регистра подключены к одним из сходов элементов И соответственно первой и второй групп, выходы которых соединены с первыми и вторыми входами соответствующих элементов ИЛИ, выходы которых являются выходами преобразователя, другие входы элементов И первой и второй групп подключены к выходам соответствующих управляющих элементов И, а третьи входы указанных элементов И подключены к выходу блокирующего триггера, установочный вход которого подключен к установочному входу преобразователя, разрешающие элементы И, первые входы которых подключены к соответствующим выходам дешифратора, вторые входы - к выходу третьего элемента ИЛИ. а выходы соединены со вторыми входами соответствующих информационных и управляющих элементов И, и блокирующий элемент И, первый и второй входы и выход которого подключены соответственно к тактовому входу преобразователя, прямому выходу блокирующего триггера и первому входу третьего элемента ИЛИ, второй вход и выход которого соединены соответственно с тактовым входом

преобразователя и входом третьего элемента задержки, выход которого подключен к счетному входу счетчика и информационному входу блокирующего триггера, при этом вход и выход четвертого элемента задержки подключены соответственно к информационному входу преобразователя и счетному входу триггера.

Алгоритм преобразования кодов, реализованный в данном устройстве, требует предварительной установки младшего разряда регистра в то же состояние, что и со- стояние триггера. В процессе такой установки, для предотвращения несанкционированной выдачи кода на выход устройства, осуществляется блокировка элементов И первой и второй групп. А это требует, в свою очередь, постоянной поддержки в процессе преобразования кодов высокого потенциала на пятых и шестых входах этих элементов И. Очевидно, что незначительные сбои в работе блокирующего триггера, блокирующего элемента И и третьего элемента задержки могут приводить к нестабильной работе элементов И первой и второй групп. Это, в конечном счете, снижает устойчивость в работе преобразователя, а следовательно, надежность (достоверность) преобразования кодов.

Цель изобретения - повышение достоверности и быстродействия преобразователя.

Цель достигается преобразователем кода Грея в параллельный двоичный код, содержащий счетчик, выходы разрядов которого соединены с соответствующими информационными входами дешифратора, триггер, прямой выход которого соединен с первыми входами информационных элементов И и первогоуправляющего элемента И, выход которого через первый элемент задержки соединен с информационным входом младшего разряда регистра, выход первого элемента ИЛИ соединен с установочными входами всех разрядов регистра, кроме младшего, выходы информационных элементов И соединены с информационными входами соответствующих разрядов регистра, кроме младшего, инверсный выход триггера соединен с первым входом второго управляющего элемента И, выход которого соединен с входом второго элемента задержки, второй элемент ИЛИ и третий элемент задержки, который отличается от известного тем, что в него введены элементы И-ИЛИ. выходы которых являются выходами преобразователя, прямые и инверсные выходы разрядов регистра соединены соответственно с первыми и вторыми входами соответствующих элементов И-ИЛИ, третьи и

четвертые входы которых подключены к выходам соответственно первого и второго управляющих элементов И, первые выходы дешифратора соединены с вторыми входами соответствующих информационных элементов И, второй выход дешифратора соединен с вторыми входами управляющих элементов И, выход второго элемента за- держки соединен с первым входом второго

0 элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ, выход третьего элемента задержки и счетный вход счетчика объединены и являются тактовым входом преобразователя, второй

5 вход второго элемента ИЛИ и установочные входы триггера и счетчика объединены и являются установочным входом преобразователя.

Основными признаками, отличающими

0 заявляемое устройство от прототипа, являются:

5 входу преобразователя.

А. Введение в схему элементов И-ИЛИ. Наличие указанных признаког в заявляемом устройстве обеспечивает ei о соответствие критерию новизна.

5 Сравнение заявляемого устройства не только с прототипом, но и с другими техническими решениями в данной и смежных областях техники показало, что подключение установочных входов суммирующего

0 триггера и младшего разряда регистра к установочному входу распределителя в устройстве 2 требует дополнительного такта установки перед преобразованием каждого очередного кода Грея, т.е. приводит к сни5 жению скорости преобразования кодов. Аналогичная связь в заявляемом устройстве позволяет избежать этого недостатка и, кроме того, повысить достоверность преобразования.

0

Из вышесказанного следует, что заявляемое техническое решение является новым и обуславливает соответствие его существенных признаков критерию существен5 ные отличия.

Сущность изобретения заключается в. 1. Предварительной установке перед . началом преобразования суммирующего триггера и младшего разряда регистра в одно и то же состояние О.

Наличие этих особенностей позволяет достичь указанного положительного эффекта.

Структурная схема преобразователя кода Грея в параллельный двоичный код. выполненная согласно данному изобретению, приведена на чертеже.

Устройство соде ржит триггер 1 с разрядами 2-5, двухразрядный счетчик б, дешифратор 7, триггер 8, первый 9 и второй 10 управляющие элементы И, информационные элементы 11-13 И. элементы 14-17 И- ИЛИ, первый 18 и второй 19 элементы ИЛИ и первый 20, второй 21 и трет ий 22 элементы задержки.

Первые входы информационных элементов 11-13 И подключены к прямому выходу триггера. 8, а выходы соединены с соответствующими информационными входами старших разрядов 3-5 регистра 1, прямые и инверсные выходы разрядов 2-5 которого подключены соответственно к первым и вторым входам элементов 14-17 И- ИЛИ, выходы которых являются выходами 23-26 преобразователя. Установочный и счетный входы триггера 8 подключены соответственно к установочному 27 и информационному 28 входам преобразователя, а прямой и инверсный выходы триггера 8 соединены с первыми входами соответственно первого 9 и второго 10 управляющих элементов И, выходы которых подключены соответственно к третьим и четвертым входам элементов 14-17 И-ИЛИ. Вход установки О и счетный вход счетчика б подключены соответственно к установочному 27 и тактовому 29 входам преобразователя, а разрядные выходы счетчика 6 соединены с соответствующими информационными входами дешифратора 7, один из входов которого подключен ко вторым входам первого 9 и второго 10 управляющих элементов И, а остальные выходы дешифратора 7 соединены со вторыми входами соответствующих информационных элементов 11-13 И. Первый и второй входы первого элемента 18 ИЛИ подключены соответственно к информационному и установочному входам младшего разряда 2. а выход соеди- н,ен с установочными входами остальных разрядов 3-5 регистра 1. Входы первого 20 и второго 21 элементов задержки подключены к выходам соответственно первого 9 и второго 10 управляющих элементов И, а выходы первого 20 и второго 21 элементов задержки соединены с первыми входами соответственно первого 18 и второго 19 элементов ИЛИ, причем второй вход и выход второго элемента 19 ИЛИ подключены соответственно к установочному входу 27 преоб- разователя и установочному входу

0 младшего разряда 2 регистра 1, а вход и выход третьего элемента 22 задержки соединены соответственно с тактовым входом 29 преобразователя и тактовым входом дешифратору 7.

5 Согласно выполняемым функциям каждый из элементов 14-17 это элемент 2-2И- ИЛИ.

Устройство работает следующим образом

0 Пусть требуется преобразовать коды Грея 1101 и 1011, поступающие на информационный вход 28 преобразователя последовательно младшими разрядами вперед. Перед началом преобразования с внеш5 него по отношению к данному преобразователю устройства (на чертеже не показан) на установочный вход 27 подается импульс установки преобразователя в исходное состояние. По этому импульсу счетчик 6, триггер

0 8, з также разряды 2-5 регистра устанавливаются в состояние О.

В следующий момент времени с внешнего устройства на вход 29 преобразователя подается тактовый импульс. Одновременно

5 с ним на вход 28 преобразователя поступает сигнал первого (младшего) разряда кода Грея, равный в данном случае 1. В результате этого в счетчик 6 записывается 1, а триггер 8 переходит в единичное состояние.

0 Задержанный на время записи информации в счетчик 6 и триггер 8 импульс проходит на выход элемента 22 и поступает на тактовый вход дешифратора 7. В результате этого, так к-ак в счегчике 6 записана 1, формируется

5 импульс на единичном выходе дешифратора 7, проходящий через подготовленный триггером 8 элемент 11 И на информационный вход разряда 3 регистра 1, записывая в него 1.

0 Второй тактовый импульс аналогичным образом поступает через вход 29 преобразователя на счетный вход счетчика б и на вход элемента 22 задержки, Одновременно с ним на вход 28 преобразователя поступает

5 сигнал второго разряда кода Грея. Но так как он равен О, состояние триггера 8 не меняется и он сохраняет свое значение 1. Одновременно импульс на счетном входе счетчика 6 записывает в него вторую 1. Задержанный импульс с выхода элемента

22 поступает на дешифратор 7. Сформированный на его втором выходе импульс через элемент 12 И записывает 1 в разряд 4 регистра 1.

Третий тактовый импульс аналогично указанному выше поступает на счетный вход счетчика 6 и на вход элемента 22 задержки. Одновременно с ним на счетный вход триггера 8 поступает сигнал третьего разряда кода Грея, равный 1. В результате в счетчик 6 записывается третья 1, а триггер 8 перебрасывается в противоположное состояние (состояние О). Задержанный импульс с выхода элемента 22 формирует на третьем выходе дешифратора 7 импульс. Однако, так как триггер 8 находится в О, элемент 13 И не подготовлен и разряд 5 регистра 1 сохраняет исходное состояние О.

Четвертый тактовый импульс возвраща- ет счетчик 6 в исходное состояние О, а четвертый (старший) разряд кода Грея, равный 1, переводит триггер 8 в 1. Задержанный импульс с выхода элемента 22 формирует на нулевом выходе дешифра- тора 7 импульс проходящий через подготовленный элемент 9 И на третьи входы элементов 14-17И-ИЛИ и на вход элемента 20 задержки. В результате этого на информационные выходы 23-26 преобразователя считывается параллельный двоичный код 1001, соответствующий обратному коду чис- ла, сформированному в регистре 1.

Импульс, задержанный на элементе20, на время считывания информации с разря- дов 2-5, поступает на установочные входы разрядов 3-5 и на информационный вход разряда регистра 1. Тем самым обеспечивается установка в исходное состояние О его разрядов 3-5 и передача и запоминание ис- ходного состояния 1 триггера 8 в младшем разряде регистра 1 перед преобразованием следующего кода Грея.

Пятый тактовый импульс аналогично указанному выше поступает на счетный вход счетчика 6 и на вход элемента 22 задержки. Одновременно на счетный вход триггера 8 поступает первый разряд следующего кода Грея, равный 1. В результате в счетчик 6 записывается 1, а триггер 8 перехо- дит в состояние О. Задержанный импульс с выхода элемента 22 задержки формирует на третьем выходе дешифратора 7 импульс, проходящий через элемент 13 И и записывающий 1 в разряд 5 регистра 1.

Восьмой тактовый импульс возвращает счетчик 6 в исходное состояние О, а четвертый (старший) разряд кода Грея, равный 1, переводит триггер 8 в состояние О. Задержанный импульс с выхода элемента

22 формирует на нулевом выходе дешифратора 7 импульс, проходящий через подготовленный элемент 10 И на четвертые входы элементов 14-17 И-ИЛИ и на вход элемента 21 задержки. В результате этого на информационные выходы 23-26 преобразователя считывается параллельный двоичный код 1101, соответствующий прямому коду числа, сформированному в регистре 1.

По завершении такого процесса импульс, задержанный на элементе 21. поступает на установочные входы разрядов 2-5 регистра 1. Тем самым обеспечивается подготовка устройства к преобразованию следующего кода Грея, а именно:

Таким образом, для преобразования двух четырехразрядных чисел в предлагаемом устройстве требуется тактов. В общем случае для преобразования m чисел, представленных каждый в n-разрядном коде Грея требуется всего m n тактов. В схеме прототипа для этого требуется (m-n+1) так- TOD. Повышение быстродействия достигнуто благодаря отсутствию в предлагаемом устройстве специального такта передачи суммирующего триггера в младший разряд накапливающего регистра перед началом преобразования А это, в свою очередь, не требует организации специального сигнала блокировки элементов И-ИЛИ, а, следовательно, блокирующего триггера и блокирую щего элемента И. поддерживающих на пятых и шестых входах элементов И первой и второй групп прототипа -определенный уровень напряжения в процессе преобразования кодов Отсутствие необходимости блокировки в предлагаемом устройстве способствует повышению достоверности преобразования кодов.

Формула изобретения Преобразователь кода Грея в парал; лельный двоичный код, содержащий счетчик, выходы разрядов которого соединены с соответствующими информационными входами дешифратора, триггер, прямой выход которого соединен с первыми входами информационных элементов И и первого управляющего элемента И, выход которого через первый элемент задержки соединен с информационным входом младшего разряда регистра и первым входом первого элемента ИЛИ, второй вход которого объединен с установочным входом младшего разряда регистра, выход первого элемента ИЛИ соединен с установочными входами

всех разрядов регистра, кроме младшего, выходы информационных элементов И соединены с информационными входами соответствующих разрядов регистра, кроме младшего, инверсный выход триггера соединен с первым входом второго управляющего элемента И, выход которого соединен с входом второго элемента задержки, второй элемент ИЛИ и третий элемент задержки, отличающийся тем, что, с целью повышения достоверности и быстродействия преобразователя, в него введены элементы И-ИЛИ, вуходы которых являются выходами преобразователя, прямые и инверсные выходы разрядов регистра соединены соответственно с первыми и вторыми входами соответствующих элементов И-ИЛИ, третьи и четвертые входы которых подключены к выходам соответственно первого и второго управляющих элементов И, первые выходы дешифратора соединены с- вторыми входами соответствующих информационных элементов И, второй выход дешифратора соединен с вторыми входами управляющих элементов И, выход второго элемента задержки соединен с первым входом второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента

ИЛИ, выход третьего элемента задержки соединен с тактовым входом дешифратора, вход третьего элемента задержки и счетный вход счетчика объединены и являются тактовым входом преобразователя, второй вход

второго элемента ИЛИ и установочные-входы триггера и счетчика объединены и являются установочным входом преобразователя, счетный вход триггера является информационным входом преобразователя.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР Ms 431512 | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-30—Публикация

1990-10-09—Подача