(54) УСТРОПСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ

1

Изобретение относится к цифровой вычислительной технике и может быть использовано для проверки исправности цифровых устройств и обнаружения неисправных цифровых узлов и микросхем в них.

Известно устройство контроля-и диагностики/ состоящее из генератора стимулирующих сигналов, конструктивно встроенного в контролируемое уст- . ройство, и сигнатурного анализатора, включаихцего формирователь интервалов измерения и последовательно соединенные регистр сдвига с обратными связями и блок индикации, при этом тактирующий вход и вход установки регистра сдвига с обратными связями соединены с выходами формирователя интервалов измерения, входы запуска, останова и тактирующий вход которого подключены к соответствующим рыходам контролируемого устройства. Сигнатурный анализатор преобразует длинные последовательности двоичных сигналовj существующие на выходах контролируемого устройства, цифрого узла и микросхемы, в короткие ключевые коды, называемые сигнатурами С13.

Недостаток этого устройства низкое быстродействие.

Известно устройство для контроля цифровых узлов, содержащее генера- тор тестов, генератор синхросигналов, логический анализатор, комг тутатор, блок управления глубиной анализа. Это устройство позволяет выбрать глубину анализа, т.е. осуществить

10 проверку на заданное число тактов. Преобразование двоичных последовательностей в сигнатуры осуществляет регистр сдвига с обратньдми связями. Обрабатываемая двоичная последова15тельность суммируется по модулю два с разрядами, поступающими по цепи обратной связи регистра сдвига, который синхронизируется теми же тактирующими сигналами,что и обра20батываемая двоичная последовательность. Входные последовательностимогут быть любой длины, но в конце обработки (в конце интервала измерения) анализируется только код, оста25ющийся в регистре.

Поиск неисправного цифрового узла или неисправной микросхемы в нем осуществляется следующим образом.

На выбранные входы проверяемого

30 устройства от генератора стимулирующих сигналов поступают счютветствующие сигналы, при этом на всех выходах цифровых узлов и микросхем формируют ся вполне определенные последоват тельности двоичных сигналов. В соответствии с алгоритмом поиска неиспра ного цифрового узла в точках, являющихся выходами цифровых узлов, с помощью сигнатурного анализатора изме-г ряют последовательно сигнатуры и сравнивают их с эталрнными значениям сигнатур проверяемых узлов. Если хотя бы одна измеренная сигнатура ,отличается от эталонной, то для поиска неисправной микросхемы в цифровом узле с помощью сигнатурного анализатора аналогично последовательно измеряют сигнатуры на всех выводах предполагаемой неисправной микросхемы и сравнивают их с эталонными значениями сигнатур проверяемых микросхем. Если измеренные на выводах мик росхемы сигнатуры совпадают с эталон ными значениями сигнатур, то принимается решение об исправности микросхемы. Если значения измеренных сигнатур на отдельных выходах микросхемы не совпадают с эталонными их значениями, а значения измеренных сигна тур на входах микросхемы - совпадают, то принимается решение о неиспра ности микросхемы. Если же не совпада ют с эталонными сигнатуры на входах микросхемы, то поиск неисправной микросхемы продолжается на микросхемах с которых поступают сигналы на входы проверенной ранее микросхемы, на которых не совпадали измеренные сигнатуры с эталонными 2. Недостатком известного устройства является малое быстродействие при контроле и поиске неисправности. Действительно, чтобы сделать заключение об исправности цифрового узла или микросхемы, оператору необходимо вручную снять и сравнить с эталонными значениями столько сигнатур, сколько выводов имеет цифрово узел или микросхема. При этом в процессе поиска неисправности цифрового узла или неисправной микросхемы приходится проверять большое количество исправных узлов или микросхем, что связано с большими затратами времени. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем что в устройство для контроля цифровых узлов, содержащее генератор тестов, сигнатурный анализатор, первый элемент И, первый триггер, причем выходы генератора тестов соединены соответственно со входами проверяемого узла, введен мультиплексор, блок управления мультиплексором, бло переключения сигналов синхронизации, второй триггер, второй и третий элементы И, элемент ИЛИ, причем rpyiina выходов сигналов останова проверяемого узла соединена соответств ;нно с группой входов останова, блока переключения сигналов синхронизации, группа тактовых входов которого соединена соответственно с группой тактирующих выходов проверяемого узла, группа выходов сигналов запуска которого соединена соответственно с группой входов запуска блока переключения сигналов синхронизации, группа управляющих входов которого соединена соответственно с группой информационных выходов блока управления мультиплексо ом и соответственно с управляющими входами мультиплексора, первая группа информационных входов которого соединена соответственно с первой группой выходов проверяемого узла, дополнительный тактирующий выход которого соединен с синхровходом генератора тестов, вторая группа выходов проверяемого узла соединена соответственно со второй группой информационных входов мультиплексора, выход которого соединен с информационным входом сигнатурного анализатора, синхровход которого соединен с первым выходом блока переключения сигналов синхронизации, второй выход которого соединен со входом останова сигнатурного анализатора, первый управляющий вход которого соединен с выходом второго элемента И, первый вход которого соединен с третьим выходом блока переключения сигналов синхронизации, первый выход сигнатурного анализатора соединен с управляющим входом блока управления- мультиплексором, установочный вход которого соединен с установочным входом сигнатурного анализатора, с первым входом элемента ИЛИ и является установочным входом устройства, вход шагового режима которого соединен с первым входом третьего элемента И, выход которого соединен со вторым входом элемента ИЛИ, третий вход которого соединен с управляющим выходом блока управления мультиплексором, выход элемента ИЛИ соединен с нулевым входом второго триггера, единичный вход которого соединен с нулевым входом первого триггера и является входом режима ПУСК устройства, второй выход сигнатурного анализатора соединен с единичным входом первого триггера, прямой выход которого соединен со вторым входом третьего элемента И, инверсный выход первого триггера соединен со вторым управляющим входом сигнатурного анализатора, прямой выход второго триггера соединен со вторым входом второго элемента и. Причем блок управления мультиплексором содержит два переключателя, счетчик, узел сравнения, причем управляющий вход блока соединен со счетным входом счетчика, установочный вход которого соединен с установочным входом блока, управляющий выход которого соединен с выходом узла сравнения/ первая группа входов которого соединена соответственно с выходами первого переключателя, вторая группа входов узла сравнения соединена соответственно с выходами счетчика и является группой информационных выходов блока, информационные входы счетчика соединены с выходами второго переключателя.

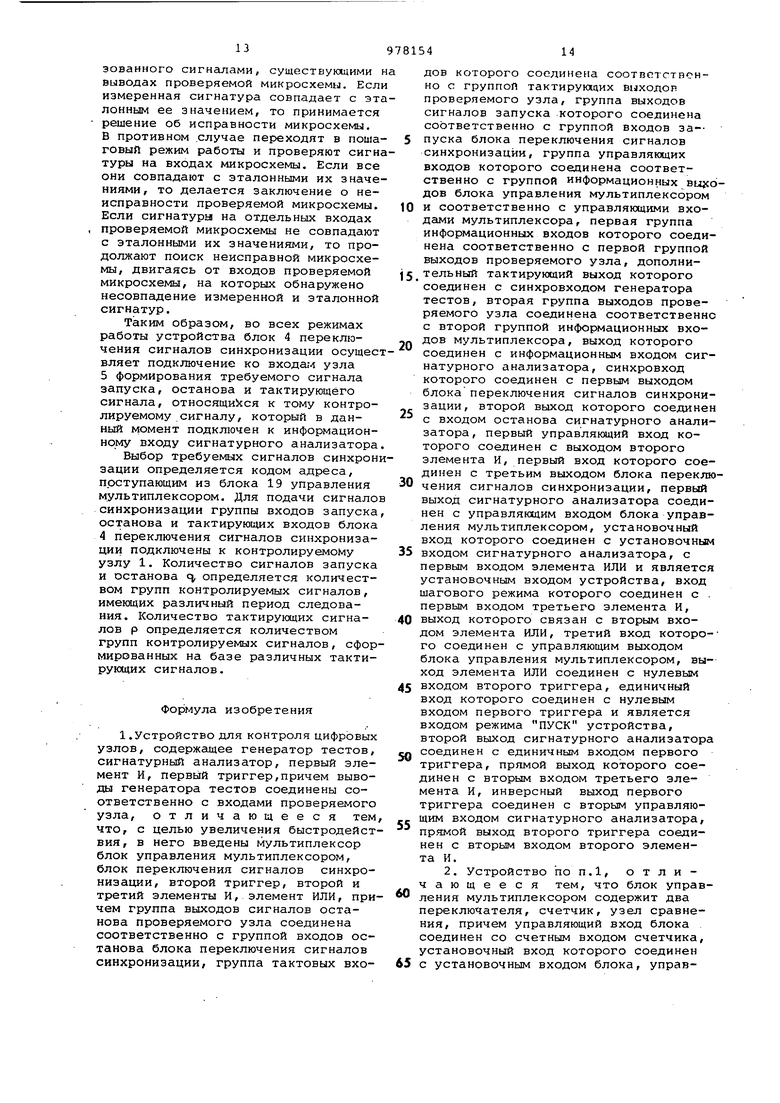

Кроме того, блок переключения сигналов синхронизации содержит три мультиплексора, причем группа тактовых входов блока соединена соответственно с группой информационных входов первого мультиплексора, группа управляющих входов которого соединена соответственно с группой управляющих входов второго и третьего мультиплексоров и является группой управляющих входов блока, группа останова блока соединена соответственно с группой информационных входов второго мультиплексора; выход которого является вторым выходом блока, первый выход которого соединен с выходом первого мультиплексора; группа входов запуска блока соединена соответственно с группой информационных входов третьего мультиплексора, выход которого является третьим выходом блока.

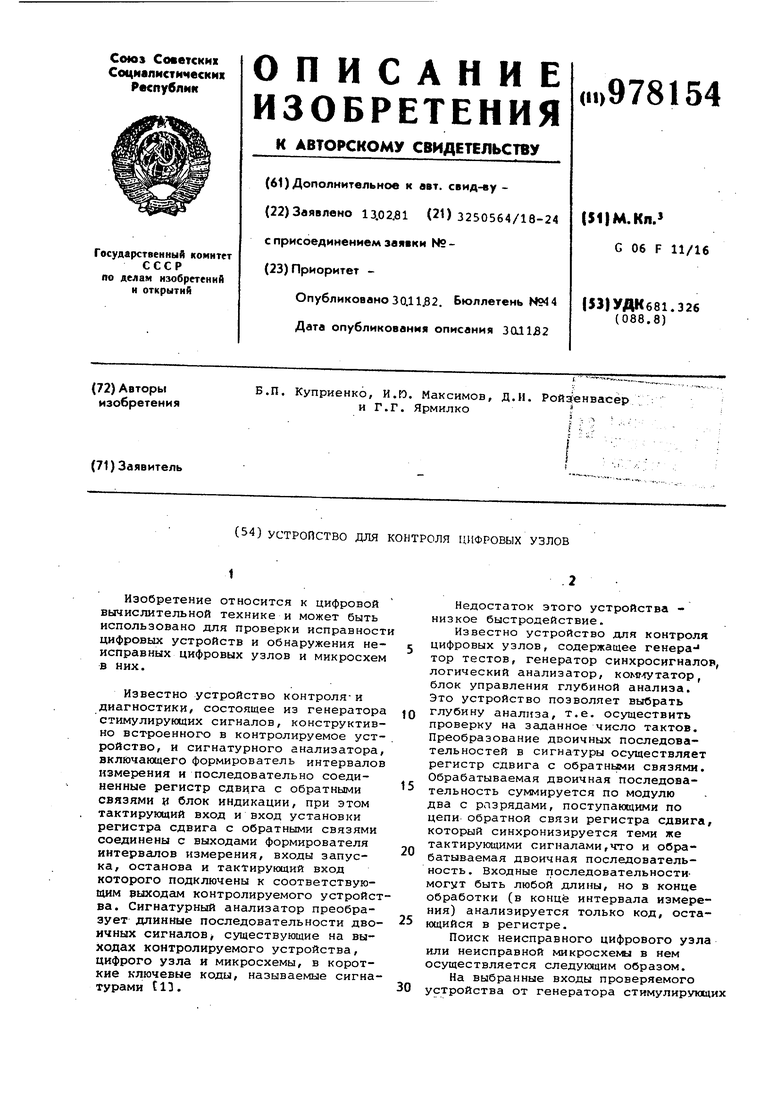

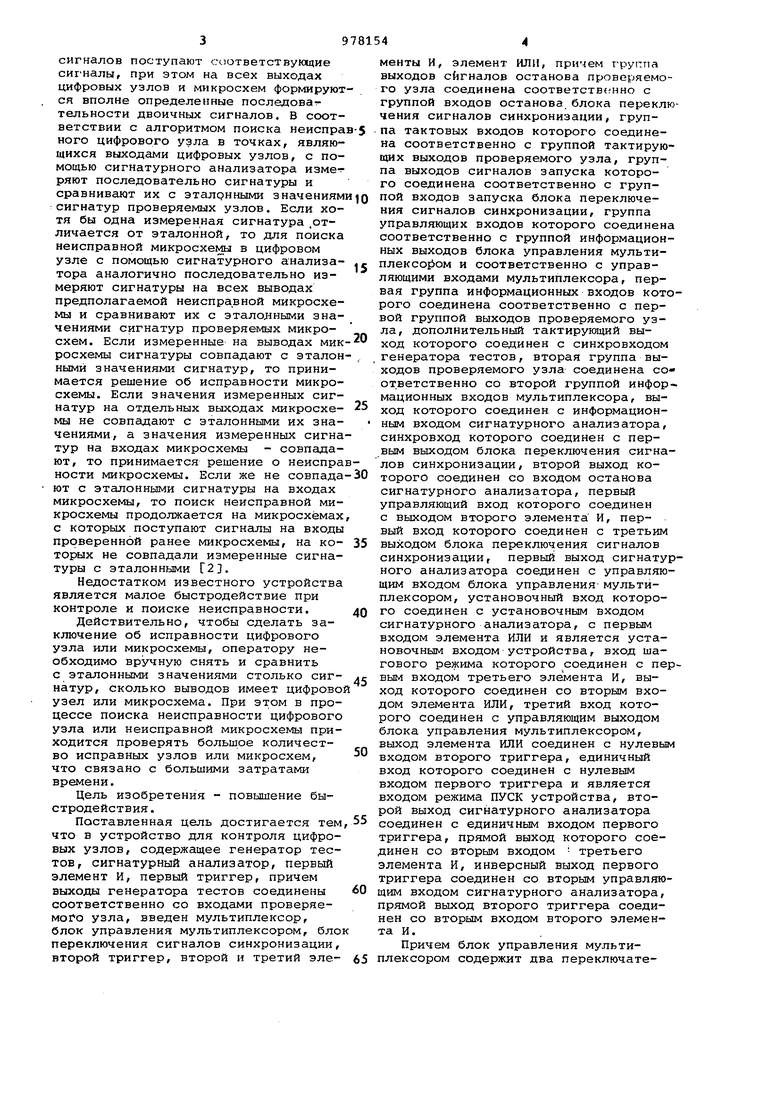

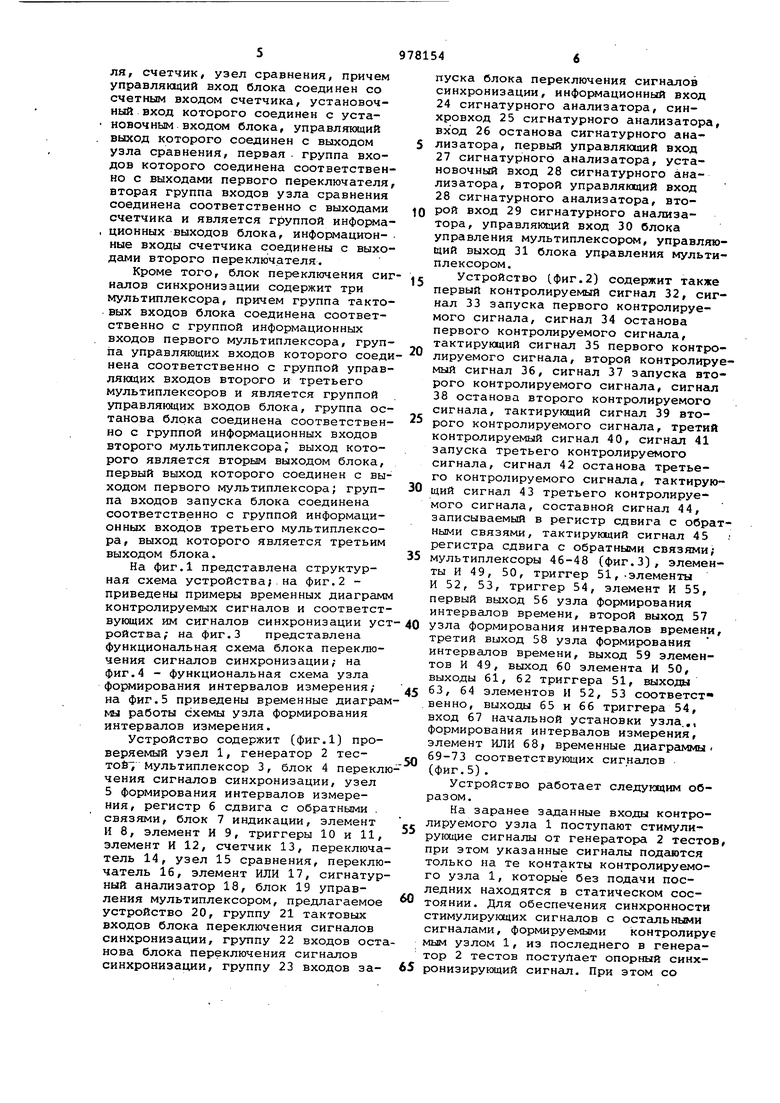

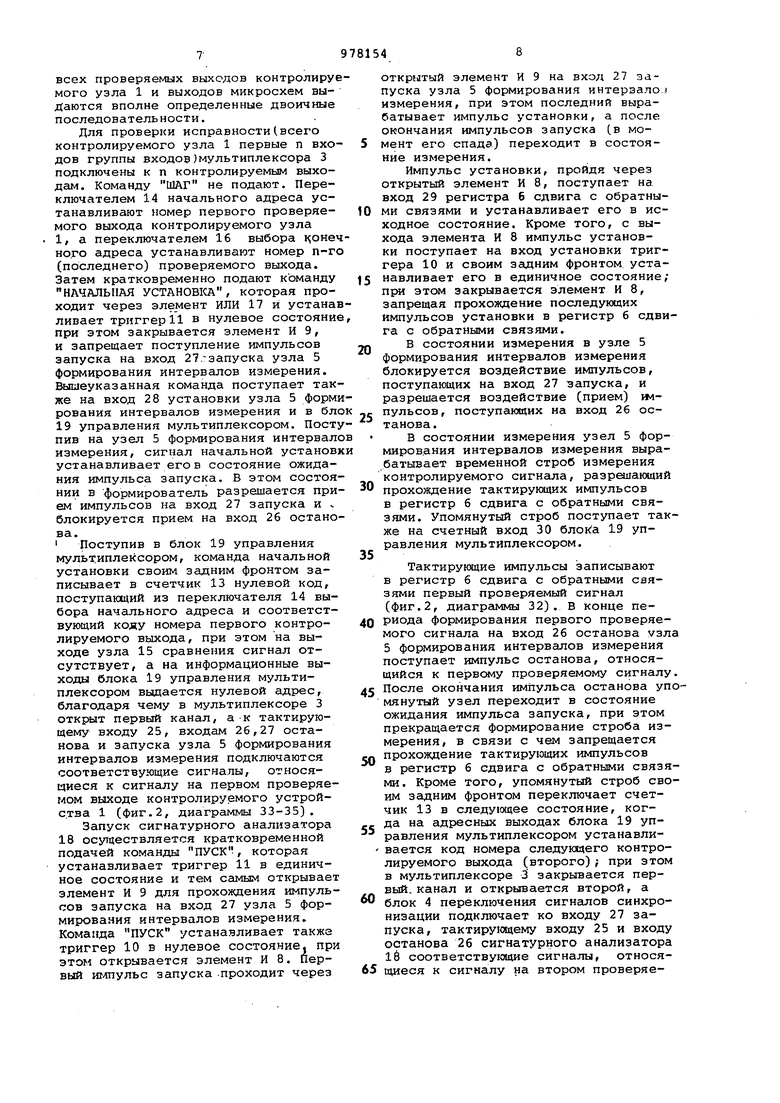

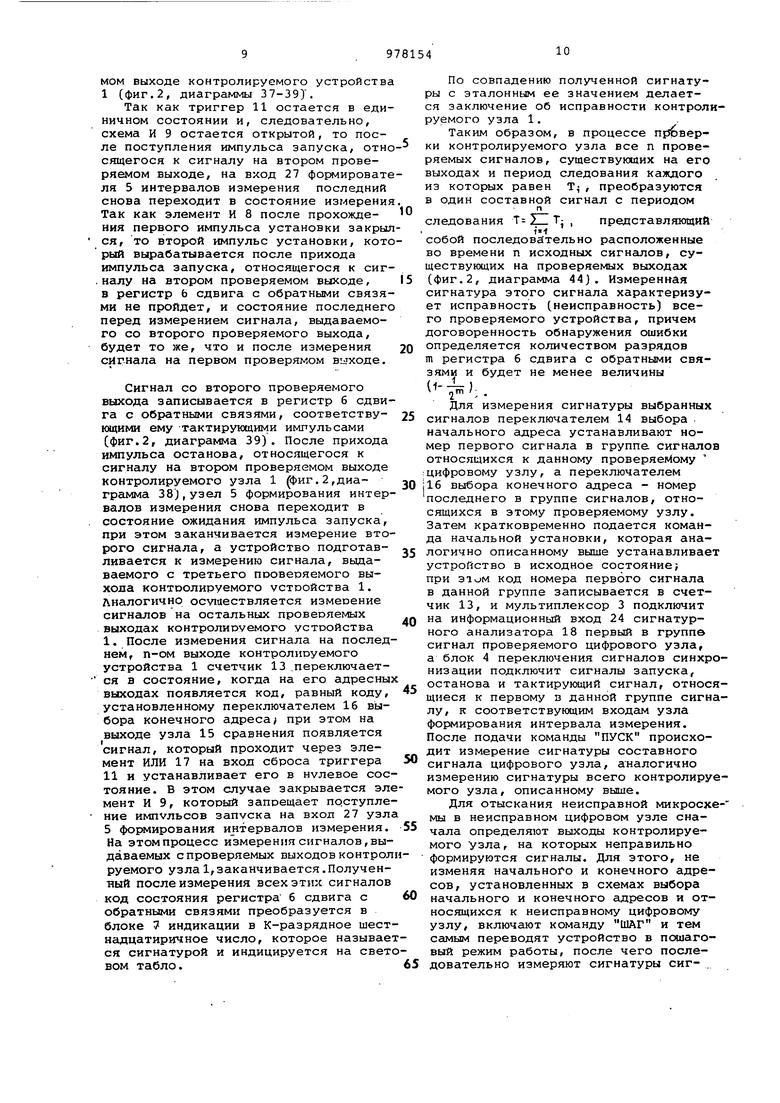

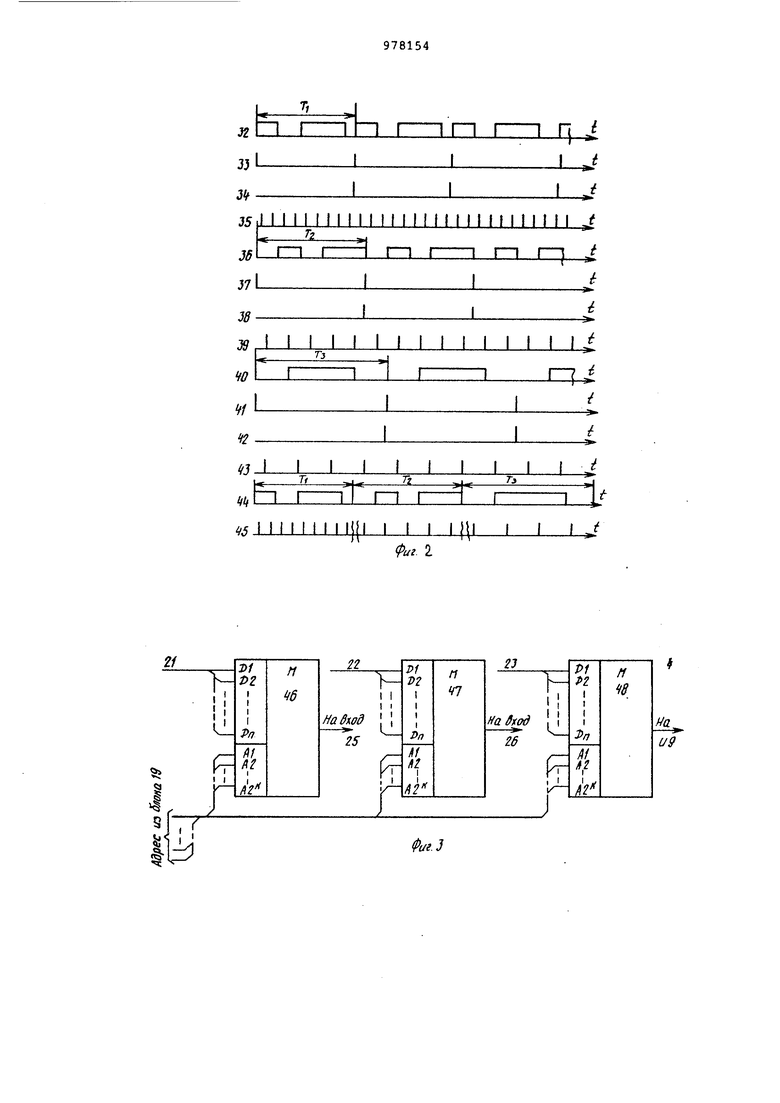

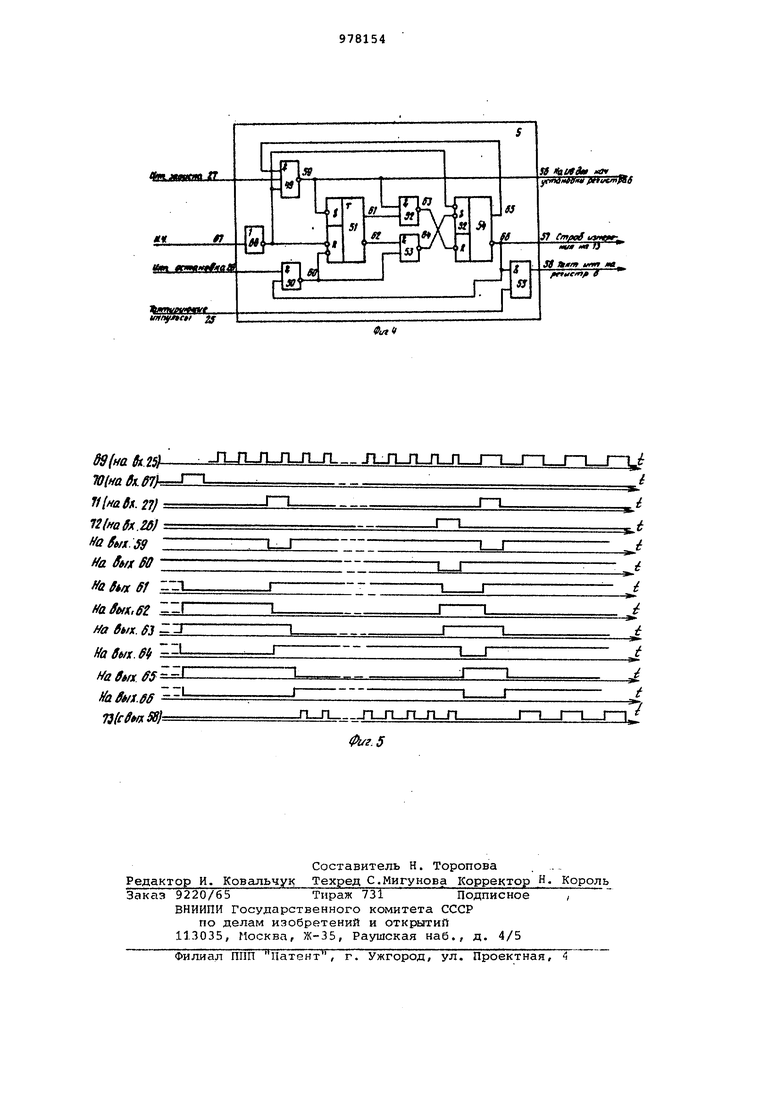

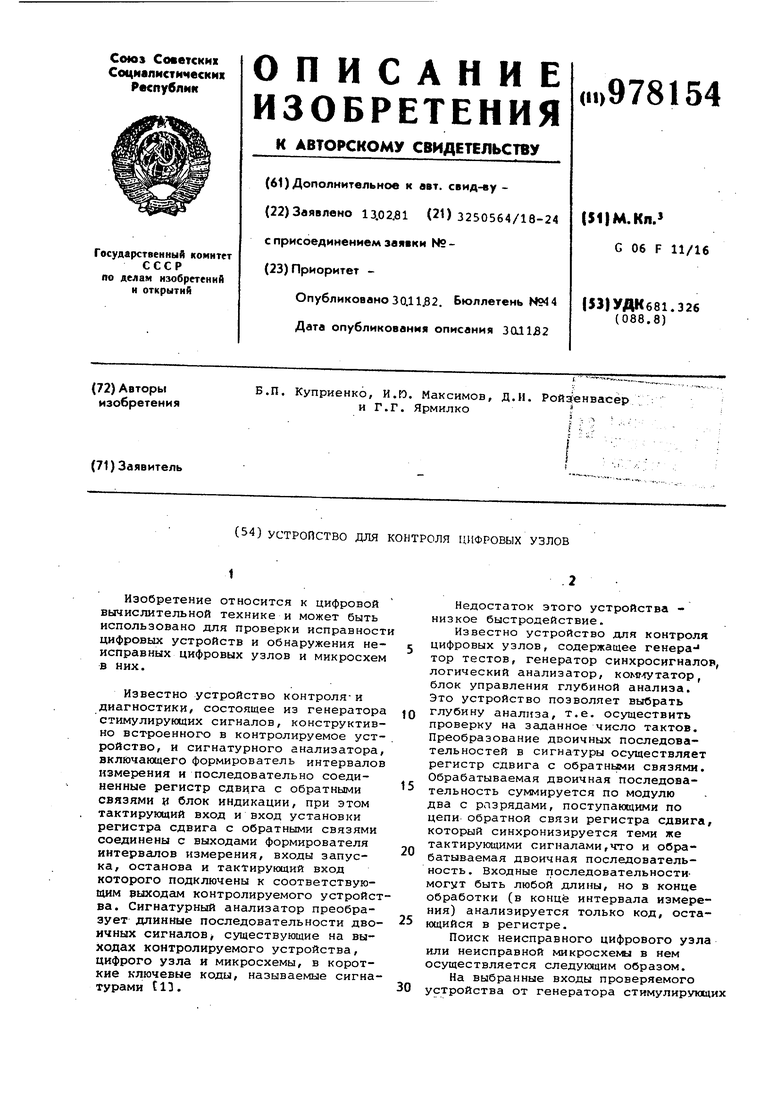

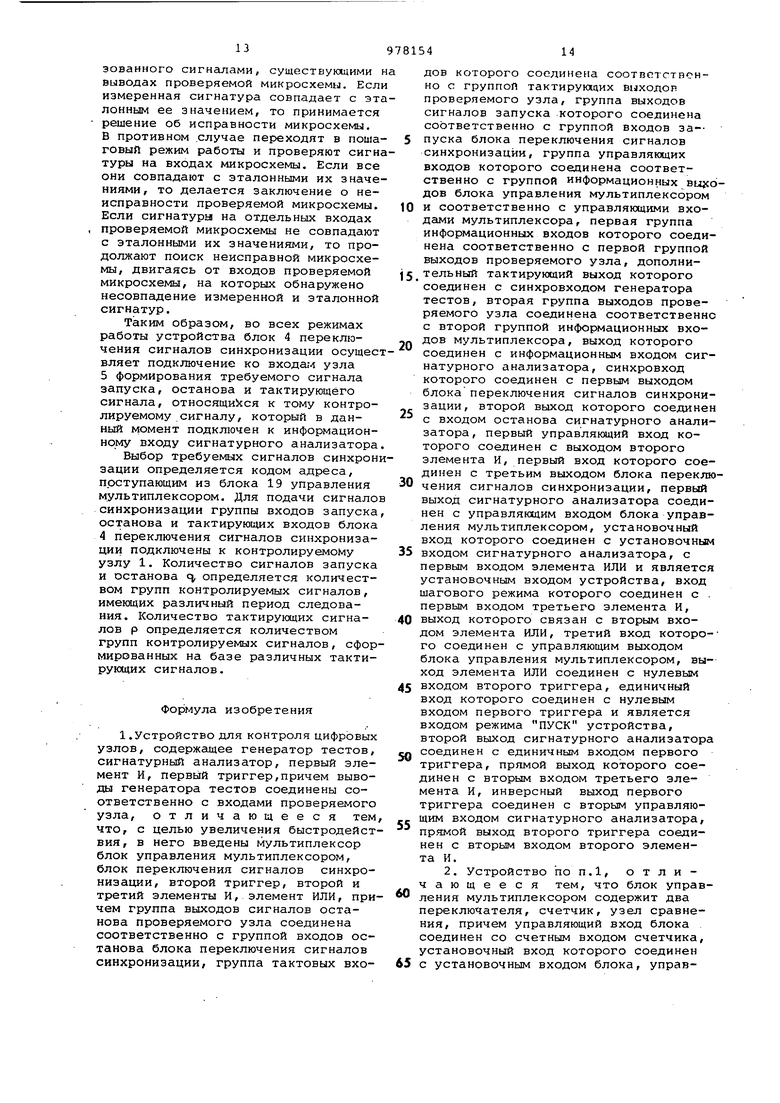

На фиг.1 представлена структурная схема устройства;.на фиг.2 приведены примеры временных диаграмм контролируемых сигналов и соответствующих им сигналов синхронизации устройства; на фиг.З представлена функциональная схема блока переключения сигналов синхронизации,- на фиг.4 - функциональная схема узла формирования интервалов измерения; на фиг.5 приведены временные диаграммы работы схемы узла формирования интервалов измерения.

Устройство содержит (фиг.1) проверяемый узел 1, генератор 2 тестой Мультиплексор 3, блок 4 переклчения сигналов синхронизации, узел 5 формирования интервалов измерения, регистр б сдвига с обратными . связями, блок 7 индикации, элемент И 8, элемент И 9, триггеры 10 и 11, элемент И 12, счетчик 13, переключатель 14, узел 15 сравнения, переключатель 16, элемент ИЛИ 17, сигнатурный анализатор 18, блок 19 управления мультиплексором, предлагаемое устройство 20, группу 21 тактовых входов блока переключения сигналов синхронизации, группу 22 входов остнова блока переключения сигналов синхронизации, группу 23 входов запуска блока переключения сигналов синхронизации, информационный вход 24 сигнатурного анализатора, синхровход 25 сигнатурного анализатора, вход 26 останова сигнатурного анализатора, первый управляющий вход

27сигнатурного анализатора, установочный вход 28 сигнатурного анализатора, второй управляющий вход

28сигнатурного анализатора, второй вход 29 сигнатурного анализа0тора, управляющий вход 30 блока управления мультиплексором, управляющий выход 31 блока управления мультиплексором.

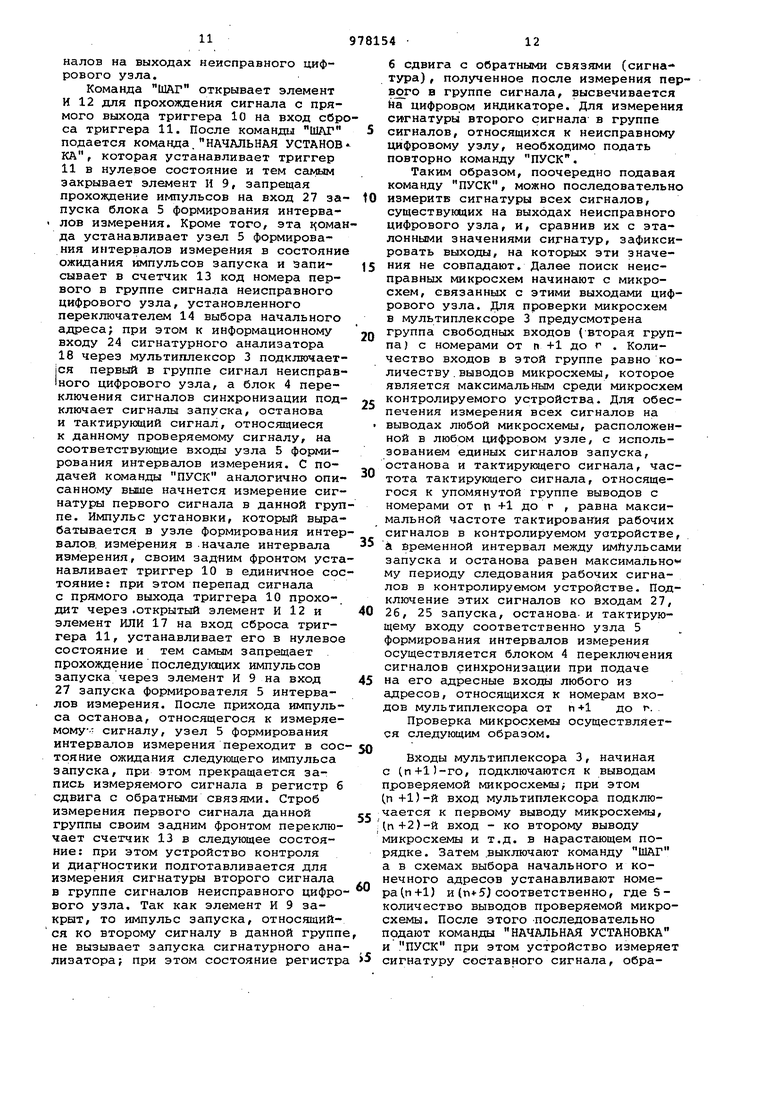

Устройство фиг.2) содержит также

5 первый контролируемый сигнал 32, сигнал 33 запуска первого контролируемого сигнала, сигнал 34 останова первого контролируемого сигнала, тактирующий сигнал 35 первого контро0лируемого сигнала, второй контролируемый сигнал 36, сигнал 37 запуска второго контролируемого сигнала, сигнал 38 останова второго контролируемого сигнала, тактирующий сигнал 39 вто5рого контролируемого сигнала, третий контролируемый сигнал 40, сигнал 41 запуска третьего контролируемого сигнала, сигнал 42 останова третьего контролируемого сигнала, тактирую0щий сигнал 43 третьего контролируемого сигнала, составной сигнал 44, записываемый в регистр сдвига с обратными связями, тактирующий сигнал 45 регистра сдвига с обратными связями;

5 мультиплексоры 46-48 (фиг.З), элементы И 49, 50, триггер 51,-элементы И 52, 53, триггер 54, элемент И 55, первый вЕлход 56 узла формирования интервалов времени, второй выход 57

0 узла формирования интервалов времени, третий выход 58 узла формирования интервалов времени, выход 59 элементов И 49, вьссод 60 элемента И 50, выходы 61, 62 триггера 51, выходы 63, 64 элементов И 52, 53 соответст

5 венно, выходы 65 и 66 триггера 54, вход 67 начальной установки узла.,, формирования интервалов измерения, элемент ИЛИ 68 временные диаграммы69-73 соответствующих сигналов

0 (фиг.5).

Устройство работает следующим образом.

На заранее заданные входы контролируемого узла 1 поступают стимули5рующие сигналы от генератора 2 тестов, при этом указанные сигналы подаются только на те контакты контролируемого узла 1, которые без подачи последних находятся в статическом сос0тоянии. Для обеспечения синхронности стимулирующих сигналов с остальными сигналами, формируемыми контролируе мым узлом 1, из последнего в генератор 2 тестов поступает опорный синх5ронизирующий сигнсш. При этом со

всех проверяемых выходов контролируемого узла 1 и выходов микросхем выдаются вполне определенные двоичные последовательности.

Для проверки исправности(всего контролируемого узла 1 первые п входов группы входов)мультиплексора 3 подключены к п контролируемым выходам. Команду ШАГ не подают. Переключателем 14 начального адреса устанавливают номер первого проверяемого выхода контролируемого узла 1, а переключателем 16 выбора конечного адреса устанавливают номер п-го (последнего) проверяемого выхода. Затем кратковременно подают команду НАЧАЛЬНАЯ УСТАНОВКА, которая проходит через элемент ИЛИ 17 и устанавливает триггер 11 в нулевое состояние при этом закрывается элемент И 9, и запрещает поступление импульсов запуска на вход 27.-запуска узла 5 формирования интервалов измерения. Вышеуказанная команда поступает также на вход 28 установки узла 5 формирования интервалов измерения и в бло 19 управления мультиплексором. Поступив на узел 5 формирования интервало измерения, сигнал начальной установк устанавливает его в состояние ожидания импульса запуска. В этом состоянии в формирователь разрешается прием импульсов на вход 27 запуска и блокируется прием на вход 26 останова.

Поступив в блок 19 управления мультиплексором, команда начальной установки своим задним фронтом записывает в счетчик 13 нулевой код, поступающий из переключателя 14 выбора начального адреса и соответствующий коду номера первого контролируемого выхода, при этом на выходе узла 15 сравнения сигнал отсутствует, а на информационные выходы блока 19 управления мультиплексором выдается нулевой адрес, благодаря чему в мультиплексоре 3 открыт первый канал, а -к тактирующему входу 25, входам 26,27 останова и запуска узла 5 формирования интервалов измерения подключаются соответствующие сигналы, относящиеся к сигналу на первом проверяемом выходе контролируемого устройства 1 (фиг.2, диаграммы 33-35).

Запуск сигнатурного анализатора 18 осуществляется кратковременной подачей команды ПУСК, которая устанавливает триггер 11 в единичное состояние и тем самым открывает элемент И 9 для прохождения импульсов запуска на вход 27 узла 5 формирования интервалов измерения. Команда ПУСК устанавливает такжэ триггер 10 в нулевое состояние,, при этом открывается элемент И 8. Первый шлпульс запуска -проходит через

открытый элемент И 9 на вход 27 запуска узла 5 формирования интерзало; измерения, при этом последний вырабатывает импульс установки, а после окончания импульсов запуска Св момент его спада) переходит в состояние измерения.

Импульс установки, пройдя через открытый элемент И 8, поступает на вход 29 регистра б сдвига с обратными связями и устанавливает его в исходное состояние. Кроме того, с выхода элемента И 8 импульс установки поступает на вход установки триггера 10 и своим задним фронтом устанавливает его в единичное состояние; ПЕ этом закрывается элемент И 8, запрещая прохождение последующих импульсов установки в регистр 6 сдвига с обратными связями.

В состоянии измерения в узле 5 формирования интервалов измерения блокируется воздействие импульсов, поступающих на вход 27 запуска, и разрешается воздействие (прием) импульсов , поступающих на вход 26 останова.

В состоянии измерения узел 5 формирования интервалов измерения вырабатывает временной строб измерения контролируемого сигнала, разролающий прохождение тактирующих импульсов в регистр 6 сдвига с обратными связями. Упомянутый строб поступает также на счетный вход 30 19 управления мультиплексором.

Тактирующие импульсы записывают в регистр 6 сдвига с обратными связями первый проверяемый сигнал (фиг.2, диагрг1Ммы 32). В конце периода формирования первого проверяемого сигнала на вход 26 останова узл 5 формирования интервалов измерения поступает импульс останова, относящийся к первому проверяемому сигналу После окончания импульса останова упмянутый узел переходит в состояние ожидания импульса запуска, при этом прекращается формирование строба измерения, в связи с чем запрещается прохождение тактирующих импульсов в регистр 6 сдвига с обратными связями. Кроме того, упомянутый строб своим задним фронтом переключает счетчик 13 в следующее состояние, когда на адресных выходах блока 19 управления мультиплексором устанавливается код номера следующего контролируемого выхода (второго); при этом в мультиплексоре 3 закрывается первый, канал и открывается второй, а блок 4 переключения сигналов синхронизации подключает ко входу 27 запуска, тактирующему входу 25 и входу останова 26 сигнатурного анализатора 18 соответствующие сигналы, относящиеся к сигналу на втором проверяеMOM выходе контролируемого устройства I(фиг, 2, диаграммы 37-39). Так как триггер 11 остается в единичном состоянии и, следовательно, схема И 9 остается открытой, то после поступления импульса запуска, отно сящегося к сигналу на втором проверяемом выходе, на вход 27 формировате ля 5 интервалов измерения последний снова переходит в состояние измерения Так как элемент И 8 после прохождения первого импульса установки закрыл ся, то второй импульс установки, кото рый вырабатывается после прихода импульса запуска, относящегося к сиг.налу на втором проверяемом выходе, в регистр 6 сдвига с обратными связями не пройдет, и состояние последнего перед измерением сигнала, выдаваемого со второго проверяемого выхода, будет то же, что и после измерения сигнала на первом проверямом виходе. Сигнал со второго проверяемого выхода записывается в регистр 6 сдвига с обратными связями, соответствукмцими ему тактирующими импульсами (фиг.2, диаграмма 39). После прихода импульса останова, относящегося к сигналу на втором проверяемом выходе контролируемого узла 1 (фиг.2,диаграмма 38),узел 5 формирования интервалов измерения снова переходит в состояние ожидания импульса запуска, при этом заканчивается измерение второго сигнала, а устройство подготавливается к измерению сигнала, выдаваемого с третьего проверяемого выхола контролируемого устройства 1. Аналогично осугаествляется измеоение сигналов на остальных проверяемых выходах контролируемого устройства 1. После измерения сигнала на послед нем, п-ом выходе контролируемого устройства 1 счетчик 13 .переключается в состояние, когда на его адресны выходах появляется код, равный коду, установленному переключателем 16 выбора конечного адреса/ при этом на выходе узла 15 сравнения появляется сигнал, который проходит через элемент ИЛИ 17 на вход сброса триггера IIи устанавливает его в нулевое сос тояние. В этом случае закрывается эл мент И 9, КОТОРЫЙ запрещает поступле ние ИМПУЛЬСОВ запуска на вход 27 узл 5 формирования интервалов измерения. На этом процесс измерения сигналов,выдаваемых спроверяемых выходов контрол руемого узла 1, заканчивается.Полученный после измерения всех этих сигналов код состояния регистра 6 сдвига с обратными связями преобразуется в блоке 7 индикации в К-разрядное шест надцатиричное число, которое называе ся сигнатурой и индицируется на свет вом табло. По совпадению полученной сигнатуры с эталонным ее значением делается заключение об исправности контролируемого узла 1. Таким образом, в процессе nfJ Bepки контролируемого узла все п проверяемых сигналов, существующих на его выходах и период следования каждого из которых равен Т, преобразуются в один составной сигнал с периодом следования Т: представляющий собой последовательно расположенные во времени п исходных сигналов, существующих на проверяемых выходс1Х (фиг.2, диаграмма 44). Измеренная сигнатура этого сигнала характеризует исправность (неисправность) всего проверяемого устройства, причем договоренность обнаружения ошибки определяется количеством разрядов m регистра 6 сдвига с обратными связями и будет не менее величины . Для измерения сигнатуры выбранных сигналов переключателем 14 выбора начального адреса устанавливают номер первого сигнала в группе сигналов относящихся к данному проверяемому цифровому узлу, а переключателем 16 выбора конечного ащреса - номер последнего в группе сигналов, относящихся в этому проверяемому узлу. Затем кратковременно подается команда начальной установки, которая аналогично описанному выше устанавливает устройство в исходное состояние; при Э1ом код номера первого сигнала в данной группе записывается в счетчик 13, и мультиплексор 3 подключит на информационный вход 24 сигнатурного анализатора 18 первый в группе сигнал проверяемого цифрового узла, а блок 4 переключения сигналов синхронизации подключит сигналы запуска, останова и тактирующий сигнал, относящиеся к первому в данной группе сигналу, к соответствующим входам узла формирования интервала измерения. После подачи команды ПУСК происходит измерение сигнатуры составного сигнала цифрового узла, аналогично измерению сигнатуры всего контролируемого узла, описанному выше. Для отыскания неисправной микросхемы в неисправном цифровом узле сначала определяют выходы контролируемого узла, на которых неправильно формируются сигналы. Для этого, не изменяя начально1 о и конечного адресов, установленных в схемах выбора начального и конечного адресов и относ5пдихся к неисправному цифровому узлу, включают команду ШАГ и тем самым переводят устройство в пошаговый режим работы, после чего последовательно измеряют сигнатуры сиг- .

налов на выходах неисправного цифрового узла.

Команда ШАГ открывает элемент И 12 для прохождения сигнала с прямого выхода триггера 10 на вход сброса триггера 11. После команды ШАГ подается команда.НАЧАЛЬНАЯ УСТАНОВ КА, которая устанавливает триггер 11 в нулевое состояние и тем самым закрывает элемент Н 9, запрещая прохождение импульсов на вход 27 запуска блока 5 формирования интервалов измерения. Кроме того, эта 1 оманда устанавливает узел 5 формирования интервалов измерения в состояние ожидания импульсов запуска и записывает в счетчик 13 код номера первого в группе сигнала неисправного цифрового узла, установленного переключателем 14 выбора начального адреса; при этом к информационному входу 24 сигнатурного анализатора 18 через мультиплексор 3 подключается первый в группе сигнал неисправного цифрового узла, а блок 4 переключения сигналов синхронизации подключает сигналы запуска, останова и тактирукадий сигнал, относящиеся к данному проверяемому сигналу, на соответствующие входы узла 5 формирования интервалов измерения, С подачей команды ПУСК аналогично описанному выше начнется измерение сигнатуры первого сигнала в данной группе. Импульс установки, который вырабатывается в узле формирования интервалов, измерения в .начале интервгша измерения, своим задним фронтом устанавливает триггер 10 в единичное состояние: при этом перепад сигнала с прямого выхода триггера 10 проходит через .открытый элемент И 12 и элемент ИЛИ 17 на вход сброса триггера 11, устанавливает его в нулевое состояние и тем самым запрещает прохождение последующих импульсов запуска через элемент И 9 на вход 27 запуска формирователя 5 интервалов измерения. После прихода импульса останова, относящегося к измеряемому-- сигналу, узел 5 формирования интервалов измерения переходит в состояние ожидания следующего импульса запуска, при этом прекращается запись измеряемого сигнала в регистр б сдвига с обратными связями. Строб измерения первого сигнала данной группы своим задним фронтом переключает счетчик 13 в следующее состояние: при этом устройство контроля и диагностики подготавливается для измерения сигнатуры второго сигнала в группе сигнсшов неисправного цифрового узла. Так как элемент И 9 закрыт, то импульс запуска, относящийся ко второму сигналу в данной группе не вызывает запуска сигнатурного анализатора; при этом состояние регистра

б сдвига с обратными связями (сигнатура) , полученное после измерения в группе сигнала, высвечивается йа цифровом индикаторе. Для измерения сигнатуры второго сигнала в группе сигналов, относящихся к неисправному цифровому узлу, необходимо подать повторно команду ПУСК.

Таким образом, поочередно подавая команду ПУСК, можно последовательно измеритБ сигнатуры всех сигналов, существующих на выходах неисправного цифрового узла, и, сравнив их с эталонными значениями сигнатур, зафиксировать выходы, на которых эти значения не совпадают. Далее поиск неисправных микросхем начинают с микросхем, связанных с этими выходами цифрового узла. Для проверки микросхем в мультиплексоре 3 предусмотрена группа свободных входов (вторая группа) с номерами от п +1 до г . Количество входов в этой группе равно количеству . выводов микросхемы, которое является максимальным среди микросхем контролируемого устройства. Для обеспечения измерения всех сигналов на выводах любой микросхемы, расположенной в любом цифровом узле, с использованием единых сигналов запуска, останова и тактирующего сигнала, частота тактирующего сигнала, относящегося к упомянутой группе выводов с номерами от п +1 до г , равна максимальной частоте тактирован ия рабочих сигналов в контролируемом устройстве, а временной интервал между имйульсами запуска и останова равен максимальному периоду следования рабочих сигналов в контролируемом устройстве. Подключение этих сигналов ко входам 27, 26, 25 запуска, останова- и тактирующему входу соответственно узла 5 формирования интервалов измерения осуществляется блоком 4 переключения сигналов синхронизации при подаче на его адресные входы любого из адресов, относящихся к номерам входов мультиплексора от п+1 до t.

Проверка микросхемы осуществляется следующим образом.

Входы мультиплексора 3, начиная с (п+1)-го, подключаются к выводам проверяемой микросхемы; при этом (.п+1)-и вход мультиплексора подключается к первому выводу микросхемы, I (п +2)-и вход - ко второму выводу микросхемы и т.д. в нарастающем порядке. Затем .выключают команду ШАГ а в схемах выбора начального и конечного адресов устанавливают номера(.п+1) и () соответственно, где Sколичество выводов проверяемой микросхемы. После этого последовательно подают команды НАЧАЛЬНАЯ УСТАНОВКА и ПУСК при этом устройство измеряет сигнатуру составного сигнала, образованного сигналами, существующими выводах проверяемой микросхемы. Есл измеренная сигнатура совпадает с эт лонным ее значением, то принимается решение об исправности микросхемы. В противном случае переходят в поша говый режим работы и проверяют сигн туры на входах микросхемы. Если все они совпадают с эталонными их значе ниями, то делается заключение о неисправности проверяемой микросхемы. Если сигнатуры на отдельных входах проверяемой микросхемы не совпадают с эталонными их значениями, то продолжают поиск неисправной микросхемы, двигаясь от входов проверяемой микросхемы, на которых обнаружено несовпадение измеренной и эталонной сигнатур. Таким образом, во всех режимах работы устройства блок 4 переключения сигналов синхронизации осущес вляет подключение ко входа; узла 5 формирования требуемого сигнала запуска, останова и тактирующего сигнала, относящиеся к тому контролируемому сигналу, который в данный момент подключен к информационному входу сигнатурного анализатора Выбор требуемых сигналов синхрон зации определяется кодом адреса, поступающим из блока 19 управления мультиплексором. Для подачи сигнало синхронизации группы входов запуска останова и тактирующих входов блока 4 переключения сигналов синхронизации подключены к контролируемому узлу 1. Количество сигналов запуска и останова cj, определяется количеством групп контролируемых сигналов, имеющих различный период следования. Количество тактирующих сигналов р определяется количеством групп контролируемых сигналов, сфор мированных на базе различных тактирующих сигналов. Формула изобретения 1 .Устройство для контроля цифровых узлов, содержаццее генератор тестов, сигнатурный анализатор, первый элемент И, первый триггер,причем выводы генератора тестов соединены соответственно с входами проверяемого узла, отличающееся тем что, с целью увеличения быстродейст вия, в него введены мультиплексор блок управления мультиплексором, блок переключения сигналов синхронизации, второй триггер, второй и третий элементы И, элемент ИЛИ, при чем группа выходов сигналов останова проверяемого узла соединена соответственно с группой входов останова блока переключения сигналов синхронизации, группа тактовых входов которого соединена соотвотстнснно с группой тактирую1дих виходол проверяемого узла, группа выходов сигналов запуска которого соединена соответственно с группой входов за-пуска блока переключения сигналов синхронизации, группа управляющих входов которого соединена соответственно с группой информационных BUJCOдов блока управления мультиплексором и соответственно с управляющими входами мультиплексора, первая группа информационных входов которого соединена соответственно с первой группой выходов проверяемого узла, дополнительный тактирующий выход которого соединен с синхровходом генератора тестов, вторая группа выходов проверяемого узла соединена соответственно с второй группой информационных входов мультиплексора, выход которого соединен с информационным входом сигнатурного анализатора, синхровход которого соединен с первым выходом блокапереключения сигналов синхронизации, второй выход которого соединен с входом останова сигнатурного анализатора , первый управляющий вход которого соединен с выходом второго элемента И, первый вход которого соединен с третьим выходом блока переключения сигналов синхронизации, первый выход сигнатурного анализатора соединен с управляющим входом блока управления мультиплексором, установочный вход которого соединен с установочным входом сигнатурного анализатора, с первым входом элемента ИЛИ и является установочным входом устройства, вход шагового режима которого соединен с . первым входом третьего элемента И, выход которого связан с вторым входом элемента ИЛИ, третий вход которого соединен с управляющим выходом блока управления мультиплексором, выход элемента ИЛИ соединен с нулевым входом второго триггера, единичный вход которого соединен с нулевым входом первого триггера и является входом режима ПУСК устройства, второй выход сигнатурного анализатора соединен с единичным входом первого триггера, прямой выход которого соединен с вторым входом третьего элемента и, инверсный выход первого триггера соединен с вторым управляющим входом сигнатурного анализатора, прялкой выход второго триггера соединен с вторым входом второго элемента И. 2. Устройство по П.1, отличающееся тем, что блок управления мультиплексором содержит два переключателя, счетчик, узел сравнения, причем управляющий вход блока соединен со счетным входом счетчика, установочный вход которого соединен с установочным входом блока, управляющий выход которого соединен с выходом узла сравнения, первая Группа входов которого соединена соответ ственно с выходами первого переключателя, вторая группа входов узла сравнения соединена соответственно с выходами счетчика и является группой информационных выходов блока, инфо1 1ационные входы счетчика соединены соответственно с выходами второ го переключателя. 3. Устройство non.lv отличающееся тем, что блок переключения сигналов синхронизамии содержит три мультиплексора, причем группа тактовых входов блока соедииена соответственно с группой информационных входов первого мультиплексора, группа управляющих входов кото рого соединена соответственно с группой управляющих входов второго и третьего мультиплексоров, и является группой управляющих входов блока, группа входов останова блока соединена соответственно с группой информационных входов второго мультиплексора, выход которого является вторым выходом блока, первый выход кото рого соединен с выходом первого мультиплексора, группа входов запуска блока соединена соответственно с группой информационных входов третьего мультиплексора, выход которого является третьим выходом блока. Источники информации, принятые во внимание при экспертизе 1. Электроника, 5, М. изд. 1977, с.23-33 2. Авторское свидетельство СССР по заявке 2883456, кл. G 06 F.11/16, 1980 (прототип).

Л., I I I I I I I I I I I I I I I ( I t I I М I 1 I { I I

JL

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1264186A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1233156A2 |

± I I I I I I I I I I I I I I J

39 40

f1 42

Ti-.

fe

Itti

1 I I I I I I Ijjl I I I

5

(риг. 1

l/agux.ffS

ЛТ-Л ---П--П-Г1-П-TL 73(cfuxS8}

7

Авторы

Даты

1982-11-30—Публикация

1981-02-13—Подача