2. Устройство по п. 1, отличающееся тем, что блокуправления содфжит элемент И, соединенный первым и вторым входами с одноименными входами блока, первый генератор одиночных импульсов, соединенный выходом с первым входом второго элемента ИЛИ, соединенного соответственно вторим входом и выходом с третьим входом и первым ааходом блока, четвертый вход которого соединен с первым входом третьего эле мента ИЛИ, соединенного вторым входом с исходом элемента И, третьим входом с выходом второго генератора одиночных импульсов, выходом с вторым выходом блока, соединенного третьими выходами с выходами дополнительного счетчика, первый и.второй входы которого соединены с выходами третьего и четвертого генераторов одиночных импульсов .соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1148009A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для тестового диагностирования цифровых блоков | 1987 |

|

SU1622884A1 |

| Устройство для контроля и диагностики многоканальной цифровой аппаратуры | 1986 |

|

SU1348758A1 |

| Устройство для контроля интегральных микросхем | 1978 |

|

SU708269A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

1. УСТРОЙСТВО ДЛИ даАГНОСТИКИ ЦИФРОВЫХ УЗЛОВ, содержащее первыЯ блок.индикации, зонд, соединенный входом с клеммой для подключения вывода диагностируемого ци(й ового узла, блок контроля, соединенный Первыми киходами и перилми входами соответственно с клеммами для подт ключения входов и выходов диагности руемого ци45 ового узла, блок управтения и блок сравнения, о т л и чающееся тем, что, с целью повышения достоверности результатов jдиагностики и быстродействия устройства, в него введены элемент задержки, счетчик, деши 1ратор, мультиплексор, вторые блоки индикации, каждый из блоков индикации содержит переключатели, элементы индикации и первый элемент ИЛИ, причем пед)вый выход блока управления соединен с вторым входом блока контроля и со счетным входом счетчика, соединенного выходами с входами дешифратора, установочным входом с вторым выходом блока управления и с третьим -ходом блока контроля, соединенного вторым выходом с входом блока управления, вторый вход которого соединен с пер,вым клходом блока сравнения, соединенного первым входом с выходом зонда, вторым выходом непосредственно с третьим входом блока управления, а элемент задержки с четвертым входом блока управления, соединенного третьими выходами сjg первыми входами мультиплексора, сое(Л диненного выходом с вторым входом блока сравнения, вторыми входами с выходами соответствующих первых элементов ИЛИ, выходы дешифратора соединены с входами одноименных переключателей каждого из блоков индикации, выходы переключателей соединены с входами соответствующих элементов индикации и с соответствующими входами первого элемента ИЛИ данного блока индикации. со 1 со

Изобретение относится к контрольно-измерительной технике и может быть использовано для диагностики неисправностей цифровых узлов.

Известно устройство для обнаружения неисправностей в логических схемах, содержащее счетчик, выход которого соединены с блоком регистрации, эталонным блоком и контролируе1 мм блоком, соединяелвдм своими выходами с соответствующими входами блока регистрации и блока сравнения, вторые входы которого подключены к выходам эталонного блока,- а выходы к блока индикации и регистрации ij.

Однако устройство имеет ограниченную областьприменения, так как не может быть использовано при диагностике неисправностей цифровых узлов.

Наиболее близким техническим решением к изобретению является устройство для контроля интегральных микросхем, входящих в состав диагностируемого цифрового узла, содержавшее зонд, соединенный входом с клеммой для подключения вывода контролируемой микроcxeivM, блок контроля, соединенный першлми выходами и первыми входами с клеммами для подключения входов и выходов диагностируемого цифрового узла, блок управления и блок сравнения 2.

Недостатками известного устройства являются недостаточная достоверность результатов диагностики и низкое быстродействие. Недостаточная достоверность результатов диагностики обусловлена тем, что при контроле микросхем, находящихся на пути от неправильно функционирующего нлхода цифрового узла до места неисправности используются эталонные микросхеьи, полная гарантия работоспособности которых отсутствует.

Низкое быстродействие определяется необходимостью замены эталонных микросхем при смене типов контролируемых микросхем, находящихся на пути поиска неисправности, а также существенными затратами времени на прием и запись информации по каждому выводу каждой микросхемы на всех словах текста в процессе записи диагностической информации.

Цель изобретения - повышение достоверности результатов диагностики и быстродействия устройсггва.

0..

Поставленная цель достигается

тем, что в устройство для диагностики цифровых узлов, содержание первый ешок индикации, зонд, соединенныи входом с клеммой для подключения вывода диагностируемого цифрового узла, блок контроля, соединенный первыми выходами и первыми входами соответственно с клеммами для подключения входов и выходов диагностируемого

0 цифрового узла, блок управления и блок сравнения, введены элемент задержки, счетчик, дешифратор, мультиплексор и вторые блоки индикации, каждый из блоков индикации содержит переключатели, элементы индикации и первый элемент ИЛИ, причем первый выход блока управления соединен с вторым входом блока контроля и со счетным входом счетчика, соединен0 ного выходами с входами дешифратора, установочным входом с вторым выходом блока управления и с третьим входом блока контроля, соединенного вторым выходом с первым входом блока управ5 ления, второй вход которого соединен с пфвым выходом блока сравнения, соединенного первым входом с выходом зонда, вторым нлходом непосредственно с третьим входом блока управления,

0 Через элемент задержки с четвертым входом блока управления, соединенного третьими выходами с пфвыми входа.1И мультиплексора, соединенного выходом с вторым входом блока срав5 нения, вторыми входами с выходами

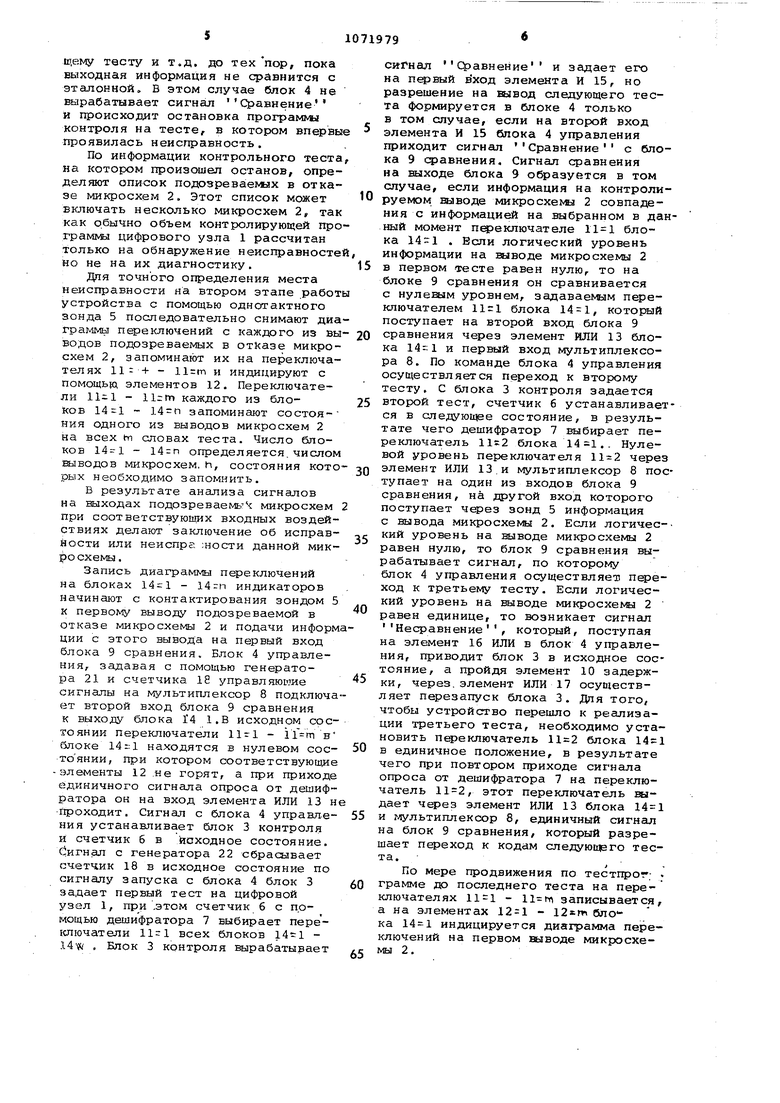

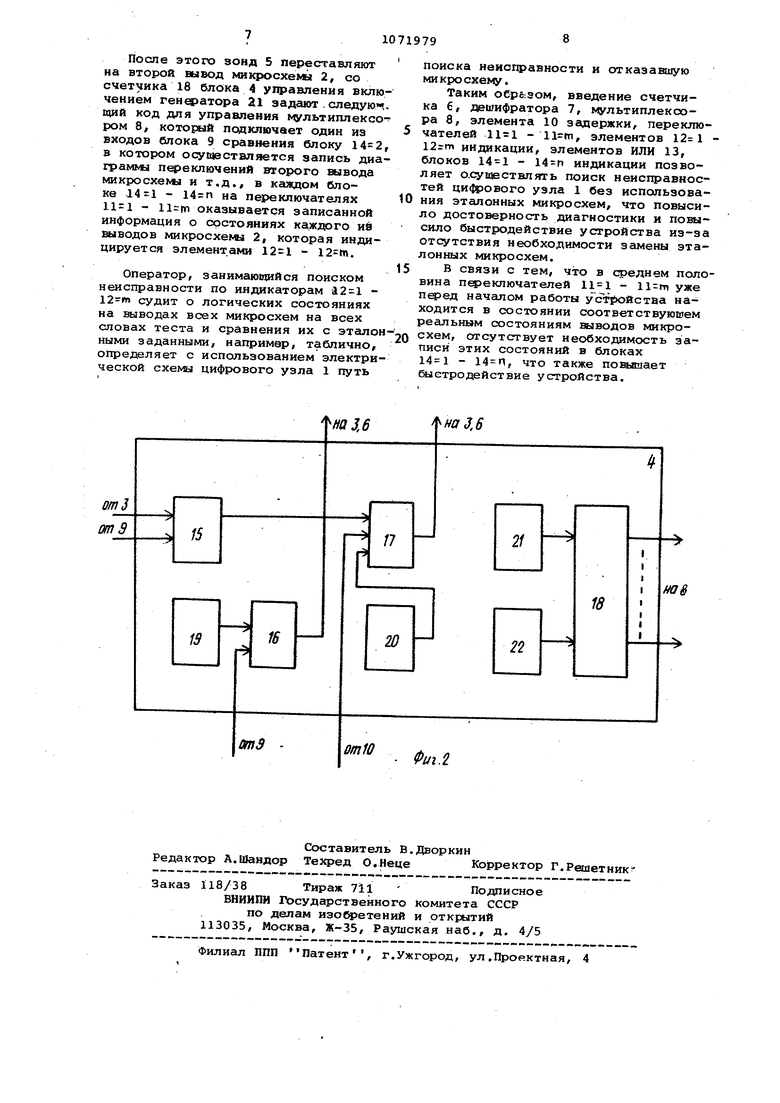

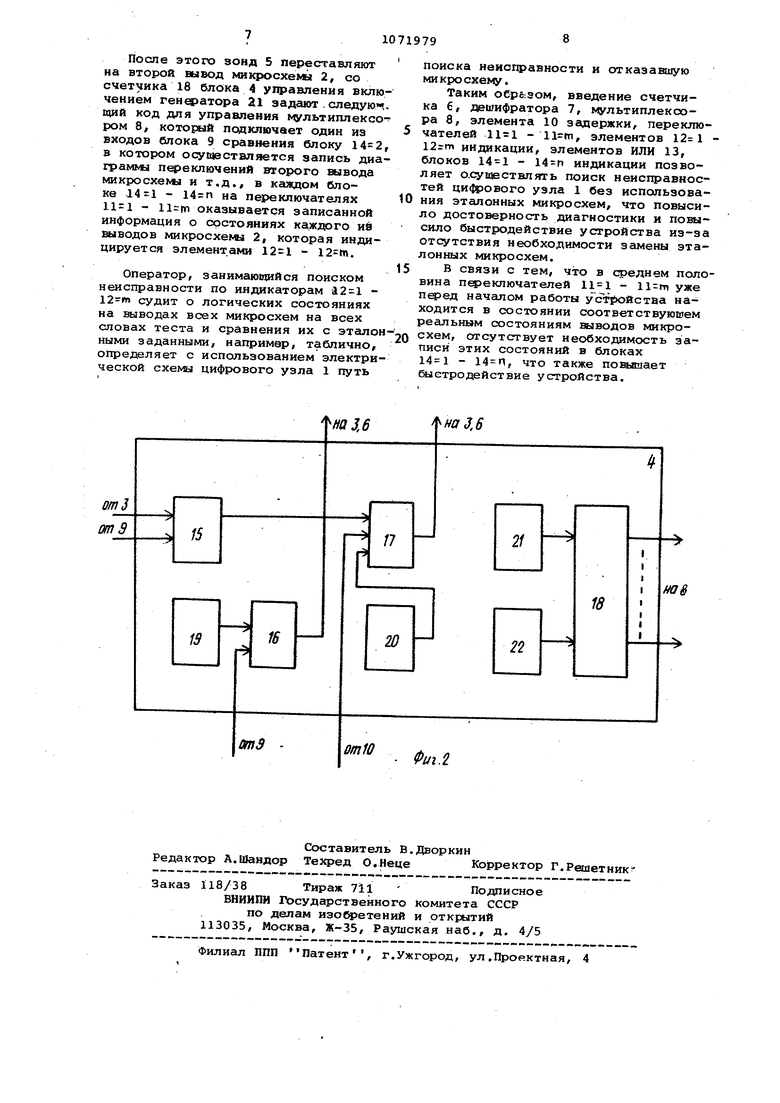

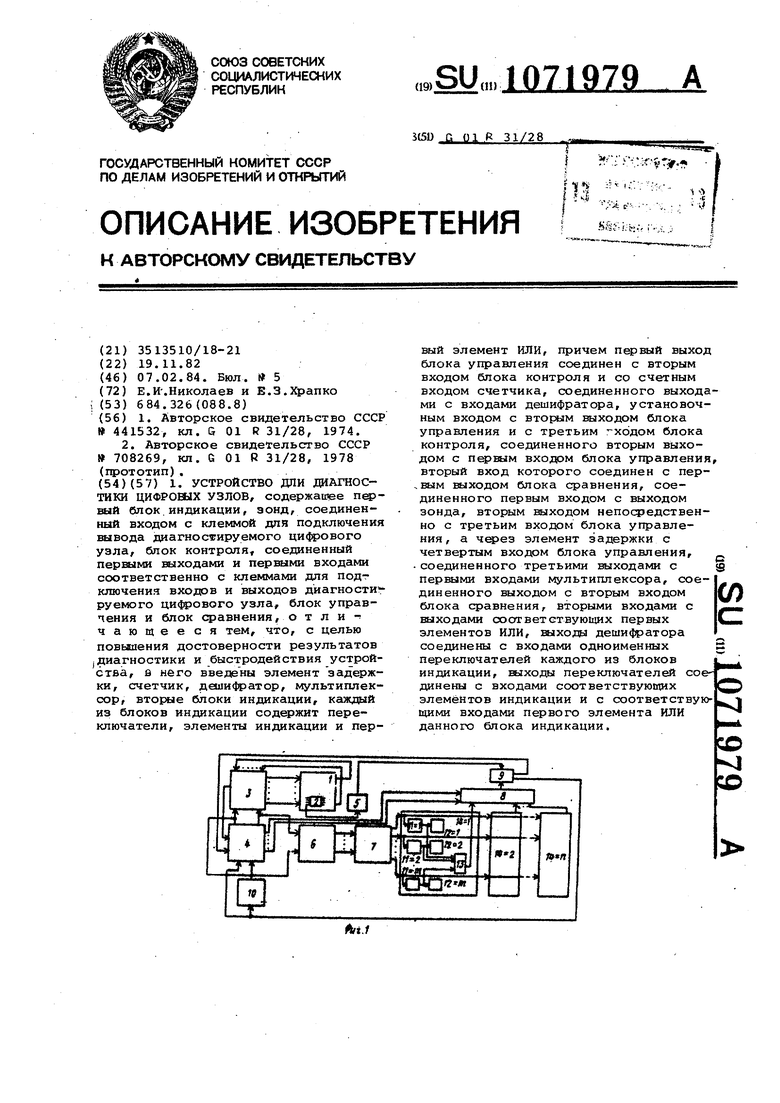

соответствующих первых элементов ИЛИ, выходы дешифратора соединены с входами одноименных переключателей, каждого из блоков индикации, выходы переключателей соединены с входами соответствующих элемен ов индикации и с соответствующими входами первого элемента ИЛИ -данного блока индикации. Кроме того, блок управления содержит элемент И, соединенный перилм и вторым входами с одноименными входами блока, первый генератор оди ночных импульсов, соединенный выходом с первым входом второго элемента ИЛИ, соединенного соответственно вторым входом и выходом с третьим входом и первым выходом блока, четвертый вход которого соединен с пер вым входом третьего элемента ИЛИ, соединенного вторым входом с выходом элемента И, третьим входом с выходом второго генератора одиночных импульсов, выходом с вторым выходом блока, соединенного третьими выходами с выходами дополнительного счетчика-, и второй входы которого соединены с выходами третьего и четвертого генераторов одиночных импульсов соответственно. На фиг. 1 приведена бЛок-схема устройства; на фиг. 2 - функциональ ная схема блока управ,пения. Устройство для диагностики цифрового узла 1, выполненного на микросхемах 2, содержит блок 3 контроля, блок 4 управления, зонд 5, счетчик 6, дешифратор 7, мультиплек сор 8, блок 9 сравнения, элемент задержки 10, и переключатели - , элементы - индикации, элементы ИЛИ 13, образую щие пфвый 14 1 и втсрые - 14 блоки индикахщи. Блок 4 управления содержит элемент 15 И, второй 16 и третий 17 элементы ИЛИ, дополнительный счетчик 18, первый 19, второй 20, третий 21 и четвертый 22 генераторы одиночных импульсов. Выход зонда 5 соединен с клеммой для подключения вывода диагностируе мого цифрового узла 1, блок 3 контроля соединен первыми выходами и пер вымивходами соответственно с клеммами для подключения входов и выходов диагностируемого цифрового узла пфвый выход блока 4 управления сое динен с вторым входом блока 3 контр ля и со счетным входом счетчика б, соединенного выходами с входами дешифратора 7, установочным входЬм с вторым выходом блока 4 управления и с третьим входом блока 3 контроля соединенного вторым выходом с входом блока 4 управления, второй вход которого,соединен с первым ных дом блока 9 сравнения, соединенного первым входом с выходом зонда 5, вто рым выходом непосредственно с третьим входом блока 4 управления, а через элемент 10 задержки - с четвертым входом блока 4 управления, соединенного третьими выходами с первыми входами мультиплексора 8, соеди ненного выходом с вторым входом блока 9 сравнения, вторыми входами - с иаходами соответствующих первых элементов ИЛИ 13, выходы дешифратора 7 соединены с входами одноименных переключателей - каждого из блоков - 14-п индикации, выходы которых соединены, с входами соответствующих элеменгч тов 12г1 - индикации и с соответствующими входами Первого элемента 13 ИЛИ данного 5-того блока индикации 14 1 . В блоке 4 управления первый и второй входы элемента И 15 соединены с одноименными входами блока. Выход первого генератора 19 одиночных импульсов соединен с первым входом второго элемента ИЛИ 16, соединенного соответственно вторым входом и выходом с третьим входом и первым выходом блока 4, четвертый вход которого соединен с первым входом тре тьего элемента ИЛИ 17, соединенного вторым входом с выходом элемента И 15, третьим входом - с выходом второго генератора 20 одиночных импульсов, выходом - с вторым входом блока 4, соединенного третьими выходами с выходами дополнительного счетчика 18, первый и второй входы которого соединены с выходами третьего 21 и четвертого 22 генераторов одиночных импульсов соответственно. Устройство работает следуюьим образом. На первом этапе работы зонд 5 не подключается. При этом, на вход блока 9 с зонда 5 поступает нулевой сигнал, блок 9 всегда илдает сигнал сравнения на элемент И 15 и осуществляется контроль цифрового узла 1 с помощью блока 3 контроля и блока 4. управления. Сигналом с ген атора 19 блока 4 устанавливают блок 3 контроля в исходное состояние, затем сигналом с генератора 20 блока 4 задают первый тест, поступающий на входы контролируемого узла 1. Блок контроля 3 сравнивает информацию с выходов узла 1 с эталонной информацией и в случае равенства вырабатывает сигнал Сравнение , который поступает в блок 4 на элемент И 15 для выработки комаадл на задание второго теста. Реакция контролируемого цифрового узла 1 повторно сравнивается с эталонной и по сигналу Сравнение осуществляется переход к следующему тесту и т.д. до тех пор, пока выходная информация не сравнится с эталонной. В этом случае блок 4 не вырабатывает сигнал Сравнение и происходит остановка программа контроля на тесте, в котором впервые проявилась неисправность.

По информации контрольного теста на котором произошел останов, определяют описок подозреваемых в отказе микросхем 2. Этот список может включать несколько микросхем 2, так как обычно объем контролирующей программа цифрового узла 1 рассчитан только на обнаружение неисправносте но не на их диагностику.

Для точного определения места Неисправности на втором этапе работ устройства с помощью однотактного зонда 5 последовательно снимают диаграммы переключений с каждого из выводов подозреваемых в отказе микросхем 2, запоминают их на переключателях 11- + - и индицируют с помощью элементов 12. Переключатели 11-1 - 11: гп каждого из блоков запоминают состояния одного из выводов микросхем 2 на всех tn словах теста. Число блоков 14-1 - 14-п определяется.числом выводов микросхем, h, состояния которых Необходимо запомнить.

В результате анализа сигналов на выходах подозреваемьЧ микросхем При соответствующих входных воздействиях делают заключение об исправйости или неиспре. :ности данной микросхемы.

Запись диаграммы переключений на блоках 14-1 - 14-п индикаторов начинают с контактирования зондом 5 к первому выводу подозреваемой в отказе микросхемы 2 и подачи информции с этого вывода на первый вход блока 9 сравнения. Блок 4 управлеHHHf задавая с помощью генератора 21 и счетчика 18 управляюиие сигналы на мультиплексор 8 подключает второй вход блока 9 сравнения к выходу блока 14 1.В исходном состоянии переключатели 11-1 - н блоке 14г 1 находятся в нулевом состоянии, при котором соответствующие -элементы 12 .не горят, а при приходе единичного сигнала опроса от дешифратора он на вход элемента ИЛИ 13 н ггроходит. Сигнал с блока 4 управл-ения устанавливает блок 3 контроля и счетчик б в исходное состояние. Йигнал с генератора 22 сбрасывает счетчик 18 в исходное состояние по сигналу запуска с блока 4 блок 3 задает первый тест на цифровой узел 1, при .этом счетчик б с помощью дешифратора 7 выбирает переключатели всех блоков 14-1 14W . Блок 3 контроля вырабатырает

О авнение

сигнал

и задает его

на пфвый вход элемента И 15, но разрешение на вывод следующего теста формируется в блоке 4 только в том случае, если на второй вход элемента И 15 блока 4 управления приходит сигнал Сравнение с блока 9 сравнения. Сигнал сравнения на выходе блока 9 о азуется в том случае, если информация на контролируемом выводе микросхемы 2 совпадения с информацией на выбранном в данный момент пфеключателе блока . Если логический уровень информации на выводе микросхемы 2 в первом тесте равен нулю, то на блоке 9 сравнения он сравнивается с нулевым уровнем, задаваемым переключателем блока , который поступает на второй вход блока 9 сравнбшия через элемент ИЛИ 13 блока 14:: 1 и первый ВХОД мультиплексора 8. По команде блока 4 управления осуществляется переход к второму тесту, С блока 3 контроля задается второй тест, счетчик 6 устанавливается в схледуюпэе состояние, в результате чего дешифратор 7 выбирает переключатель 11 2 блока .. Нулевой уровень переключателя через элемент ИЛИ 13.и мультиплексор 8 поступает на один из входов блока 9 сравнения, на другой вход которого поступает через зонд 5 информация с вывода микросхег ы 2. Если логический уровень на выводе микросхемы 2 равен нулю, то блок 9 сравнения вырабатывает сигнал, по кoтopo y блок 4 управления осуществляем переход к третьему тесту. Если логический уровень на выводе микросхемы 2 равен единице, то возникает сигнал Несравнение, который, поступая на элемент 16 ИЛИ в блок 4 управления, приводит блок 3 в исходное состояние, а пройдя элемент 10 задержки, через, элемент ИЛИ 17 ocyDiecTBляет перезапуск блока 3. Для того, чтобы устройство перешло к реализации третьего теста, необходимо установить Переключатель блока 14г:1 в единичное положение, в результате чего при повтором приходе сигнала опроса от дешифратора 7 на переключатель , этот переключатель выдает через элемент ИЛИ 13 блока и глультиплексор 8, единичный сигнал на блок 9 сравнения, который разрешает переход к кодам следующего теста. . По Мере продвижения по тестпрогграмме до последнего теста на переключателях 11 1 - записывается, а на элементах 12 1 - 12«т блока индицируется диаграмма переключений на первом выводе микросхемы 2.

После этого зонд 5 переставляют на второй вывод михросхекн 2, со счетчика 18 блока 4 управления включением генератора 21 задают . еледую « щий код для управления мультиплексором В, который подключает один из входов блока 9 сравнения блоку , в котором осу(цествляетоя запись диаграммы переключений второго вывода микросхема и т.д., в каждом блоке - на переключателях 11 1 - 11-гп оказывается записанной информация о состояниях каждого ив выводов микросхемы 2, которая индицируется элементами - .

Оператор занимающийся поиском неисправности по индикаторам судит о логических состояниях на выводах всех микросхем на всех словах теста и сравнения их с эталон ными заданными, например, таблично, определяет с использованием электрической схемы цифрового узла 1 путь

fia3.6

поиска неисправности и отказавшую микросхему.

Таким о6р.9ом, введение счетчика 6, дешифратора 7, мультиплексора 8, элемента 10 задержки, переклю5 чателей - , элементов I2rm индикации, элементов ИЛИ 13, блоков - индикации позволяет о.суаествлять поиск неисправностей цифрового узла 1 без испопьзова10 ния эталонных микросхем, что повысило достоверность диагностики и повысило быстродействие устройства из-за отсутствия необходимости замены эталонных микросхем.

5 В связи с тем, что в среднем половина переключателей - уже п)ед началом работы уст йства находится в состоянии соответствующем реальным состояниям выводов микро0 отсутствует необходимость записи этих состояний в блоках - 14 П, что также повьицает алстродействие устройства.

на J,6

ffffjj

отЗ

15

16

13

and

отЮ

Фиг.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обнаружения неисправностей в логических схемах | 1971 |

|

SU441532A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля интегральных микросхем | 1978 |

|

SU708269A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-02-07—Публикация

1982-11-19—Подача