(St) СПОСОБ ДОЛГОВРЕМЕННОГО ИНТЕГРИРОВАНИЯ УНИПОЛЯРНОГО АНАЛОГОВОГО

I

Изобретение относится к аналоговой вычислительной технике и может быть использовано в моделирующих, интегрирующих и других устройствах для выполнения операции долговременного интегрирования входного сигнала, представляющего собой униполярную, т.е. либо положительную, либо отрицательную функцию.

Известен способ долговременного интегрирования аналогового сигнала, основанный на разбиении всего времени интегрирования на последовательные отрезки (шаги), интегрировании входного сигнала на этих отрезках и изменении начальных условий рирования в момент окончания каждого из отрезков путем переключения обкладок конденсатора обратной связи интегрирующего усилителя, который для определения текущего результата интегрирования требует запоминания результатов интегрирования на каждок из отрезков tOСИГНАЛА

К недостаткам этого способа следует отнести его сложность, обусловленную необходимостью выполнения операции запоминания результата интегрирования в течение каждого из временных отрезков, а также наличие нескомпенсированной ошибки интегрирования, вызываемой дрейфом нуля интегрирующего усилителя.

10

Наиболее близок к предлагаемому способ долговременного интегрирования униполярного аналогового сигнала, основанный на поэтапном интегрировании входного сигнала, сравне15нии результата интегрирования на каждом этапе с эталонным сигналом, запоминании числа этапов интегрирова.ния и определении текущего результата интегрирования как суммы произ20ведения числа этапов интегрирования на постоянное значение, и результата интегрирования на последнем этапе 2.

Недостатком этого способа является значительная погрешность интегрирования, обусловленная наличием нескдмпенсированной ошибки интегрирования, вызываемой температурным к временным дрейфом нуля интегрирующего усилителя. Так, например, при интегрировании единичного униполярного входного сигнала 1(t) на интервале времени от О до Т абсолютная погрешность интегрирования равна ЕТ, а относительная погрешность - Е (где Е - приведенная ко входу интегрирующего усилителя величина сигнала дрейфа нуля).

Цель изобретения - уменьшение погрешности интегрирования, вызываемой наличием температурного и временного дрейфа нуля интегрирующего усилителя Поставленная цель достигается тем что в способе долговременного инте)- рирования униполярного аналогового сигнала, основанном на поэтапном интегрировании входного сигнала, сравнении результата интегрирования на каждом этапе с эталонным сигналом, запоминания числа этапов интегрирования и определения текущего результата интегрирования как суммы произведения числа этапов интегрировани на постоянное значение и результата интегрирования на последнем этапе, результат интегрирования на каждом этапе сравнивают с двумя равными по модулю эталонными сигналами противоположной полярности, в момент равенства результата интегрирования и одного из эталонных сигналов инвертируют входной сигнал и продолжают интегрирование полученного сигнала, а при определении текущего результата интегрирования используют модуль результата интегрирования на последнем этапе.

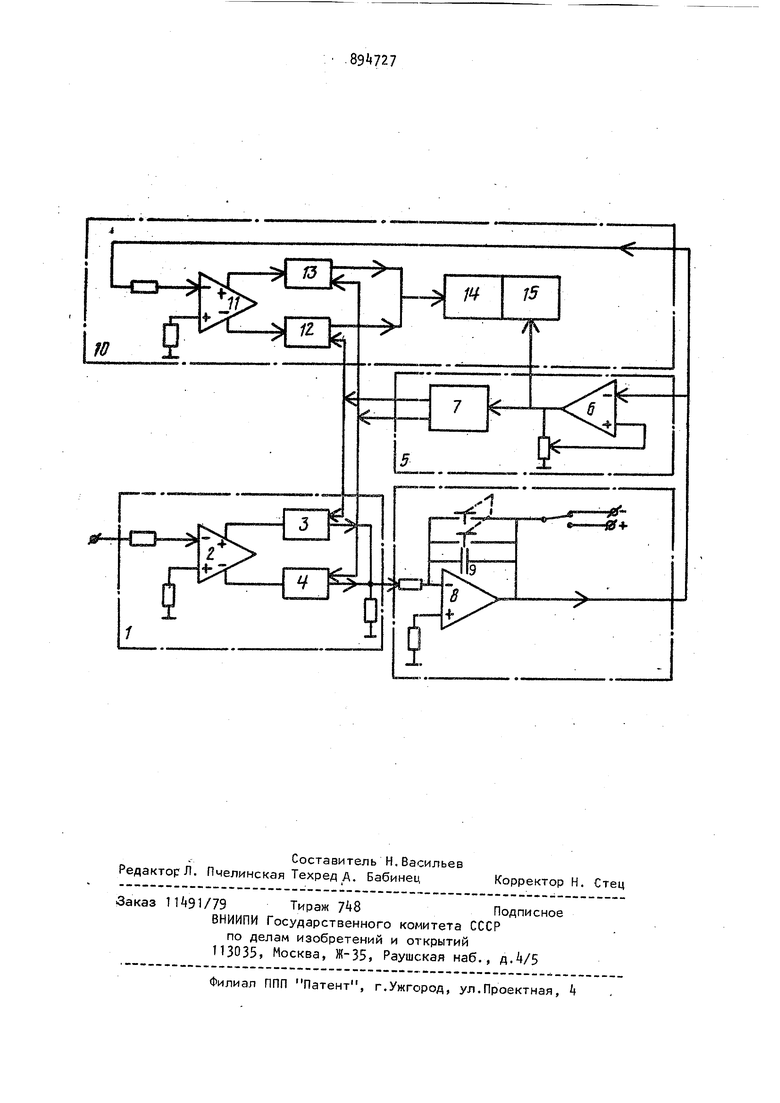

На чертеже представлена блок-схе ма устройства, реализующего способ. Устройство состоит из блока 1 ин1 вертирования входного сигнала, причем этот блок содержит усилитель 2 с двумя фазоинверсными выходами и ключевые элементы 3 и 4, блока 5 управления, включающего компаратор $ триггер 7, интегрирующего усилителя 8 с конденсатором 9 .в цепи отрицательной обратной связи и блока 10 регистрации данных, включающего усилитель 11 с двумя фазоинверсными выходами, ключевые элементы 12 и 13 вольтметр Ik и счетчик 15.

Входной униполярный аналоговый сигнал поступает на инвертирующий вход усилителя 2. Равные по модулю и противоположные по знаку сигналы с

выходов этого усилителя поступают на входы ключевых элементов 3 и k, управляющие входы которых подключены к различным выходам триггера 7. Пусть на первом этапе интегрирования

открыт ключевой элемент 3, сигнал с выхода которого поступает на вход интегрирующего усилителя 8 и вызывает возрастание амплитуды его выходного сигнала. 8 момент равенства

выходного сигнала интегрирующего усилителя 8 и одного из двух равных по модулю эталонных сигналов противоположной полярности срабатывает компаратор 6, подключенный своим выходом к счетному входу триггера 7Сигнал с выхода компаратора 6 вызывает переключение триггера 7 в противоположное состояние, что, в свою очередь, приводит к запиранию ключевого элемента 3 и открытию ключевого элемента 4. Следствием.этого является изменение полярности входного сигнала интегрирующего усилителя 8, т.е. инвертирование входного

сигнала.

С этого момента начинается процесс перезаряда конденсатора 9 в цепи отрицательной обратной связи интегрирующего усилителя 8, в результате чего выходной сигнал этого усилителя сначала уменьшается до нуля, сохраняя при этом ту же полярность, что и на предыдущем этапе, а затем, после изменения полярности, возрастает.по амплитуде. В момент равенства амплитуд второго эталонного сигнала и сигнала на выходе интегрирующего усилителя 8 происходит срабаты еание компаратора 6 и переключение

триггера 7, вызывает повторение процесса перезаряда конденсатора 9 в цепи отрицательной обратной связи интегрирующего усилителя 8.

Количество срабатываний компара-, тора 6 подсчитывается подключенным к его выхрйу счетчиком 15, в котором запоминается число этапов интегрирования.

Выходной сигнал интегрирующего усилителя 8, т.е. результат интегрирования на последнем этапе, измеряет вольтметр 14, причем сигнал на входе этого вольтметра в течение одного цикла интегрирования име ет одну и ту же полярность, что обеспечивается подсоединенным к выходу интегрируюи его усилителя 8 усилителем 11 с двумя фазоинверсным выходами и управляемыми триггером 7 ключевыми элементами 12 и 13Для получения текущего результата интегрирования необходимо просуммировать величину, пропорциональ ную измеренному вольтметром Tt значению выходного сигнала интегрирующего усилителя 8, т.е. результат интегрирования на последнем этапе, и произведение запомненного в счетчике 15 числа этапов интегрирования на постоянную величину, пропорциональную амплитуде эталонных сигналов. Инвертирование входного сигнала интегрирующего усилителя может быtь осуществлено и другим образом. Так например, при использовании в качестве 1 сточника входного униполярного аналогового сигнала резистивного датчика инвертирование входног сигнала интегрирующего усилителя, т.е. выходного сигнала датчика, может быть осуществлено путем измене)НИя полярности напряжения питания датчика. Анализ погрешности интегрировани единичного униполярного входного сиг нала 1(t) на интервале времени от О до Т при использовании предлагаемого способа долговременного интегрирования униполярного аналогового сигнала показывает, что по истечении заданного интервала времени текущий результат интегрирования определяется выражением Ьц A-S Г| Г c. V -2fc-1 -bvi-i ,1 II ис ье/atlj, где А - текущий результат интегрирования;t - момент окончания п-го этап интегрирования; ,2,3,..., а абсолютная погрешность интегрирования А - выражением Д Т Е-Т Е+ТдЕ-.-., где Tt - длительность п-го этапа ин тегрирования, определяемая как . 74 Преобразование последнего выражения с учетом того, что сумма длительностей всех этапов интегрирования равна заданному интервалу времени Т, показывает, что в этом случае абсолютная погрешность интегрирования равна Е Т, а относительная погрешность - Е . Поскольку, приведенная ко входу интегрирующего усилителя величина сигнала дрейфа нуля Е значительно меньше единицы, то сравнение выраже НИИ, определяющих величины абсолютной и относительной погрешностей при использовании предлагаемого способа и уже известного показывает, что предлагаемый способ долговременного интегрирования униполярного аналогового сигнала обеспечивает существенное уменьшение погрешности интегрирования, вызываемой наличием температурного и временного дрейфа нуля интегрирующего усилителя. Формула изобретения Способ долговременного интегрирования униполярного аналогового си1- нала, основанный на поэтапном интегрировании входного сигнала, сравнении результата интегрирования на каждом этапе с эталонным сигналом, запоминании числа этапов интегрирования и определении текущего результата интегрирования как суммы произведения числа .этапов интегрирования на постоянное значение и результата интегрирования на последнем этапе, отличающийся тем, что, с целью уменьшения погрешности, результат интегрирования на каждом этапе сравнивают с двумя равными по модулю эталонными сигналами проти воположной полярности, в момент равенства результата интегрирования и одного из эталонных сигналов инвертируют входной сигнал и продолжают интегрирование полученного сиг нала, а при определении текущего результата интегрирования используют модуль результата интегрирования на последнем этапе. Источники информации, принятые во внимание при экспертизе 1.J.A.McKinney and Ch.A.H.Hali-. jak. The Periodically Reverse-Switched Capacitor. IEEE Transactions on Circuit Theory, 1968, 15, № 3, c.2882.Смолов В.Б.Аналоговые вычислительные -машины. М., Высшая школа, 1972, с.177-182.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГОВЫЙ ИНТЕГРАТОР | 2014 |

|

RU2571618C1 |

| Аналого-дискретное интегрирующее устройство | 1975 |

|

SU556463A1 |

| Аналого-дискретное интегрирующее устройство | 1979 |

|

SU875407A1 |

| Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления | 1987 |

|

SU1494216A1 |

| Интегратор напряжения | 1973 |

|

SU467361A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| Аналого-цифровой преобразователь сопротивления | 1983 |

|

SU1108369A1 |

| Аналоговый интегратор | 1983 |

|

SU1128271A1 |

| УСТРОЙСТВО для ГЕНЕРИРОВАНИЯ ПСЕВДОСЛУЧАЙНЫХСИГНАЛОВ | 1972 |

|

SU328442A1 |

| Интегрирующее устройство | 1985 |

|

SU1251125A1 |

Авторы

Даты

1981-12-30—Публикация

1976-05-20—Подача