(5) ФОРМИРОВАТЕЛЬ МНОГОФАЗНОГО СИГНАЛА

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Программно-управляемый блок задания и развертки поляризующего магнитного поля радиоспектрометра электронного парамагнитного резонанса | 1987 |

|

SU1536285A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛОВ | 2009 |

|

RU2422982C2 |

| СПОСОБ ВОСПРОИЗВЕДЕНИЯ СИГНАЛОВ ЦИФРОВОЙ ИНФОРМАЦИИ С МАГНИТНОГО НОСИТЕЛЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

SU1825194A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для программного управления шаговым двигателем | 1989 |

|

SU1675850A1 |

| Устройство синхронизации источников сейсмических сигналов | 1991 |

|

SU1787278A3 |

1

Изобретение относится к импульсной технике и может быть использова но в управляющих устройствах для управления схемами с жесткими временными требованиями, например в запоминающих устройствах.

Известно устройство для формирования многофазного сигнала, содержащее два сдвигающих регистра, элементы НЕ, элементы И-НЕ 1 .

Недостатки этого устройства - наличие двух синхронизирующих меандров, низкочастотного и высокочастотного, несовпадение фронтов которых вносит погрешность.при формировании выходных сигналов, а также отсутствие возможности программного управления временными характеристиками выходных сигналов.

Наиболее близким по технической сущности к предлагаемому является формирователь многофазного сигнала, содержащий последовательно соединенные счетчик, программный блок (дешиф раторы) и регистр 2.

Недостатки известного устройства отсутствие в нем возможности управления временными параметрами формируемых импульсов,сравнительно большая дискретность задания сдвига фазы и коэффициента заполнения формируемых импульсов, которая равна периоду опорных синхроимпульсов, жестко за10данный период следования выходных сигналов зависящий от количества разрядов применяемого счетчика импульсов. Это не позволяет задавать требуемую временную диаграмму без

15 изменения конструктивных связей формирователя, а уменьшение дискрет ности изменения временных параметров требует применения элементной базы с повышенным быстродействием, явля20ющейся недоступной для широкого пользования.

Цель изобретения - расширение функциональных возможностей за счет

обеспечения возможности программного управления временными соотношениями выходных импульсов, уменьшения дискретности задания (программирования) коэффициента заполнения и сдвига фазы выходных импульсов относительно опорного синхроимпульса, а также программного управления частотой следования формируемых импульсов.

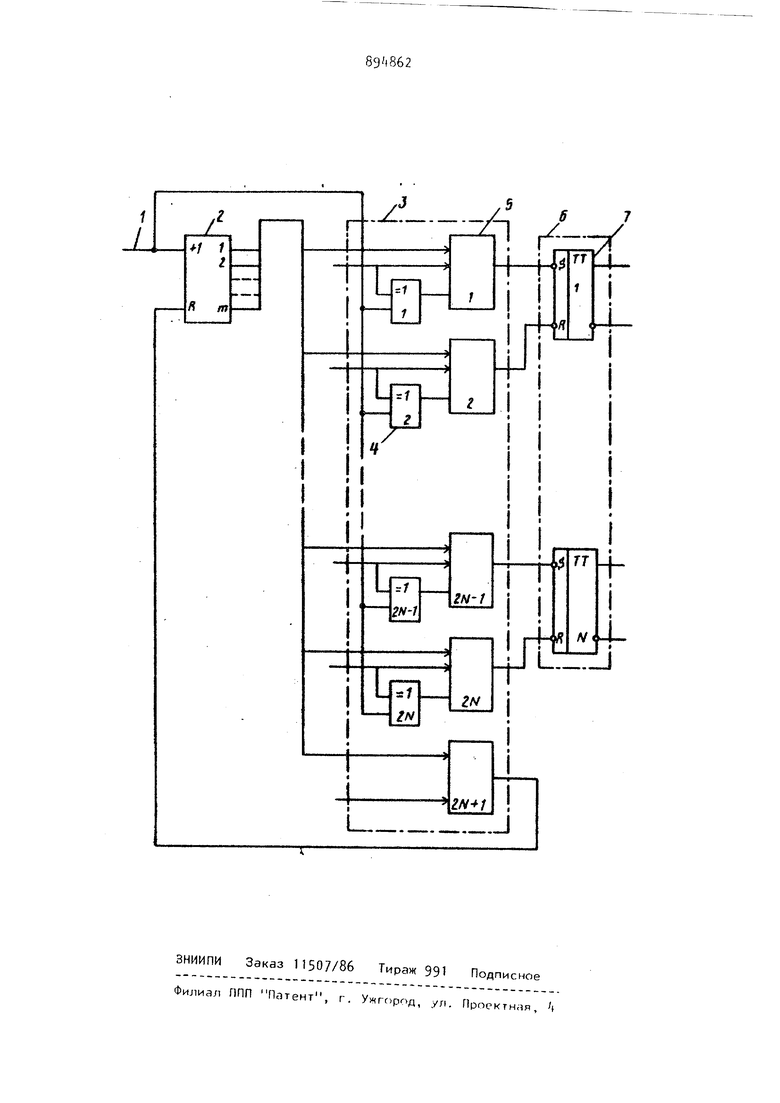

Эта цель достигается тем, что в формирователе многофазного сигнала, содержащем счетчик импульсов, выходы которого соединены с входными шинами программного блока, стробирующий вход которого соединен со входом счетчика импульсов и шиной тактовых импульсов, а выходы программного блока подключены ко входам триггеров регистра, программный блок состоит из 2N элементов Исключающее ИЛИ и 2N+1 элементов сравнения, причем первые входь элементов сравнения соединены с входными шинами программного блока, стробирующий вход которого подключен к первым входам элементов Исключающее ИЛИ, а вторые входы элементов сравнения и элементов Исключающее ИЛИ соединены с дополнительными входными шинами программного блока, выходы которого соединены с выходами 2N, элементов сравнения, стробирующие входы которых подключены к выходам элементов Исключающее ИЛИ, а выход (2N+1)-ro элемента сравнения соединен со входом сброса счетчика импульсов.

На чертеже приведена структурная схема формирователя многофазного сигнала.

Устройство содержит шину 1 тактовых импульсов, счетчик 2, программный блок 3 включающий элементы k Исключающее ИЛИ, и элементы 5 сравнения, регистр 6, состоящий из триггеров 7.

Формирователь многофазного сигнала работает следующим образом.

В исходном состоянии .счетчик импульсов 2, а также все триггеры 7 находятся в нулевом состоянии. При появлении на шине 1 последовательности опорных синхроимпульсов, поступающих на счетный вход счетчика 2, на его входах образуется последовательность двоичных кодовых комбинаций, которые поступят на первые входы элементов S сравнения,, на вторые входы которых подаются заданные кодовые

комбинации от какого-либо источника информации. В момент времени, когда на первых и вторых входах какого-то из нечетных (первый, третий и т.д.)

элементов 5 сравнения кодовые комбинации становятся равными, на выходе этого элемента по переднему фронту импульса, поступающему на его стробирующий вход, формируется импульс,

который поступает на первый вход соответствующего триггера 7 и переводит его в единичное состояние. Данный триггер 7 будет находиться в единичном состоянии до прихода импульса с выхода четного элемента 5 сравнения, соединенного со вторым входом этого триггера. Аналогичным образом происходит формирование всех выходных сигналов, при этом задержка

каждого из формируемых импульсов формирователя многофазного сигнала относительно начала отсчета, за которое принимается нулевое состояние счетчика импульсов 2, будет определяться кодовой комбинацией, поступающей на второй вход соответствующего нечетного элемента 5 сравнения, а длительность формируемого сигнала будет определяться разностью кодов, поступающих на вторые входы данной пары элементов сравнения (четного и нечетного) .

На первые входы элементов Исключающее ИЛИ поступает последовательность тактовых импульсов, а на вторые их входы поступают нулевые или единичные потенциалы с выходов источника информации, в зависимости от которых последовательность импульсов на выходах элементов 4 совпадает по фазе с последовательностью тактовых импульсов или сдвинута по фазе на 180 по отношению к ней. Возможность программного изменения фазы импульсов, поступающих на тактовые входы элементов 5 сравнения кодов, позволяет установку в единичное состояние триггеров 7 и их сброс в нулевое состояние производить по фронту или

спаду любого импульса из опорной последовательности. Это позволяет уменьшить дискретность программирования сдвига фазы и коэффициента заполнения выходных импульсов формирователя многофазного сигнала в два раза, т.е. достичь дискретности, равной То/2, где TQ- период следования тактовых импульсов.

Для осуществления программного управления периодом ч1)ормируемых сигналов используется (2N+1)-H элемент 5 сравнения, выходной импульс которого поступает на установочный вход сметчика 2 импульсов и устанавливает его в нулевое состояние. На этом цикл работы формирователя многофазного сигнала заканчивается и с приходом последующего опорного синхроимпульса следующий цикл его работы начинается.

Формула изобретения

Формирователь многофазного сигнала, содержащий счетчик импульсов, выходы которого соединены с входными шинами программного блока, стробирующий вход которого соединен со входом счетчика импульсов и шиной тактовых импульсов, а выходы программного подключены ко входам триггеров регистра, отличающийся тем, что, с целью расширения функциональных возможностей, программный блок состоит из 2N элементов Исключающее ИЛИ и 2N+1 элементов сравнения, причем первые входы элементов

сравнения соединены с входными шинами программного блока, стробирующий вход которого подключен к первым входам элементов Исключающее ИЛИ, а вторые входы элементов сравнения и элементов Исключающее ИЛИ соединены с дополнительными входными шинами программного блока, выходы которого соединены с выходами 2N элементов сравнения, стробирующие входы которых подключены к выходам элементов Исключающее ИЛИ, а выход (2N+1)-ro элемента сравнения соединен со входом сброса счетчика импульсов.

Источники информации,

принятые во внимание при экспертизе

Авторы

Даты

1981-12-30—Публикация

1980-01-21—Подача