ел

о

CD

00

ч

доа нечетных разрядов переносов сумматора 6 и четных разрядов переносов сумматора 5 и с выходов нечетных разрядов переносов сумматора 5 и четных разрядов переносов сумматора 6 соответственно. Сигналы с выходов суммы сумматоров 5 и 6 транслируются коммутатором 8 на выход 18 устройства соответственно в первом и втором полутактах тактов работы устройства.Вслед за разрядами первой пары сомножителей в регистры 1 и 2 вдвигаются без паузы разряды второй пары сомножителей. Группы элементов И 11 и 12 под действием управления исключают формирование конъюнкций сомножителей из смежных пар. 2 ил.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1988 |

|

SU1532918A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1711152A1 |

| Вычислительная ячейка | 1985 |

|

SU1287145A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1587498A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для выполнения арифметических действий. Целью изобретения является повышение производительности. Устройство содержит регистры 1 и 2, в которые вдвигаются множимое и множитель младшими разрядами вперед, группы элементов И 3 и 4, формирующие конъюнкции разрядов множимого и множителя соответственно с весовыми функциями 2°, 22,...,2K, и 21, 23,...,2K+1, где K = 0,1,...,7, регистры 9 и 10 управления и элемент И 13, вырабатывающие управляющие сигналы. Одноразрядные сумматоры 5 и 6 складывают конъюнкции, имеющие одинаковые в такте весовые функции соответственно с четным и нечетным значениями K, а также задержанные на регистрах группы 71 и 72 сигналы с выходов нечетных разрядов переносов сумматора 6 и четных разрядов переносов сумматора 5 и с выходов нечетных разрядов переносов сумматора 5 и четных разрядов переносов сумматора 6 соответственно. Сигналы с выходов суммы сумматоров 5 и 6 транслируются коммутатором 8 на выход 18 устройства соответственно в первом и втором полутактах тактов работы устройства. Вслед за разрядами первой пары сомножителей в регистры 1 и 2 вдвигаются без паузы разряды второй пары сомножителей. Группы элементов И 11 и 12 под действием управления исключают формирование конъюнкций сомножителей из смежных пар. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для выполнения арифметических дейст-вий.

Целью изобретения является повышение производительности.

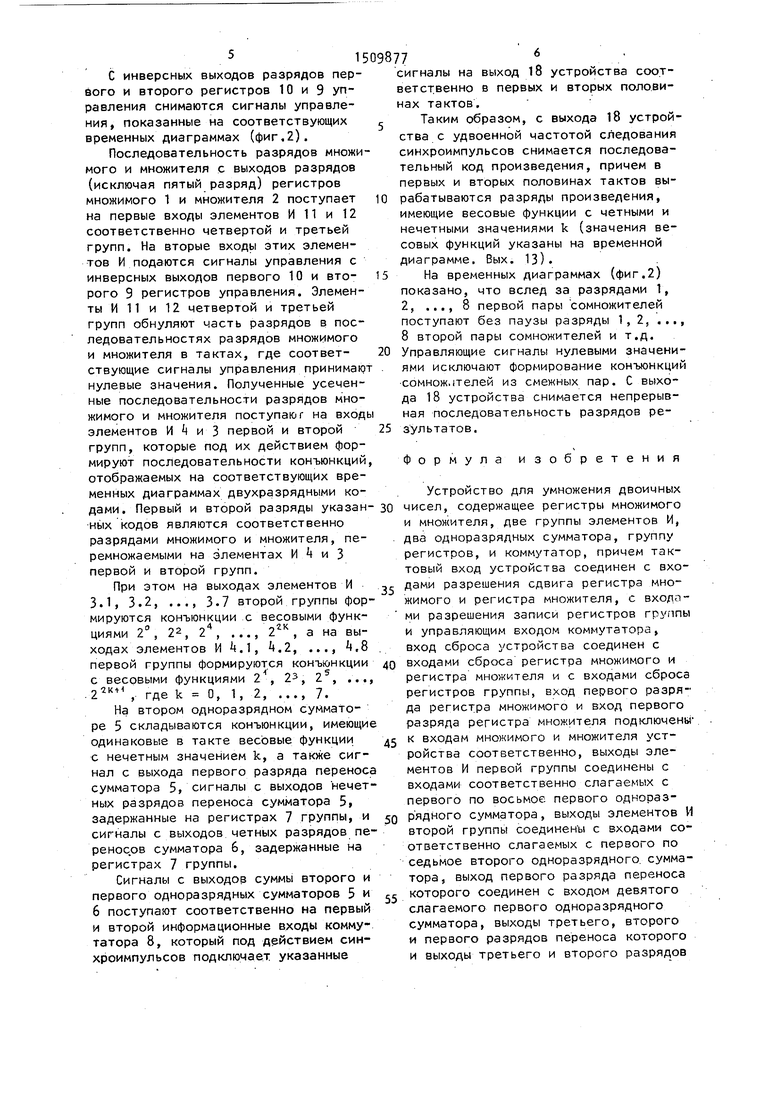

На фиг.1 представлена схема устройства для умножения двоичных чисел; на фиг.2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит регистр 1 мно- жимого, регистр 2 множителя, вторую группу элементов И 3.1, 3.2, ..., 3.7, первую группу элементов И 4,1, 4.2, ,.., ,8, второй одноразрядный сумматор 5, первый одноразрядный сум- матор 6, группу регистров 7.1 и 7.2, коммутатор 8, второй 9 и первый 10 регистры управления, четвертую группу элементов И 11.1, 11.2, ..., 11«7, третью группу элементов И 12.1, 12.2, ..., 12.7, элемент И 13, вход 14 множимого устройства, вход 15 множителя устройства, вход 1б .сброса устройства, тактовый вход 17 и выход 18 устройства.

Устройство работает следующим образом.

На тактовый вхой 17 устройства поступают синхроимпульсы СИ типа меандр, тактирующие работу устройства

На входы 14 и 15 множимого и множителя устройства с частотой следования синхроимпульсов поступают в последовательном коде разряды, начиная первого (младшего), множимого и множителя соответственно.

На вход 16 сброса устройства поступает импульс, сбрасывающий в ноль регистры 1 и 2 множимого и множителя регистры 7,1 и 1Л группы, а также .первый 10 и второй 9 регистры управления.

Под действием синхроимпульсов, поступающих на входы управления сдви

5

0

5 30 35 40

з

50

гом регистров 1 и 2 множимого и множителя, разряды множимого и множителя продвигаются в каждом такте в регистрах 1 и 2 на одну позицию s сторону старших разрядов.

При этом на выходах разрядов регистров 1 и 2 множимого и множителя формируются последовательности разрядов множимого и множителя в соответствии с временными диаграммами, представленными на фиг.2. Числа, указанные на временных диаграммах выходов разрядов регистров 1 и 2, означают номера разрядов множимого и множителя.

Одновременно с этим после обнуления первого и второго регистров 10 и 9 управления во второй регистр 9 управления под действием синхроимпульсов вдвигается единичное значение с инверсного выхода третьего разряда первого регистра 10 управления. С прямого выхода четвертого разряда второго регистра 9 управления единичное значение вдвигается в первый разряд первого регистра 10 управления. При этом элемент И 13, подключенный входами к прямым выходам четвертого разряда второго регистра 9 управления и первого разряда первого регистра 10 управления, вырабатывает единичный импульс, обнуляющий второй регистр 9 управления по второму входу сброса и устанавливающий в единичное значение все разряды первого регистра 10 управления по входу установки в единичный код.

Далее в первый регистр 10 управления вдвигается нулевое значение. При достижении третьего разряда с инверсного выхода этого разряда единичное значение поступает на вход первого разряда второго регистра 9 управления, и цикл работы регистров управления повторяется.

51

С инверсных выходов разрядов пер- його и второго регистров 10 и 9 уп равления снимаются сигналы управления, показанные на соответствующих временных диаграммах (фиг,2).

Последовательность разрядов множимого и множителя с выходов разрядов (исключая пятый разряд) регистров множимого 1 и множителя 2 поступает на первые входы элементов И 11 и 12 соответственно четвертой и третьей групп. На вторые входь этих элементов И подаются сигналы управления с инверсных выходов первого 10 и вто- рого 9 регистров управления. Элементы И 11 и 12 четвертой и третьей групп обнуляют часть разрядов в последовательностях разрядов множимого и множителя в тактах, где соответ- ствующие сигналы управления принимаю нулевые значения. Полученные усеченные последовательности разрядов множимого и множителя поступают на вход элементов И и 3 первой и второй групп, которые под их действием формируют последовательности конъюнкций отображаемых на соответствующих временных диаграммах двухразрядными ко

дами. Первый и второй разряды указан- зо чисел, содержащее регистры множимого нь1х кодов являются соответственно разрядами множимого и множителя, перемножаемыми на элементах И и 3 первой и второй групп.

При этом на выходах элементов И 3.1, 3.2, ..., 3.7 второй группы форс

мируются циями 2°

конъюнкции

2 7

) I .

ходах элементов И k., k.2,

весовыми функrt J/

.., 2 , а на выi.8

35

и множителя, две группы элементов И, два одноразрядных сумматора, группу регистров, и коммутатор, причем тактовый вход устройства соединен с вхо дами разрешения сдвига регистра множимого и регистра множителя, с входа ми разрешения записи регистров групп и управляющим входом коммутатора, вход сброса устройства соединен с входами сброса регистра множимого и регистра множителя и с входами сброс регистров группы, вход первого разря да регистра множимого и вход первого разряда регистра множителя подключен к входам множимого и множителя устройства соответственно, выходы элементов И первой группы соединены с входами соответственно слагаемых с первого по восьмое первого одноразрядного сумматора, выходы элементов второй группы соединены с входами со ответственно слагаемых с первого по седьмое второго одноразрядного, сумма тора, выход первого разряда переноса которого соединен с входом девятого слагаемого первого одноразрядного сумматора, выходы третьего, второго и первого разрядов переноса которого и выходы третьего и второго разрядов

первой группы формируются конъюнкции с весовыми функциями 2, 2, 2, ..., . .- где k О, 1, 2, ..., 7.

, I Ht, г - U, ,-, ...,

На втором одноразрядном сумматоре 5 складываются конъюнкции, имеющие одинаковые в такте весовые функции с нечетным значением k, а также си1- нал с выхода первого разряда переноса сумматора 5, сигналы с выходов нечетных разрядов переноса сумматора 5, задержанные на регистрах 7 группы, и сигналы с выходов четных разрядов пе- реносрв сумматора 6, задержанные на регистрах 7 группы.

Сигналы с выходов суммы второго и первого одноразрядных сумматоров 5 и 6 поступают соответственно на первый и второй информационные входы коммутатора 8, который под действием синхроимпульсов подключает указанные

6

сигналы на выход 18 устройства соответственно в первых и вторых половинах тактов.

Таким образом, с выхода 18 устройства с удвоенной частотой следования синхроимпульсов снимается последовательный код произведения, причем в первых и вторых половинах тактов вырабатываются разряды произведения, имеющие весовые функции с четными и нечетными значениями k (значения весовых функций указаны на временной диаграмме. Вых. 13).

На временных диаграммах (фиг.2) показано, что вслед за разрядами 1, 2, ..., 8 первой пары сомножителей поступают без паузы разряды 1,2, ... 8 второй пары сомножителей и т.д.

Управляющие сигналы нулевыми значениями исключают формирование конъюнкций сомнож.1телей из смежных пар. С выхода 18 устройства снимается непрерывная последовательность разрядов результатов.

Формула изобретения Устройство для умножения двоичных

зо чисел, содержащее регистры множимого

35

40

50

д5

55

и множителя, две группы элементов И, два одноразрядных сумматора, группу регистров, и коммутатор, причем тактовый вход устройства соединен с входами разрешения сдвига регистра множимого и регистра множителя, с входами разрешения записи регистров группы и управляющим входом коммутатора, вход сброса устройства соединен с входами сброса регистра множимого и регистра множителя и с входами сброса регистров группы, вход первого разряда регистра множимого и вход первого разряда регистра множителя подключены к входам множимого и множителя устройства соответственно, выходы элементов И первой группы соединены с входами соответственно слагаемых с первого по восьмое первого одноразрядного сумматора, выходы элементов И второй группы соединены с входами соответственно слагаемых с первого по седьмое второго одноразрядного, сумматора, выход первого разряда переноса которого соединен с входом девятого слагаемого первого одноразрядного сумматора, выходы третьего, второго и первого разрядов переноса которого и выходы третьего и второго разрядов

переноса второго одноразрядного сумматора соединены соответственно с входами разрядов с первого по пятый первого регистра группы, выход перво го разряда которого соединен с информационным входом второго регистра группы, выход которого соединен с входом восьмого слагаемого второго одноразрядного сумматора, входы девя того и десятого слагаемых которого соединены соответственно с выходами третьего и пятого разрядов первого регистра группы, выходы четвертого и второго разрядов которого соединен соответственно с входами десятого и одиннадцатого слагаемых первого одноразрядного сумматора, выходы суммы второго и первого одноразрядных сумматоров соединены соответственно с первым и вторым информационными входами коммутатора, выход которого является выходом устройства, первый и второй входы k-ro элемента И второй группы (k 1-7) соединены соответственно с вторым входом )-ro и с первым входом (9-k)-ro элементов И первой группы, выходы пятых разрядов регистра множимого и регистра множителя соединены соответственно с первым и вторым входами четвертого элемента И второй группы, отличающееся тем, что, с целью повышения производительности, оно содержит первый и второй регистры управления, третью и четвертую группы элементов И и элемент И, причем входы разрешения сдвига первого и второго регистров управления подключены к тактовому

входу устройства, вход сброса первого 40группы соединены соответственно с

регистра управления и первый входпервыми входами элементов И с первого

сброса второго регистра управленияпо четвертый и с шестого по восьмой

подключены к входу сброса устройства,первой группы, выходы элементов И

вход первого разряда первого регистра управления соединен с прямым выходом четвертого разряда второго регистра управления и с первым входом элемен- та И, второй вход которого соединен с прямым выходом первого разряда первого регистра управления, выход элемента И соединен с входом установки

50

0

5

0

5

1 первого регистра управления и с вторым входом сброса второго регистра управления, вход первого разряда которого соединен с инверсным выходом третьего разряда первого регистра управления, первые входы элементов И с первого по седьмой третьей группы соединены соответственно с выходами разрядов с первого по четвертый и с шестого по восьмой регистра множителя, вторые входы элементов И с первого по четвертый третьей группы соединены соответственно с инверсными выходами разрядов с первого по четвертый второго регистра управления, вторые входы элементов И с пятого по седьмой третьей группы соединены соответственно с инверсными выходами разрядов с первого по третий первого регистра управления, первые входы элементов И с первого по седьмой четвертой группы соединены соответственно с выходами разрядов с первого по четвертый и с шестого по восьмой регистры множимого, .вторые входы элементов И с первого по четвертый и с шестого по восьмой регистра множимого, вторые входы элементов И с первого по четвертый четвертой группы соеди- нены соответственно с инверсными вы- ходами разрядов с первого по четвертый второго регистра управления, вторые входы элементов И с пятого по седьмой четвертой группы соединены соответственно с инверсными выходами разрядов с первого по третий первого регистра управления, выходы элементов И с первого по седьмой третьей

с второго по седьмой четвертой группы соединены соответственно с первыми входами элементов И с первого по третий и с пятого по седьмой второй группы, выход первого элемента И четвертой группы соединен с вторым входом восьмого элемента И первой группы.

Вх.6 Вк.17 Bx.J i Вш.1э/1.1 Вых. 23A.I

Вых.Зэл. 1

BiilX.(3/1.1

Bbif.53/l.1

ВЫХ.бЗА.1

.73/l.t

Вш.8з/.1

Bx.JS

ВЫК.13Л.2

ВЫХ23Д.2

ВЫХ.ЗЗА.2.

Вы К.3/1.2

Вык.5з/1.г

дых.6 3/1.2 Вых.73/1.2 Вых.83/.2 Вых.13/1.3 Вых.2 3/1.9 ВЬ/Х.ЗЗ/l.S BblLl3/1.9 ВШ.13/1.0 BbiL23/l.W дых.Ззл.Ю

Вых.3/1.11

Вых.3/1.3-7.

дых.зл.3-6.

Вып.3/1.3-5.

Bux.3/J.3- f

Bl,lX.3/J.J-3.

ВЫИ.ЗЛ.3-2.

ВЫХ.3/1.3-1

Вып.3/1.-8

Bbix.3/i. f-7

Вых.з/r.-f.

Вых.3/1.-5.

ВЫХ.З/l. t- f.

Вых.зл. 1-З.

8Ш.З/.-2. ВЫХ.Э/.-.

Bbix.W

..кг:

51 fZ SJ 64 75 8S

Х

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| (S) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ двоичных ЧИСЕЛ | |||

Авторы

Даты

1989-09-23—Публикация

1988-03-10—Подача