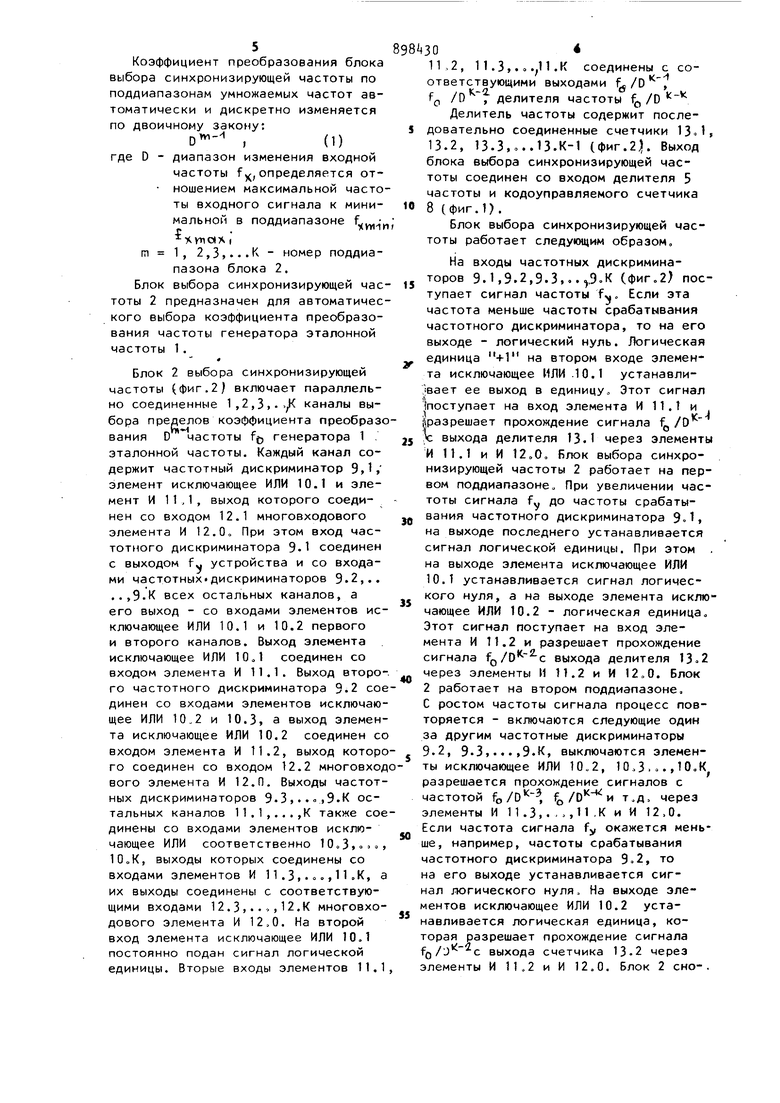

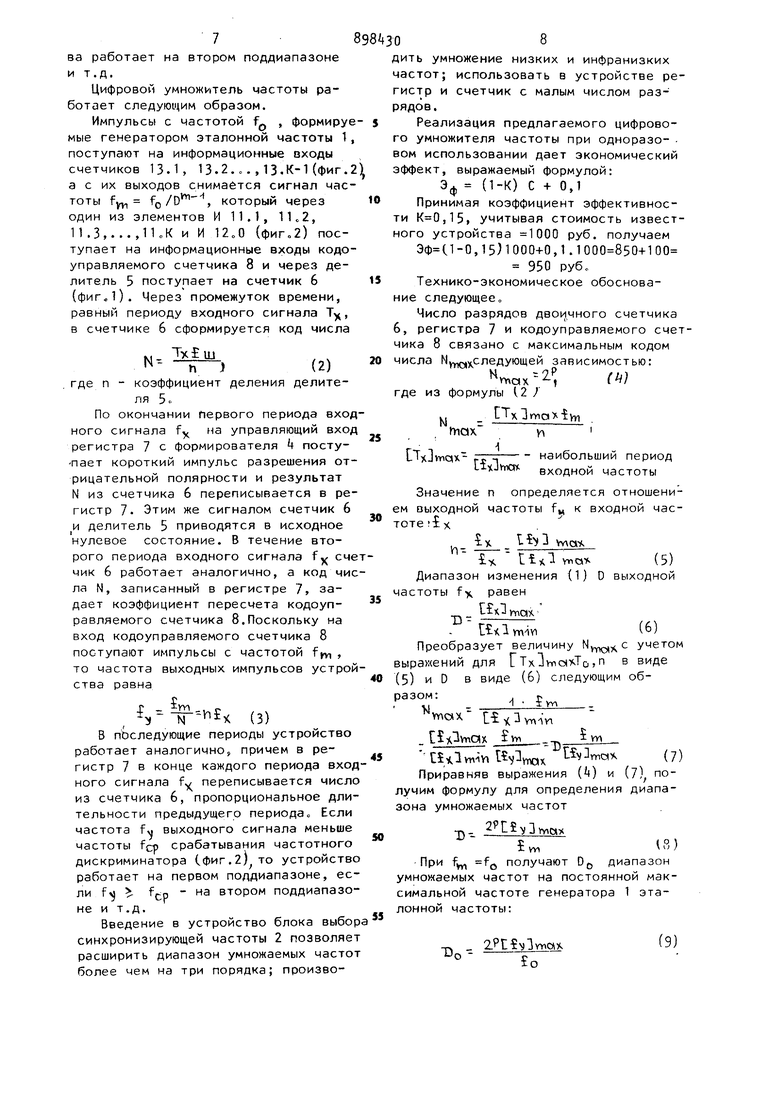

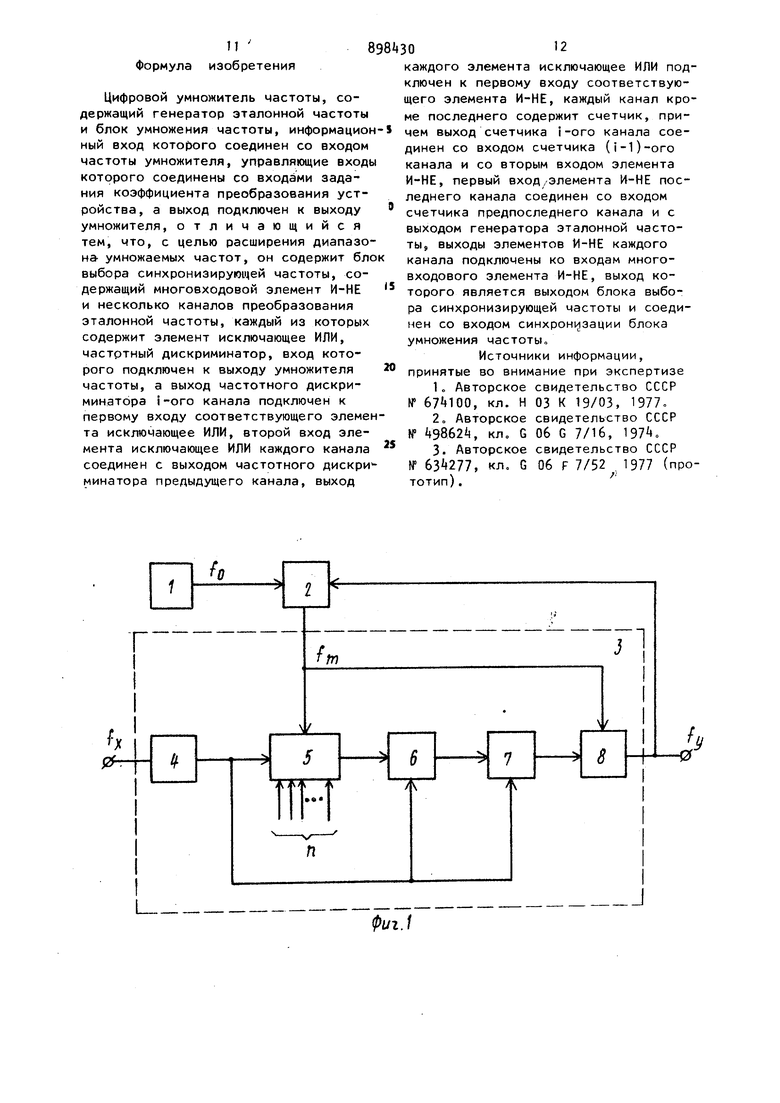

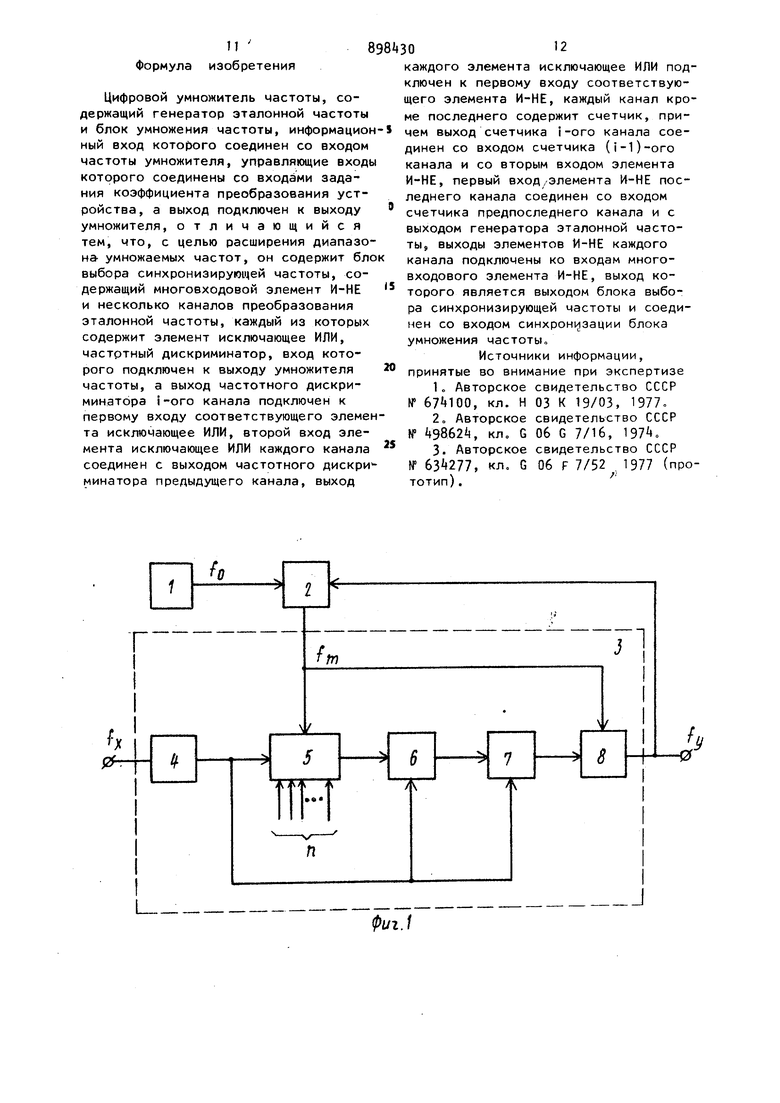

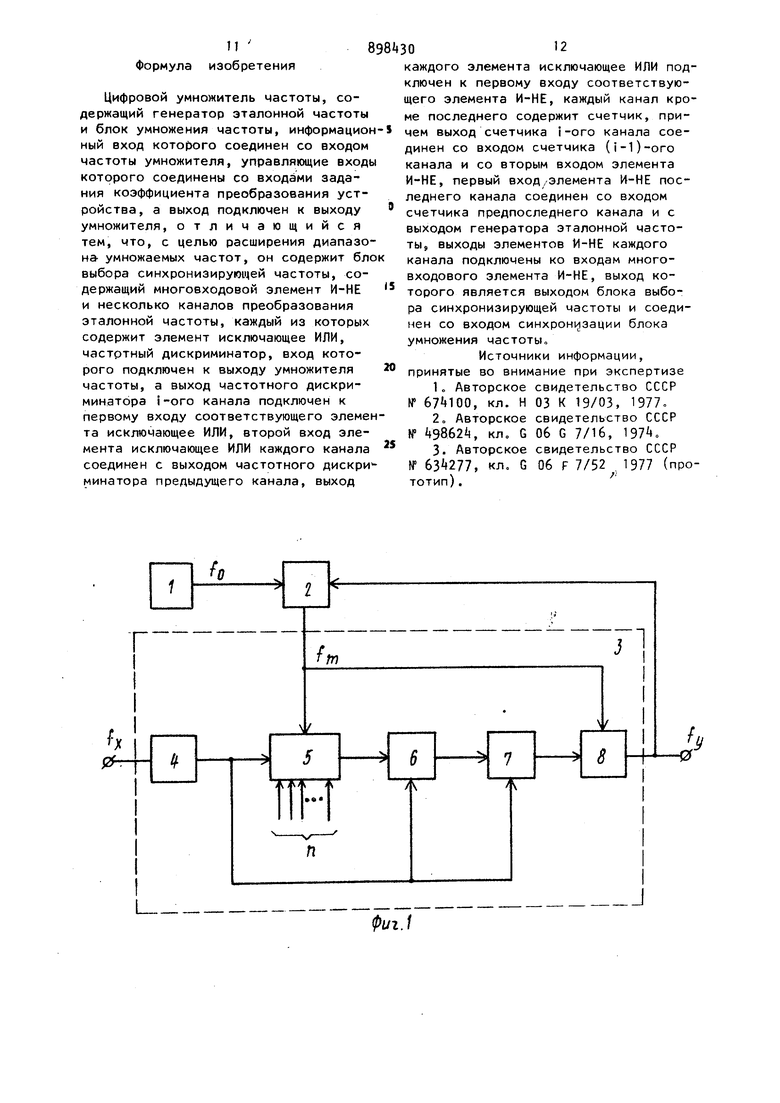

Изобретение относится к автоматике и вычислительной технике и может найти применение при обработке си1- налов частотных датчиков в качестве синхронизирующего устройства в бесфильтровых анализаторах спектра, а также в качестве управляемого аналого-цифрового преобразователя и тактирующего устройства в системах централизованного контроля. Известен цифровой умножитель частоты, содержащий последовательно соединенные генератор эталонной частоты, регистры сдвига и хранения, дешифратор и управляемую линию задержки выход которой через управляемый делитель частоты, элементы И и ИЛИ соединены с ее входом,, второй вход управ ляемого делителя частоты соединен со вторым входом элемента ИЛИ, со BXO дами регистров сдвига и хранения и с выходом формирователя импульсов. Вто рой выход управляемого делителя частоты соединен с дешифратором 1. Недостатками устройства являются узкий диапазон умножаемых частот, который ограничивается конечным числом разрядов регистров сдвига и хранения, дешифратора и линии задержки ограниченный диапазон умножаемых частот смещенный в область низких и инфранизких частот вследствие того, что частотой эталонного генератора, емкостью регистров сдвига и хранения дешифратором и линией задержки невозможно управлять в процессе работы устройства. Известен также цифровой умножитель частоты, содержащий генератор эталонной частоты, выход которого соединён с первым счетчиком и через делитель частоты - со входом второго счетчика, выход последнего через регистр соединен со входом блока сравнения кодов, вход устройства соединен с делителем частоты, с регистром, с дополнительным делителем частоты, с триггером, с элементом ИЛИ и со вторым счетчиком, выход которого соединен с блоком сравнения кодов, выход последнего соединен со вторым счетчиком и через элемент И - с три1- герои и элементом ИЛИ 2J „ К недостаткам устройства относятся узкий диапазон умножаемых частот, который ограничивается конечным числом разрядов счетчиков и регистров, а также ограниченный диапазон умножаемых частот, смещенный в область низких и инфранизких частот вследствие того, что частотой эталонного генератора, емкостью счетчиков и регистра невозможно управлять в процессе работы умножителя. Наиболее близким по технической сущности к предлагаемому устройству является цифровой следящий умножитель частоты, содержащий формирователь, вход которого соединен с информационным входом устройства, выход - с управляющими входами делителя частоты, счетчика и регистра, генератор эталонной частоты, выход которого подключен к информационным входам кодоуправляемого счетчика и делителя частоты, выход последнего подключен к информационному входу счетчика, разрядные выходы которого подключены к информационным входам регистра, выходы последнего соединен с управляющими входами кодоуправляющего счетчика, выход которого является выходом устройства З Однако устройство характеризуется узким диапазоном умножаемых частот, который ограничивается конечным числом разрядов счетчиков и регистра и ограниченным диапазоном умножаемых частот, смещенным в область низких и инфранизких частот вследствие того, что частотой эталонного генератора, емкостью счетчиков и регистра невозМОЖНО управлять в процессе работы ум ножителя« Целью изобретения является расши рение диапазона умножаемых частот. Поставленная цель достигается те что цифровой умножитель частоты, со держ.ащии генератор эталонной частот и блок умножения частоты, информационный вход которого соединен со в дом частоты умножителя, управляющие входы которого соединены со входами задания коэффициента преобразования устройства, а выход подключен к выходу умножителя, содержит блок выбо ра синхронизирующей частоты, содеращий многовходовой элемент И-НЕ и несколько каналов преобразования эталонной частоты, каждый из которых содержит элемент исключающее ИЛИ, частотный дискриминатор, вход которого подключен к выходу умножителя частоты, а выход частотного дискриминатора i-ro канала подключен к первому входу соответствующего элемента исключающее ИЛИ, второй вход элемента исключающее ИЛИ каждого канала соединен с выходом частотного дискриминатора предыдущего канала, выход каждого элемента исключающее ИЛИ подключен к первому входу соответствующего элемента -И-НЕ, каждый канал кроме последнего содержит счетчик, причем выход счетчика i-oro канала соединен со входом счетчика {i-1)-oro канала и со вторым входом элемента И-НЕ, первый вход элемента И-НЕ последнего канала соединен с входом счетчика предпоследнего канала и с выходом генератора эталонной частоты, выходы элементов И-НЕ каждого канала подключены ко входам многовходового элемента И-НЕ, выход которого является выходом блока выбора синхронизирующей частоты и соединен со входом синхронизации блока умножения частоты. На фиг. 1 приведена блок-схема цифрового умножителя частоты; на j фиГо 2 - схема блоке выбора синхронизирующей частоты. Цифровой умножитель частоты содержит генератор 1 эталонной частоты, блок 2 выбора синхронизирующей частоты и блок 3 умножения частоты, который, например, содержит формирователь импульсов , вход которого соединен с информационным входом fy устройства, выход - с управляющими входами делителя 5 частоты, счетчика 6 и регистра 7 выходы которого соединены с управляющими входами кодоуправляемого счетчика 8. Выход f генератора 1 эталонной частоты подключен к информационному входу блока 2 выбора синхронизирующей частоты, выход которого соединен с информационными входами кодоуправляемого счетчика 8 и делителя 5 частоты Выход кодоуправляемого счетчика 8 является выходом f устройства и соединен с управляющим входом блока выбора синхронизирующей частоты. Коэффициент преобразования блока выбора синхронизирующей частоты по поддиапазонам умножаемых частот автоматически и дискретно изменяется по двоичному закону: , где D - диапазон изменения входной частоты f, определяется от ношением максимальной часто ты входного сигнала к минимальной в поддиапазоне xvnoix t m 1, 2,3,...К - номер поддиапазона блока 2. Блок выбора синхронизирующей час тоты 2 предназначен для автоматичес кого выбора коэффициента преобразования частоты генератора эталонной частоты 1. Блок 2 выбора синхронизирующей частоты (фиг.2) включает параллельно соединенные 1,2,3,../ каналы выбора пределов коэффициента преобразо вания D частоты f(5 генератора 1 . эталонной частоты. Каждый канал содержит частотный дискриминатор 9,1, элемент исключающее ИЛИ 10.1 и элемент И 11.1, выход которого соединен со входом 12.1 многовходового элемента И 12.0„ При этом вход частотного дискриминатора 9.1 соединен с выходом f устройства и со входаМИ частотных дискриминаторов 9.2,.. ..,9.К всех остальных каналов, а его выход - со входами элементов ис ключающее ИЛИ 10.1 и 10.2 первого и второго каналов. Выход элемента исключающее ИЛИ ЮЛ соединен со входом элемента И 11.1. Выход второ го частотного дискриминатора 9.2 со динен со входами элементов исключаю щее ИЛИ 10,2 и 10.3, а выход элемен та исключающее ИЛИ 10.2 соединен со входом элемента И 11.2, выход которо го соединен со входом 12.2 многовход вого элемента И 12.П. Выходы частот ных дискриминаторов 9.3,...9.К остальных каналов 11.1,...,К также сое динены со входами элементов исключающее ИЛИ соответственно 10оЗ,о,о 10„К, выходы которых соединены со входами элементов И 11 .3,.«.,11.К, а их выходы соединены с соответствующими входами 12.3,..о,12.К многовходового элемента И 12.0. На второй вход элемента исключающее ИЛИ 10.1 постоянно подан сигнал логической единицы. Вторые входы элементов 11.1 30 11,2, 1 1.3,. о .,11 .К соединены с соответствующими выходами fjj/D fp /D, делителя частоты /О Делитель частоты содержит последовательно соединенные счетчики 13о1, 13.2, 13.3,о..13.К-1 (фиг.2). Выход блока выбора синхронизирующей частоты соединен со входом делителя 5 частоты и кодоуправляемого счетчика 8 (фиг.1). Блок выбора синхронизирующей частоты работает следующим образом. На входы частотных дискримина,лп«о «„/ -, °Р°« 9.1,9.2,9.3,,. ,,9Ж (фиг.2) поступает сигнал частоты т«. Если эта частота меньше частоты срабатывания частотного дискриминатора, то на его выходе - логический нуль. Логическая единица +1 на втором входе элемента исключающее ИЛИ.10.1 устанавли.;вает ее выход в единицу „ Этот сигнал поступает на вход элемента И 11.1 и . V -4 |разрешает прохождение сигнала f /D X выхода делителя 13.1 через элементы И 11.1 и И 12„0, Блок выбора синхронизирующей частоты 2 работает на первом поддиапазоне. При увеличении частоты сигнала fy до частоты срабатывания частотного дискриминатора 9-1, на выходе последнего устанавливается сигнал логической единицы. При этом . на выходе элемента исключающее ИЛИ 10.1 устанавливается сигнал логического нуля, а на выходе элемента исключающее ИЛИ 10.2 - логическая единица Этот сигнал поступает на вход элемента И tl.2 и разрешает прохождение сигнала выхода делителя 13.2 через элементы И 11.2 и И 12„0. Блок 2 работает на втором поддиапазоне, С ростом частоты сигнала процесс повторяется - включаются следующие один за другим частотные дискриминаторы 9.2, 9.3,...,9.К, выключаются элементы исключающее ИЛИ 10.2, 10.3..,10,К разрешается прохождение сигналов с частотой fo/0, т.д. через элементы И 11.3,...,11.К и И 12,0. Если частота сигнала fy окажется меньше, например, частоты срабатывания частотного дискриминатора 9.2, то на его выходе устанавливается сигнал логического нуля. На выходе элементов исключающее ИЛИ 10.2 устанавливается логическая единица, которая разрешает прохождение сигнала fg/j c выхода счетчика 13.2 через элементы И 1К2 и И 12,0. Блок 2 сно-. ва работает на втором поддиапазоне и т.д. Цифровой умножитель частоты работает следующим образом. Импульсы с частотой f , формиру мые генератором эталонной частоты t поступают на информационные входы счетчиков 13.1, 13.2.о,,13.К-1(фиг. а с их выходов снимается сигнал час тоты fуу, fo/D, который через один из элементов И 11.1, 1U2, 11 .3,...,11сК и И 12.0 (фиг.2) поступает на информационные входы кодо управляемого счетчика 8 и через делитель 5 поступает на счетчик 6 (фиг.Т). Через промежуток времени, равный периоду входного сигнала Т, в счетчике 6 сформируется код числа N-, h J (2) где n - коэффициент деления делителя 5. По окончании Первого периода вхо ного сигнала f на управляющий вхо регистра 7 с формирователя 4 поступает короткий импульс разрешения от рицательной полярности и результат N из счетчика 6 переписывается в ре гистр 7. Этим же сигналом счетчик 6 и делитель 5 приводятся в исходное нулевое состояние. В течение второго периода входного сигнала f сч чик 6 работает аналогично, а код чи ла N, записанный в регистре 7, задает коэффициент пересчета кодоуправляемого счетчика 8.Поскольку на вход кодоуправляемого счетчика 8 поступают импульсы с частотой f у, , то частота выходных импульсов устро ства равна f., : N (3) В пЬследующие периоды устройство работает аналогично, причем в регистр 7 в конце каждого периода входного сигнала f переписывается число из счетчика 6, пропорциональное длительности предыдущего периода., Если частота f« выходного сигнала меньше частоты fcp срабатывания частотного , - i дискриминатора Сфиг. устройство работает на первом поддиапазоне, если f , - на втором поддиапазоне и т.д. Введение в устройство блока выбора синхронизирующей частоты 2 позволяет расширить диапазон умножаемых частот более чем на три порядка; произво08дить умножение низких и инфранизких частот; использовать в устройстве регистр и счетчик с малым числом разрядов. Реализация предлагаемого цифрового умножителя частоты при одноразо- . вом использовании дает экономический эффект, выражаемый формулой: Эф (1-К) С + 0,1 Принимая коэффициент эффективности ,15, учитывая стоимость известного устройства 1000 руб. получаем Эф(1-О,15)1000+0,1.1000 850+100 950 руб. Технико-экономическое обоснование следующее,. Число разрядов двои чного счетчика 6, регистра 7 и кодоуправляемого счетчика 8 связано с максимальным кодом числа Ну следующей зависимостью: п. (1 где из формулы (2 } - - наибольший период Ci ;lhia% входной частоты Значение n определяется отношением выходной частоты f к входной частоте tix IL. )k ч ti, (5) Диапазон изменения (1) D выходной частоты f равен linl tt lm-ivi Преобразует величину Ny с учетом выражений для L Тх Jvtio(xTu,n в виде (5) и D в виде (6) следующим образом:К VYicsx- , - Зутлш УУ ---д,, w tHlwvi (7) Приравняв выражения (k) и (7), получим формулу для определения диапазона умножаемых частот D- ,«х iw.( При fy fQ получают D диапазон умножаемых частот на постоянной максимальной частоте генератора 1 эталонной частоты: ZPtblmoib Из формулы (8) следует, что для расширения диапазона умножаемых частот необходимо увеличивать число раз рядов Р счетчиков 6 и 8 и регистра 7 либо умненьшать частоту fy , которая связана с fe следующей зависимостью io hr, ,3,...,К., (10 VVA -jjVTiгде m - номер поддиапазона блока выбора синхронизирующей частоты 2. Подставив выражение UO) в формулу (, 8), получают значения поддиапазонов умножаемых частот в соответствии с номером, при определяют общий диапазон. 2РС€х, .. Т)-Преимущество предлагаемого цифрового умножителя частоты в сравнении с известными заключается в следующем Пусть число разрядов счетчиков и регистра равно и - 16,При это емкости счетчиков 6 и 8 и регистра 7 составляют соответственно «096 и 65 536 импульсов, частота генератора 1 эталонной частоты f 10, Макси мальная частота входного сигнала L 000 Гц, а максимальная частр та выходного сигнала Clv HiOOT ° , тогда коэффициент преобразования делителя 5 равен Зададимся погрешностью умножения устройства сГ 0,1, которая определяется по формуле: ЮО И- TO TX С помощью Формулы определяют D для Ра (По ) и Р2 16 (,5 и по формуле (10) частоты 0 г О ,5 VYi-i 4 /12) +ЗО.О Согласно заданным значениям Р, f , fp в таблице приведены изменения частот эталонного генератора 1 и входного сигнала для каждого поддиапазона rti. Согласно результатам, приведенным в таблице, применение в устройстве блока выбора синхронизирующей частоты,например, с шестью поддиапазонами, счетчиков 6 и 8 и регистра 7 с числом разрядов, равным позволяет расширить , пазом умножаемых частот от до „Ю (CtJn, 0,25 и , Гц) при изменении частоты f., от 10 до . В свою очередь, применение счетчиков 6 и 8, регистра 7 с числом разрядов f 16 и блока 2, имеющего, например три поддиапазона, позволяет расширить диапазон умножаемых частот от 65,5 до ,0035 Гц и С) Гц при изменении частоты 2,. Ю Гц„ При прочих равных условиях в известных устройствах, в которых число разрядов счетчиков и регистра или частота эталонного генератора не изменяются в процессе работы, диапазон умножаемых частот изменяется в раза для Р 12 и в 65,5 раза для Р, Для умножения входного сигнала с частотой ,0035 Гц эти устройства должны иметь счетчики и регистр с числом разрядов более тридцати.Все это усложняет устройство и повышает его стоимость, тогда как ожидаемый экономический эффект при одноразовом использовании предлагаемого цифрового умножителя частоты составляет 950 руб..

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| Устройство для измерения показателя тепловой инерции частотных термодатчиков | 1982 |

|

SU1075090A1 |

| Устройство для контроля фазочастотных характеристик четырехполюсников | 1989 |

|

SU1758600A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

| Анализатор распределений вероятностей временных интервалов между соседними выбросами случайных процессов | 1977 |

|

SU746317A2 |

| Устройство для синхронизации равнодоступных многоканальных систем связи | 1975 |

|

SU563736A1 |

| Умножитель частоты | 1980 |

|

SU868756A1 |

л , f lvYinvi,Гц ГЕхЗугох, Гц . - о -vvia 6,5 Поддиапазоны 62,5 15,6 3,9 1,5о10 2,4.10 62,5 15,6 Формула изобретения Цифровой умножитель частоты, содержащий генератор эталонной частоты и блок умножения частоты, информацио ный вход которого соединен со входом частоты умножителя, управляющие вход которого соединены со входами задания коэффициента преобразования устройства, а выход подключен к выходу умножителя, отличающийся тем, что, с целью расширения диапазо на- умножаемых частот, он содержит бл выбора синхронизирующей частоты, содержащий многовходовой элемент И-НЕ и несколько каналов преобразования эталонной частоты, каждый из которых содержит элемент исключающее ИЛИ, частртный дискриминатор, вход которого подключен к выходу умножителя частоты, а выход частотного дискриминатора i-oro канала подключен к первому входу соответствующего элеме та исключающее ИЛИ, второй вход элемента исключающее ИЛИ каждого канала соединен с выходом частотного дискри минатора предыдущего канала, выход

I

иг. 012 каждого элемента исключающее ИЛИ подключен к первому входу соответствующего элемента И-НЕ, каждый канал кроме последнего содержит счетчик, при|- - llv i 4 . -1 V NirV, IV -l l-irIINjII KI цем выход счетчика i-ого канала соединен со входом счетчика (i-l)-oro канала и со вторым входом элемента И-НЕ, первый вход/элемента И-НЕ последнего канала соединен со входом счетчика предпоследнего канала и с выходом генератора эталонной частоты, выходы элементов И-НЕ каждого канала подключены ко входам многовходового элемента И-НЕ, выход которого является выходом блока выбора синхронизирующей частоты и соединен со входом синхронизации блока умножения частоты Источники информации, принятые во внимание при экспертизе 1 о Авторское свидетельство СССР № , кл. Н 03 К 19/03, 1977. 2о Авторское свидетельство СССР № i 9862i{, кл, G Об G 7/16, 3. Авторское свидетельство СССР № , кло G 06 F 7/52 , 1977 (прототип) .

э4

Авторы

Даты

1982-01-15—Публикация

1980-04-15—Подача