( 5А ) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ п-РАЗРЯДНЫХ ДЕСЯТИЧНЫХ

ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения п-разрядныхдЕСяТичНыХ чиСЕл | 1979 |

|

SU824203A1 |

| Двоично-десятичный сумматор | 1981 |

|

SU1019441A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| КОМБИНАЦИОННЫЙ СУММАТОР СТРУКТУРНЫХ КОДОВ | 1991 |

|

RU2023288C1 |

| Двоично-десятичный сумматор | 1977 |

|

SU746509A1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Устройство для суммирования двоично-десятичных кодов | 1976 |

|

SU691851A1 |

t

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных машинах.

Известно устройство для сложения десятичных чисел, которое позволяет осуществить коррекцию результата суммирования за один такт СО.

Недостатками этого устройства являются необходимость коррекции результата и использование в декадах кода без ошибкообнаруживаямцей способности.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство для сложения празрядных десятичных чиселj в котором для представления каждой десятичной цифры используется Фибоначчиевая система счисления и исключается коррекция результата сложения. Каждый разряд устройства включает четыре сумматора сложения двух чисел и элемент ИЛИ 21.

Недостатком известного устройства является то, что в случае вoзник ювения переноса в i-й десятичный разряд требуется дополнительный такт сложения на суммирование единицы переноса и суммы цифр в этом разряде. Это приводит к снижению быстродействия работы сумматора десятичных чисел.

Цель изобретения - повышение

10 быстродействия устройства суммирования десятичных чисел.

Поставленная цель достигается тем, что в устройстве для сложения п-разрядных десятичных чисел, дый i-й разряд которого (,2,.,.п) содержит четыре двоичных сумматора и первый элемент ИЛИ, выходы суммы первого, второго, третьего и четвертого двоичных сумматоров данного

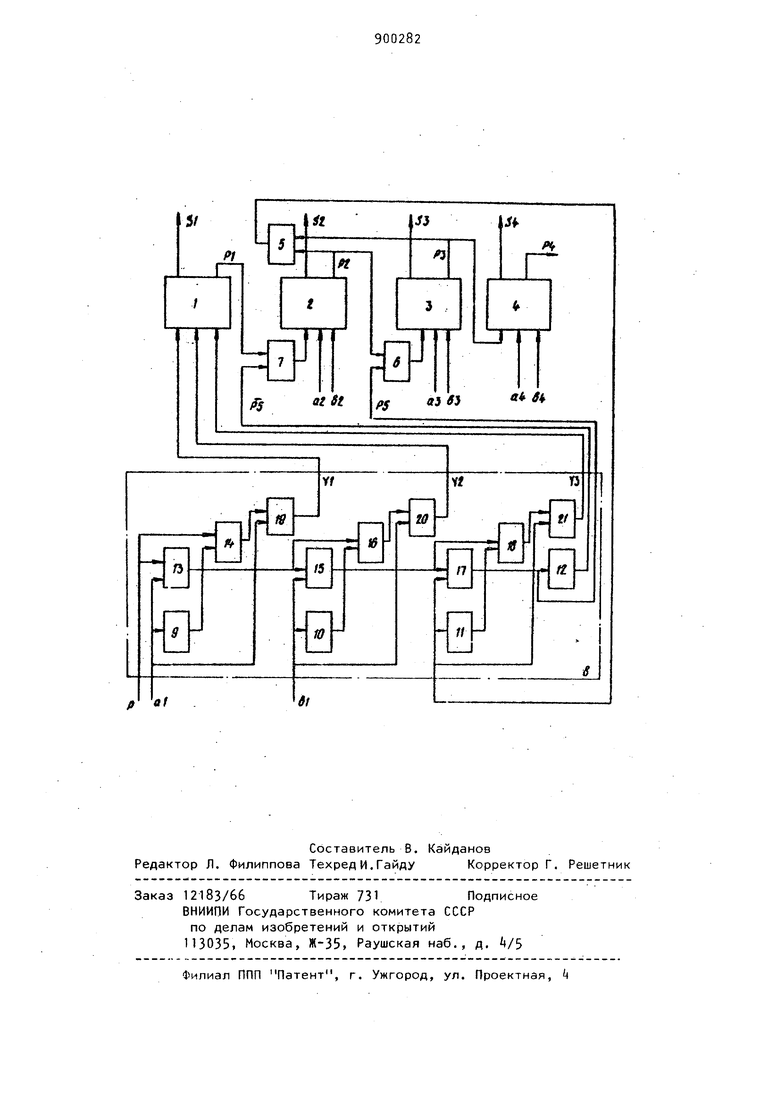

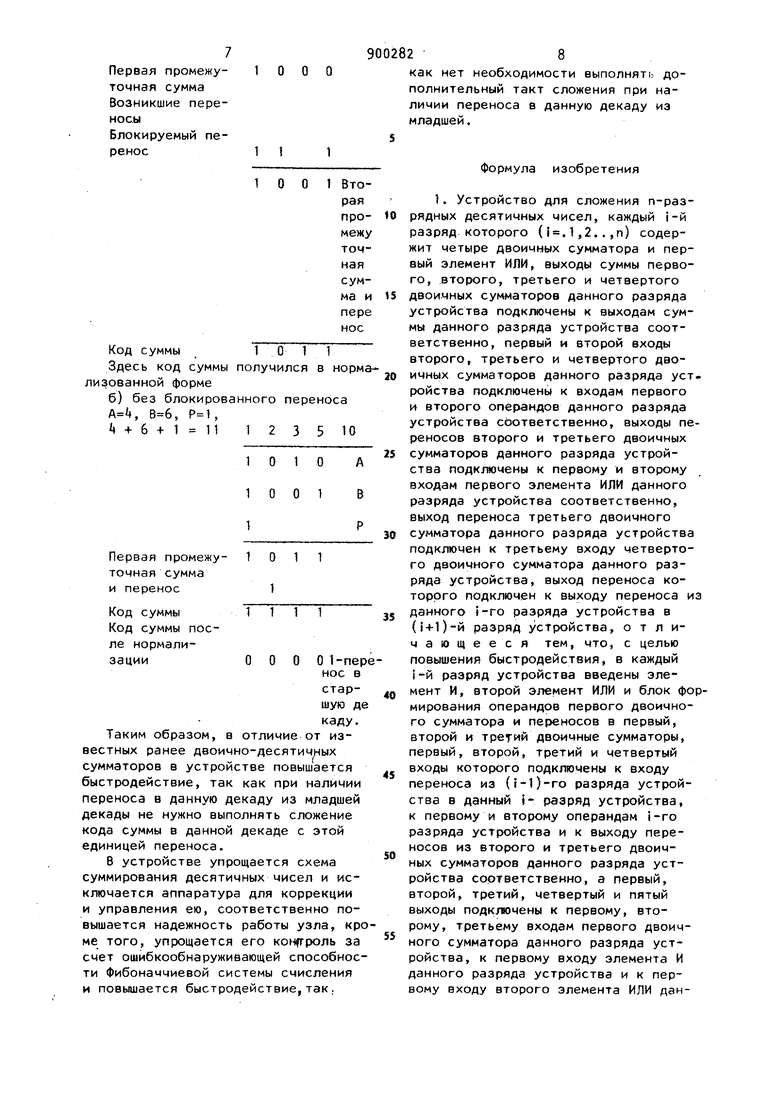

20 разряда устройства подключены к выходам суммы данного разряда устройства соответственно, первый и второй входы второго, третьего и четвертого двоичных сумматоров данного разряда устройства подключены к входам первого и второго операндов данного разряда устройства соответственно, выходы переносов второго и третьего двоичных сумматоров данного разряда устройства подключены к первому и второму входам первого элемента ИЛИ данного разряда устройства соответственноJвыход переноса тре тьего двоичного сумматора данного разряда устройства подключен к третьему входу четвертого двоичного сум матора данного разряда устройства, выход переноса которого подключен к выходу переноса из данного f-ro разряда устройства в (|+1)-й разряд уст ройства, в каждый i-й разряд устройства введены эяеиент И, второй элемент ИЛИ и блок формирования операндов первого двоичного сумматора и переносов в первый, второй и третий двоичные сумматоры, первый, второй, третий и четвертый двоичные входы которого подключены к входу переноса из ( разряда, устройства в данный i-й разряд устройства, к первому и второму операндам i-ro разряда устройства и к выходу переносов из второго и третьего двоичных сумматоров данного разряда устройства соответственно, а первый, второй, третий, четвертый и пятый выходы подключены к первому, второму, третьему входам первого двоичного сумматора данного разряда устройства, к первому входу элемента И данного разряда устройства и к первому входу второго элемента ИЛИ данного разряда устройства соответственно, второй вход второго элемента ИЛИ подключен к выходу переноса второго двоичного сумматора дан ноге разряда устройства, второй вход элемента И подключен к выходу переноса первого двоичного сумматора данного разряда устройства. Кроме того, блок формирования опе рандов первого двоичного сумматора и переносов в первый, второй и третий двоичные сумматоры содержит три элемента ИЛИ, шесть элементов И и четыре элемента НЕ, причем первый вход блока подключен к первым входам первого и второго элементов И, второй вход блока подключен к входу первого элемента НЕ, к первому входу первого элемента ИЛИ и ко второму входу первого элемента И, выход первого эле2 .4 мента НЕ подключен ко второму входу второго, элемента ИЛИ, выход которого подключен ко второму входу первого элемента ИЛИ,выход которого подключен к первому выходу блока, второй и третий выходы которого подключены к выходам второго и третьего элементов ИЛИ соответственно, выход первого элемента И подключен к первым входам третьего и четвертого элементов И, третий вход блока подключен ко второму входу третьего элемента И, к первому входу второго элемента ИЛИ и ко входу второго элемента НЕ, выход которого подключен ко второму входу четвертого элемента И, выход которого подключен ко второму входу второго элемента ИЛИ, выход третьего элемента И подключен к первым входам пятого и шестого элементов И, четвертый вход блока подключен ко второму входу пятого элемента И, к первому входу третьего элемента НЕ, выход которого подключен ко второму входу шестого элемента И, выход которого подключен ко второму входу третьего элемента ИЛИ, выход четвертого элемента НЕ подключен к четвертому выходу блока, пятый выход которого подключен к выходу пятого элемента И и ко входу четвертого элемента НЕ. На чертеже приведена функциональная схема одной декады устройства. Схема состоит из четырех трехвходовых однозарядных двоичных сумматоров , элементов ИЛИ 5 и 6, элемента И 7 и блока 8 логических элементов, которьй состоит из четырех элементов НЕ , шести элементов И , и трех элементов ИЛИ 19-21. 0 данном устройстве на входы блока 8 логических элементов i-ro разряда поступают сигналы от первого и второго операндов и переноса из(i -1) -го разряда, от первого и второго операндов и переноса от второго и третьего трехвходовых одноразрядных двоичных сумматоров данного десятичного разряда. Если из этих четырех сигналов один нулевой, то блок логических элементов передает единичные сигналы на входы первого трехвходового одноразрядного двоичного сумматора данного десятичного разряда, и суммирование осуществляется без блока 8, Если все сигналы на входе блока 8 единичные, то сложение в младшем 5 разряде (с весом 1) осуществляется соответствии с правилом 1+1+1+1 1 и формируется перенос в разряд с весо 3. Это достигается тем, что блок 8 логических элементов выдает на вход первого трехвходового одноразрядног двоичного сумматора данного десятич ного разряда единицы, блокирует выход переноса этого сумматора и формирует перенос, поступающий на вход третьего трехвходового одноразрядного двоичного сумматора данного де сятичного разряда. В соответствии с этим блок 8 логических элементов реализует следую щие логические функции: 1 Р«1 Va jftpg V У,- Ра (Pj VP,) V (Д V Р, ) Р, раД tPjVP,), где Р перенос из предыдущего деся тичного разряда; переносы из второго и третье го разрядов данной декады; 01,& - двоичные ЦИФРЫ разрядов данных декад слагаемых; PJ- - перенос в третий разряд дан,ной декады. Одноразрядные сумматоры 1-Ц представляют обычные в классической двоичной арифметике сумматоры, которые соответствуют разрядам с весом 1,2, 3,5 и соединены между собой цепями переносов на основании правил суммирования в разрядах декады, т.е. перенос Р подается через элемент И 7 на вход сумматора 2, перенос Bjчерез элемент ИЛИ 6 на вход сумматора 3 и через элемент ИЛИ 5 на вход блока логических элемейтов, перенос РЗ; - на вход сумматора «и через эяе мент ИЛИ 5 - на вход блока логических элементов, перенос Рц - перенос в следующую декаду. Элемент ИЛИ 5 введен для того, чтобы блок логических элементов имел четыре входа. Он не искажает результата суммирования, так как од новременно переносы и Pj аозникнуть не могут из-за того, что на вход декады подаются коды в нормальной форме, т.е. наличие единиц во вт ром и третьем разрядах декады одновременно невозможно. Элемент ИЛИ 6 введен для реализации сложения четырех единиц в млад шем разряде декады. 3toT элемент не искажает результата суммирования. 82 так как одновременно пеоеносы Р и Pj (з блока логических элементов) возникнуть не могут по тем же причинам, что и в предыдущем случае. Элемент И 7 введен для реализации сложения четырех единиц в младВем разряде декады. По входу он подсоединен к выходу Ру блока логических элементов и в случае появления четырех единиц на входах блока логических элементов этот элемент блокирует распространение переноса f ;Блок 8 логических элементов введен для реализации сложения в млад.шем разряде декады. Он состоит из логических элементов , соединенных в соответствии с формулами для реализуемых блоком логических функций V;,, 3(j, -, FV . Блок логических элементов соедин на основании правил суммирования в разрядах декады с сумматорами 1 и 3, а также с элементом И 7, т.е. выходы ,,i/j,,j подключены к первому, второму и третьему входам сумматора 1, перенос Р через элемент ИЛИ 6 подается на вход сумматора 3 а выход Pf подключен к входу элемента И 7. Входы установки нуля не показаны. Устройство работает следующим образом . Одновременно на входы декады устройства поступают суммируемые десятичные цифры А и 8 в нормальной форме системы Фибоначчи и перенос из младшей декады Р, формируются переносы и первая промежуточная цифра, затем осуществляется подсуммирование переносов и блокирование переноса из младшего разряда декады в случае четырех единиц на входе блока логических элементов, образование второй промежуточной цифры и новых переносов и так до тех пор, пока не прекратится образование переносов и на выходах сумматоров 1- не образуется код . В дальнейшем этот код переписывается на нормализатор где с помощью операции свертки происходит нормализация кода результата. а) A«, Первая промежуточная сумма Возникшие переносыБлокируемый переносКод суммы 1011 Здесь код суммы получился в нор лизованной форме б) без блокированного переноса , , , Первая промежуточная сумма и перенос 1111 Код суммы Код суммы после нормалиО 1-п 000 зации нос стар шую каду Таким образом, в отличие от известных ранее двоично-десятичных сумматоров в устройстве повышается быстродействие, так как при наличи переноса в данную декаду из младше декады не нужно выполнять сложение кода суммы в данной декаде с этой единицей переноса. В устройстве упрощается схема суммирования десятичных чисел и ис ключается аппаратура для коррекции и управления ею, соответственно по вышается надежность работы узла, к ме того, упрощается его кон|гроль з счет ошибкообнаружиаающей способно ти Фибоначчиевой системы счисления и повышается быстродействие,так; 002828 как нет необходимости выполнять дополнительный такт сложения при наличии переноса в данную декаду из младшей. формула изобретения ). Устройство для сложения п-разрядных десятичных чисел, каждый i-й разряд которого (1.1,2..,п) содержит четыре двоичных сумматора и первый элемент ИЛИ, выходы суммы первого, второго, третьего и четвертого двоичных сумматоров данного разряда устройства подключены к выходам суммы данного разряда устройства соответственно, первый и второй входы второго, третьего и четвертого двоичных сумматоров данного разряда уст. ройстаа подключены к входам первого и второго операндов данного разряда устройства соответственно, выходы пе реносов второго и третьего двоичных сумматоров данного разряда устройства подключены к первому и второму входам первого элемента ИЛИ данного разряда устройства соответственно, выход переноса третьего двоичного сумматора данного разряда устройства подключен к третьему входу четвертого двоичного сумматора данного разряда устройства, выход переноса которого подключен к выходу переноса из данного 5-го разряда устройства в (+1)-й разряд устройства, отличающееся тем, что, с целью повышения быстродействия, в каждый i-й разряд устройства введены элемент И, второй элемент ИЛИ и блок формирования операндов первого двоичного сумматора и переносов в первый, второй и третий двоичные сумматоры, первый, второй, третий и четвертый входы которого подключены к входу переноса из (t-l)-ro разряда устройства в данный J- разряд устройства, к первому и второму операндам i-ro разряда устройства и к выходу переносов из второго и третьего двоичных сумматоров данного разряда устройства соответственно, а первый, второй, третий, четвертый и пятый выходы подк/ючены к первому, второму, третьему входам первого двоичного сумматора данного разряда устройства, к первому входу элемента И данного разряда устройства и к первому входу второго элемента ИЛИ данного разряда устройства соответственно, второй вход второго элемента ИЛИ подключен к выходу переноса второго двоичного сумматора данного раз ряда устройства, второй вход элемента И подключен к выходу переноса первого двоичного сумматора данного разряда устройства. 2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок формирования операндов первого двоичного сумматора и переносов в первый, второй и третий двоичные сумматоры содержит три элемента ИЛИ, шесть элементов И и четыре элемента НЕ, принем первый вход блока подключен к первым входам первого и второго элементов И, второй вход блока подключен к входу первого элемента НЕ, к первому входу первого элемента ИЛИ и ко второму входу первого элемента И, выход первого элемента НЕ подключен ко второму входу второго элемента И, выход которогб подключен ко второму входу первого элемента ИЛИ, выход которого подключен к первому выходу блока, второй и третий выходы которого подключены к выходам второго и третьего элементов ИЛИ соответственно, выход первого элемента И подключен к первым входам тре92,0 тьего и четвертого элементов И, третий в-ход блока подключен ко второму входу третьего элемента И, к первому входу второго элемента ИЛИ и ко входу второго элемента НЕ, выход которого подключен ко второму входу четвертого элемента И, выход которого подк/чочен ко второму входу второго элемента ИЛИ, выход третьего элемента И подключен к первым входам пятого и шестого элементов И, четвертый вход блока подключен ко второму входу пятого элемента И, к первому входу третьего элемента ИЛИ и ко входу третьего элемента НЕ, выход которого подключен ко второму входу шестого элемента И, выход которого подключен ко второму входу третьего элемента ИЛИ, выход четвертого элемента НЕ подк/точен к четвертому выходу блока, пятый выход которого подключен к выходу пятого элемента И и ко входу четвертого элемента НЕ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 488206, кл. G Об F 7/385. 19752.Авторское свидетельство СССР по заявке If 2807бЗЗ/18-2, кл. G 06 F 7/385, 1979 (прототип).

Авторы

Даты

1982-01-23—Публикация

1980-04-08—Подача