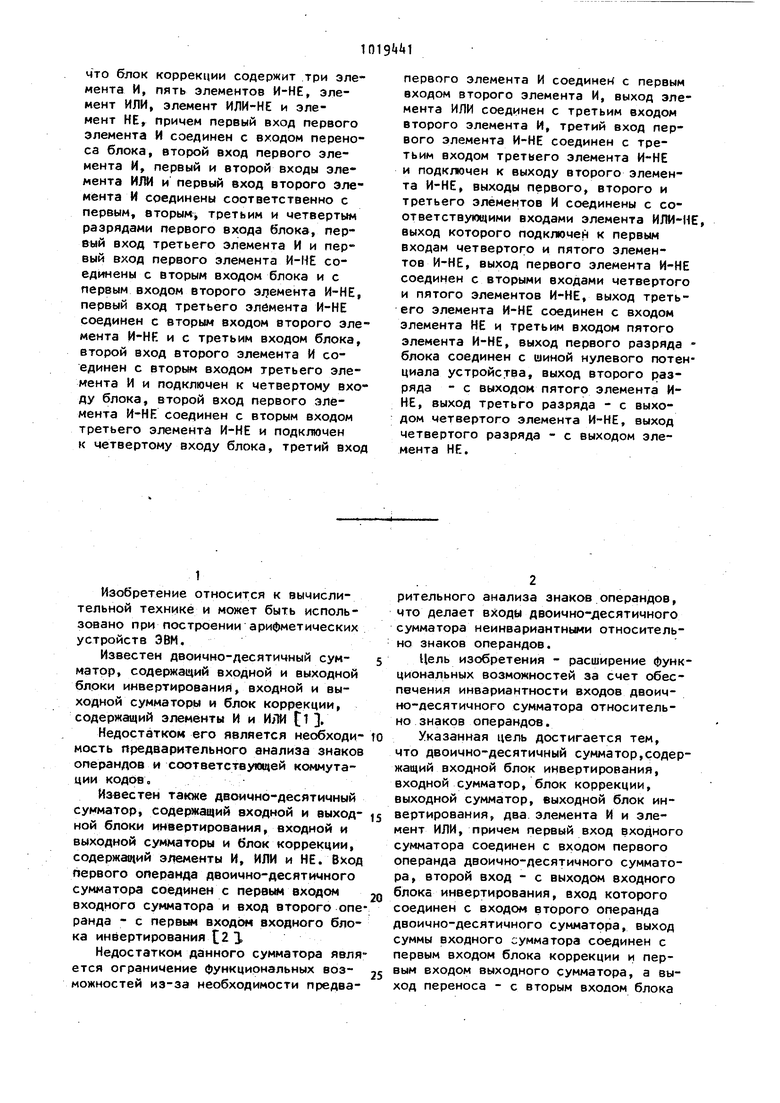

что блок коррекции содержит три элемента И, пять элементов И-НЕ, элемент ИЛИ, элемент ИЛИ-НЕ и элемент НЕ, причем первый вход первого элемента И соединен с входом переноса блока, второй вход первого элемента И, первый и второй входы элемента ИЛИ и первый вход второго элемента И соединены соответственно с первым, вторым третьим и четвертым разрядами первого входа блока, первый вход третьего элемента И и первый вход первого элемента И-НЕ соединены с вторым входом блока и с первым входом второго э емента И-НЕ, первый вход третьего элемента И-НЕ соединен с вторым входом второго элемента И-НЕ и с третьим входом блока, второй вход второго элемента И соединен с вторым входом третьего элемента И и подключен к четвертому входу блока, второй вход первого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ и подключен к четвертому входу блока, третий вход

первого элемента И соединен с первым входом второго элемента И, выход элемента ИЛИ соединен с третьим входом второго элемента И, третий вход первого элемента И-НЕ соединен с третьим входом третьего элемента И-НЕ и подключен к выходу второго элемента И-НЕ, выходы первого, второго и третьего элементов И соединены с соответствующими входами элемента ИЛИ-НЕ выход которого подключен к первым входам четвертого и пятого элементов И-НЕ, выход первого элемента И-НЕ соединен с вторыми входами четвертого и пятого элементов И-НЕ, выход третьего элемента И-НЕ соединен с входом элемента НЕ и третьим входом пятого элемента И-НЕ, выход первого разряда блока соединен с шиной нулевого потенциала устройства, выход второго разряда - с выходом пятого элемента ИНЕ, выход третьго разряда - с выходом четвертого элемента И-НЕ, выход четвертого разряда - с выходом элемента НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный сумматор | 1983 |

|

SU1208550A1 |

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Одноразрядный десятичный сумматор | 1975 |

|

SU690479A1 |

| УСТРОЙСТВО для СУММИРОВАНИЯ | 1973 |

|

SU393740A1 |

| Арифметико-логическое устройство | 1977 |

|

SU703808A1 |

| Одноразрядный десятичный сумматор в коде "5421 | 1988 |

|

SU1575171A1 |

| Устройство для суммирования и вы-чиТАНия дВОичНО-дЕСяТичНыХ КОдОВ | 1978 |

|

SU813415A1 |

| Устройство для сложения и вычитания | 1980 |

|

SU922730A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств ЭВМ.

Известен двоично-десятичный сумматор, содержащий входной и выходной блоки инвертирования, входной и выходной сумматоры и блок коррекции, содержащий элементы И и ИЛИ fl },

Недостатком его является необходимость предварительного анализа знаков операндов и соответствующей коммутации кодов.

Известен также двоично-десятичный сумматор, содержащий входной и выходной блоки инвертирования, входной и выходной сумматоры и блок коррекции, содержащий элементы И, ИЛИ и НЕ. Вход первого операнда двоично-десятичного сумматора соединен с первым входом входного сумматора и вход второго операнда - с первым входом входного блока инвертирования 2 3

Недостатком данного сумматора является ограничение функциональных возможностей из-за необходимости предварительного анализа знаков операндов, что делает входы двоично-десятичного сумматора неинвариантньми относительно знаков операндов.

Цель изобретения - расширение функциональных возможностей за счет обеспечения инвариантности входов двоично-десятичного сумматора относительно знаков операндов.

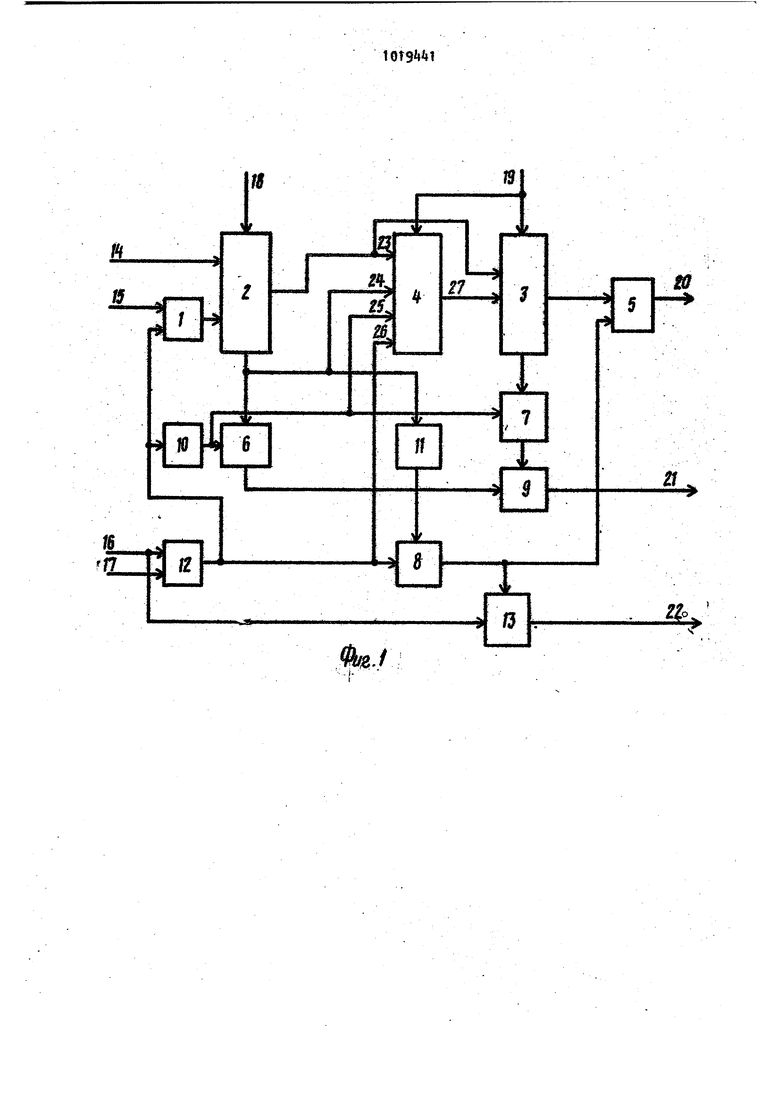

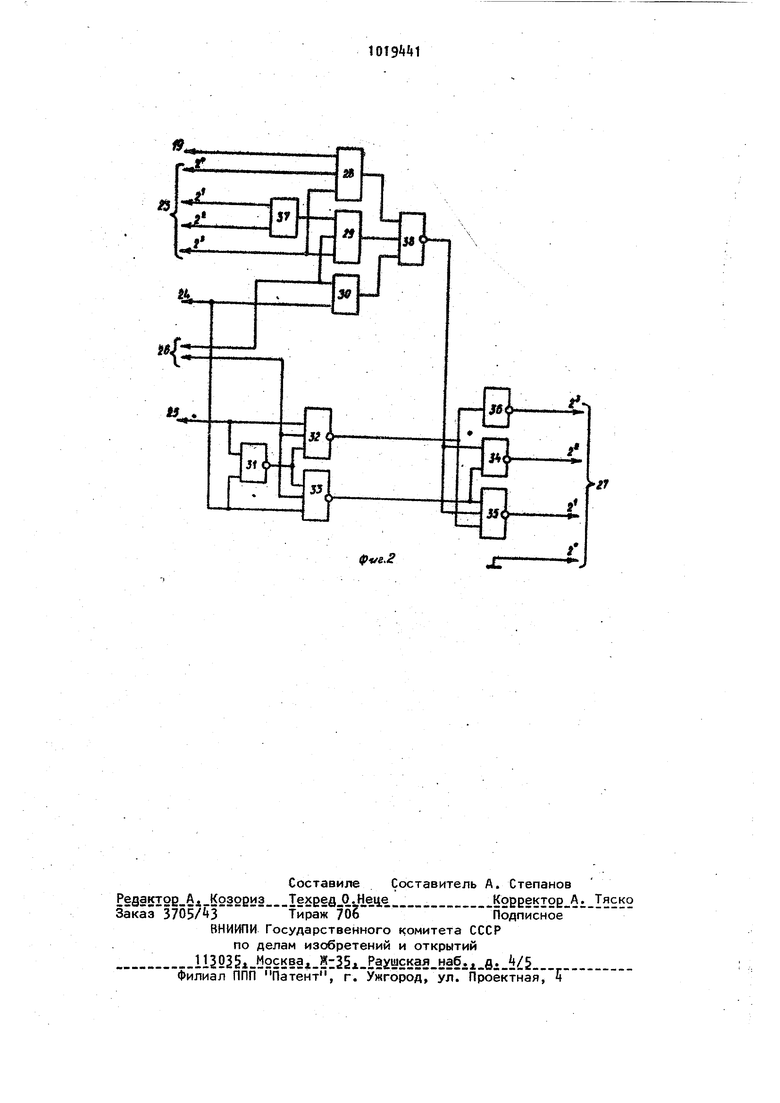

Указанная цель достигается тем, что двоично-десятичный сумматор,содержащий входной блок инвертирования, входной сумматор, блок коррекции, выходной сумматор, выходной блок инвертирования, два элемента И и элемент ИЛИ, причем первый вход входного сумматора соединен с входом первого операнда двоично-десятичного сумматора, второй вход - с выходом входного блока инвертирования, вход которого соединен с входом второго операнда двоично-десятичного сумматора, выход суммы входного сумматора соединен с первым входом блока коррекции и первым входом выходного сумматора, а выход переноса - с вторым входом блока коррекции и первым входом первого эле мента И, второй вход которого соединен с первым входом второго элемента И, второй вход которого подключен к выходу переноса выходного сумматора, выход блока коррекции подключен к второму входу выходного . сумматора, выход которого соединен с входом выходного блока инзертиро а ния, выход которого соединен с выходом суммы двоично-десятичного сумматора, выходы первого и второго элементов И соединены с соответствующим входами элемента ИЛИ, выход которого соединен с выходом переполнения двоично-десятичного сумматора, вход пере носа блока коррекции соединен с входом переноса выходного сумматора, содержит два элемента НЕ, два сумматора по модулю два и третий элемент И, причем входы первого суммато ра по модулю два соединены с соответ ствующими входами знаков операндов двоично-десятичного сумматора, первый вход второго сумматора по модулю два соединен с первым входом первого сум атора по модулю два, выход которого подкгючен к управляющему входу входного блока инвертирования, вх ду пер&ого, элемента , третьему вхо ду блока коррекции, к первому входу третьего элемента И, выход первого элемента НЕ соединен с вторым входом первого элемента И и с четвертым вхо дом блока коррекции, выход переноса входного сумматора подключен к входу второго элемента НЕ, выход которого соединен с вторым входом третьего элемента И, выход которого подключен к второму входу второго сумматора по модута) два и к управляющему входу выходного блока инвертирования, выход второго сумматора по модулю два соединен с выходом знака двоич«о-деcяtичнoгo сумматора.. Блок коррекции содержит три элемента И, пять элемеитов Й-НЕ, элемент ИЛИ, элемент ИЛИ-НЕ и элемент НЕ причем первый вход первого элемента И соединен с входом переноса блока, вто рой -вход перввго элемента И, первый и второй входы элемента ИЛИ и первый вход второго элемента И соединены соответственно с первым, вторым, третьим и четвертым разрядами первого входа блока, первый вход третьего эле мента И и первый вход первого элемента И-НЕ соединены с вторьм входом блока и с первым входом второго элемента И-НЕ, первый вход третьего элемента И-НЕ соединен с вторым входом второго элемента И-НЕ и с третьим входом блока, второй вход второго элемента И соединен с вторым входом третьего элемента И и подключен к четвертому входу блока, второй вход первого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ и подключен к четвертому входу блока, третий вход первого элемента И соединен с первым входом второго элемента И, выход элемента ИЛИ соединен с третьим входом второго элемента И, третий вход первого элемента И-НЕ соединен с третьим входом третьего элемента И-НЕ и подключен к выходу второго элемента И-НЕ, выходы первого, . второго и третьего элементов И соединены с соответствующими входами элемента ИЛИ-НЕ, выход которого подключен к первым входам четвертого и пятого элементов И-НЕ, выход первого элемента И-НЕ соединен с вторыми входами четвертого и пятого элементов И-НЕ, выход третьего элемента И-НЕ соединен с входом элемента НЕ и третьим входом пятого элемента И-НЕ, выход первого разряда блока соединен с шиной нулевого потенциала устройства, выход второго разряда с выходом пятого элемента И-НЕ, выход третьего разряда - с выходом четвертого элемента И-НЕ выход четвертого разряда - с выходом элемента НЕ. На фиг. 1 показана структурная схема предлагаемого двоично-десятичного сумматора; на фиг. 2 - функциональная схема блока коррекции. Двоично-десятичный сумматор содержит входной блок 1 инвертирования, входной сумматор 2, выходной сумматор 3, блок коррекции, выходной блок 5 инвертирования, элементы И 6-8, ИЛИ 9 НЕ 10 и 11, а также су| «аторы 12 и 13 по модугйо два. Двоично-десятичный сумматор имеет входы 1 и 15 соответственно первого и второго операндов, входы 16 и 17 знаков первого и второго операндов. Входной и выходной сумматоръ имеют также входы 18 и 19 переноса для подключения к пр едла- гаемому двоично-десятичному сумматору других для получения многоразрядного устройства. Двоично-десятичный сумматор имеет выходы 20 - суммы, 21 переполнения и 22 - знака суммы.

Блок коррекции имеет входы , выход 27 и еодержит элементы И , И-НЕ 31-35, не 36, ИЛИ 37 и ИЛИ-НЕ 38 Двоично-десятичный сумматор работа ет следующим образом.

При одинаковых знаках операндов А и В, где А - первый операнд, В - второй операнд, суммирование производится в прямых кодах В этом случае выходной сигнал сумматора 12 по модулю два равен О и входной блок 1 инвер; тирования кодов обеспечивает передачу прямого кода на вход входного сумматора 2. Выходной сигнал элемента ИВ также равен О.

Зна,к, суммы аырабатывЬется сумматором 13 по модулю два. В случае положительных знаков операндов (положительному знаку соответствует нулевой логический уровень :) на выходе суммато ра 13 по модулю два будет О, что соответствует положительному знаку суммы, В случае отрицательных знаков операндов (отрищательному знаку соответствует единичный логический уровень )кэ выходе сумматора 13 по модулю два будет 1, что с(ютветствует отрицательному знаку суммы. Если операнды имеют разные знаки, то выходной сигнал сумматора 12 по модулю два равен 1 и тогда олеранд В ин вертируется входным блоком 1 инвертирования. Ксли отрицательным операндом является операнд В, то ) инвертирование справедливо. Если отрицателен операнд А, то такое инвертирование соответствует умножению обоих операндоа на 1. Знак суммы также зависит и от соотношения величин операндов. Если из большего числа вычитать меньшее, то результат получается в прямом коде. Если из меньшего числа вычитать большее,то результат получается в инверсном коде.

Признаком получения суммы в прямом коде является наличие сигнала nepeHoса в старшей декаде устройства соответственно его отсутствие является признаком получения суммы в инвертированном коде. Элемент И 8 выделяет условие при выполнении вычитания, т.е выход сумматора 1 по модуло два равен 1 и отсутствует равен О сиг йал переноса из старшей декады входно го сумматора, и это условие соответствует получению суммы в инверсном коде. Выходной сигнал элемента И 8 управляет выходным блоком 5 инвертирования кодов, Hj если возникает указанное условие, результат суммирования инвертируется

Если операнд А положителен и больше, чем операнд В, то сумма получается в прямом коде, выходной сигнал элемента И 8 равен О, выходной блок 5 инвертирования кодов пропускает прямой код, а выходной сигнал сумматора 13 по моду/ з два равен О, что соответствует положительному знаку суммы.

Если операнд А положителен и меньше, чем операнд В, то сумма получается в инверсном коде, выходнойссигнал элемента И В равен 1, выходной блок 5 инвертирования кодов инвертирует код суммы, а выходной сигнал с сумматора 13 по модулю два равен 1, что соответствует отрицательному знаку суммы.

Если операнд А отрицателен и больше, чем операнд В, то сумма получается в прямом коде, выходной сигнал элемента И 8 равен О, выходной блок 5 инвертирования кодов пропускает прямой код, а выходной сигнал сумматора 13 по модулю два равен 1, v что соответствует отрицательному знаку суммы.

Если операнд А отрицателен и меньше, чем операнд В, то сумма получается в инверсном коде, выходной сигнал элемента И 8 равен 1, выходной блок 5 инбертирования кодов инвертирует код сукмы, а выходной .сигнал сумматора 13 по модулю два равен О, что соответствует положительному знаку суммы.

Таким образом, введение в состав двоично-десятичного сумматора элементов И, НЕ и сумматоров по модулю два позволяет расширить функциональные возможности устройства для суммирования двоично-десятичных кодов за счет того, что входы устройства инвариантны любым сочетаниям знаков операндов. При этой отпадает необходимость перемены операндов местами, а, следовательно, и в дополнительной аппаратуре для коммутации кодов, которая весьма громоздка. Таким образом, получено устройство чисто комбинационного типа, обладающее высоким быстродействием, которое ограничивается только задержками логических элементов.

Йй./

Авторы

Даты

1983-05-23—Публикация

1981-10-20—Подача