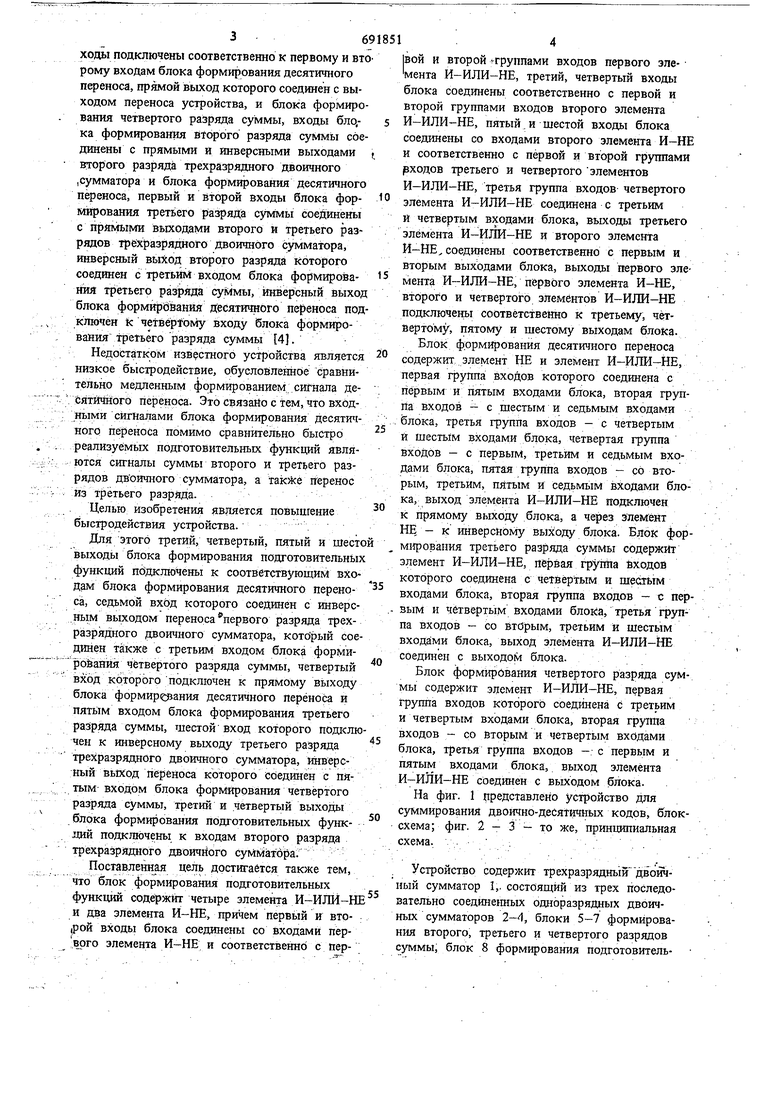

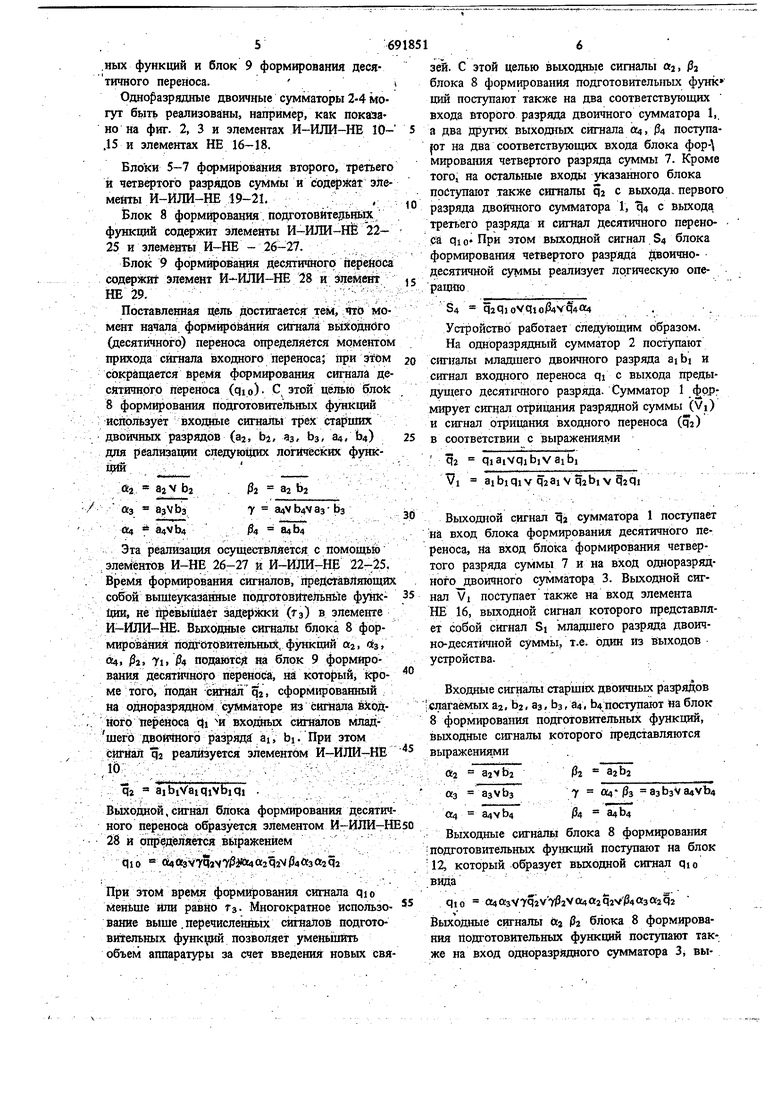

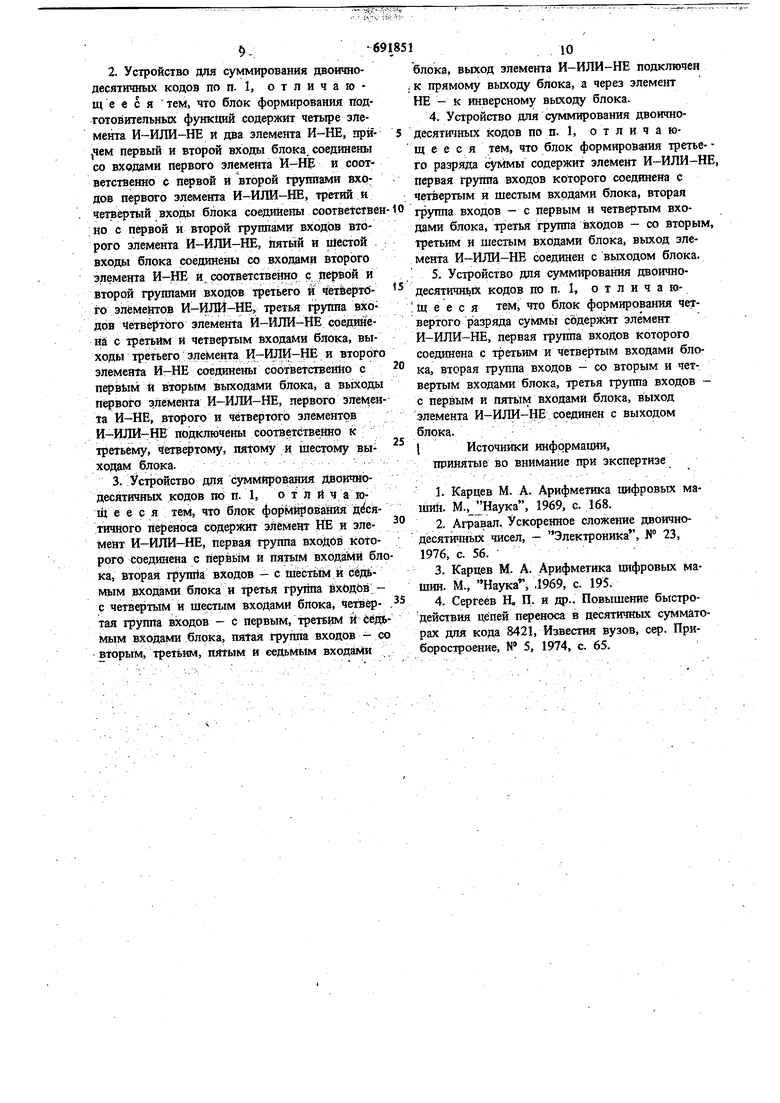

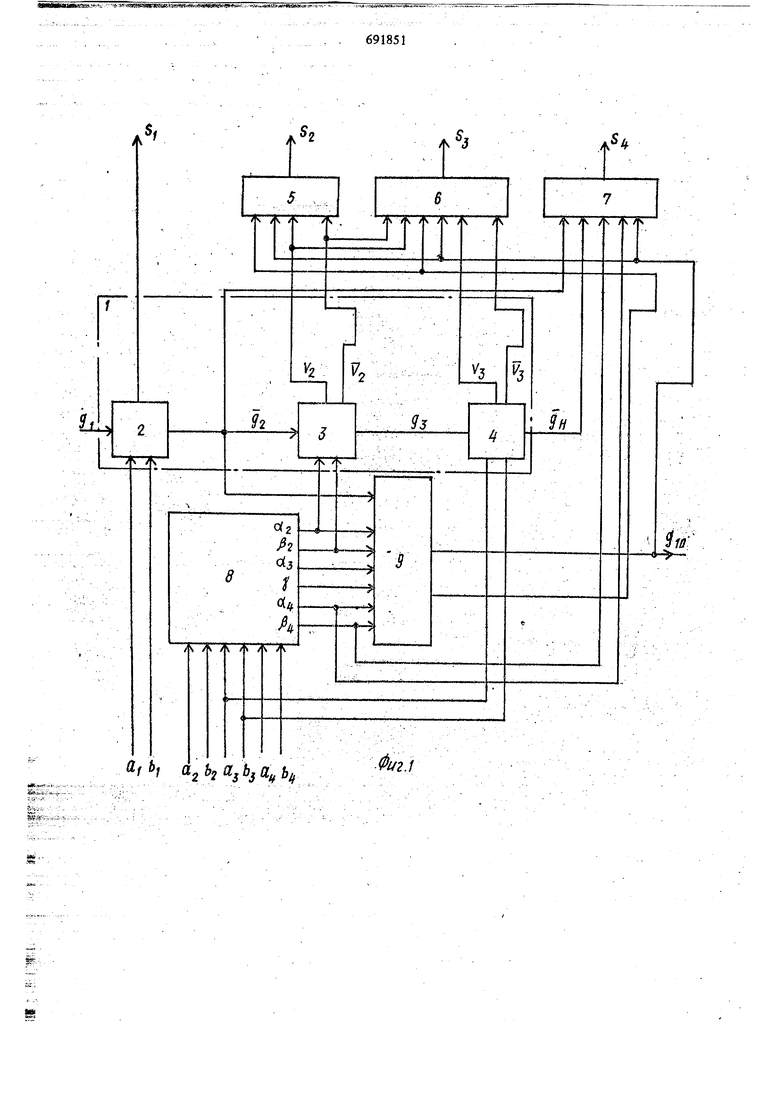

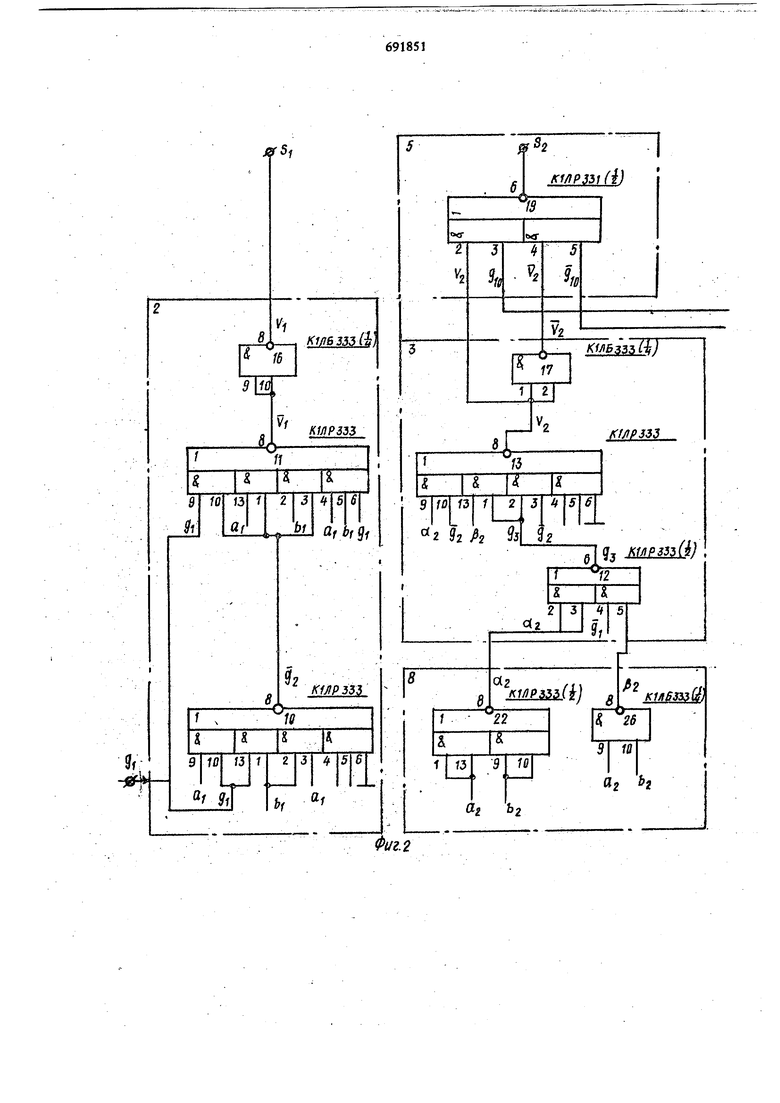

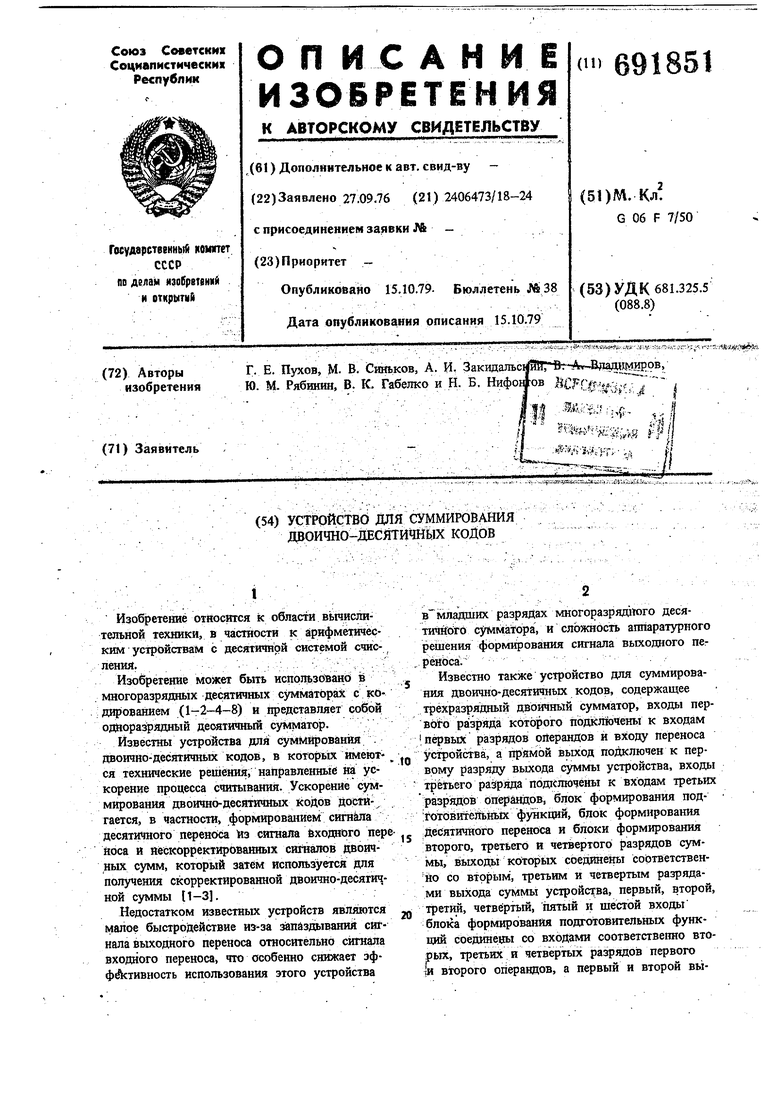

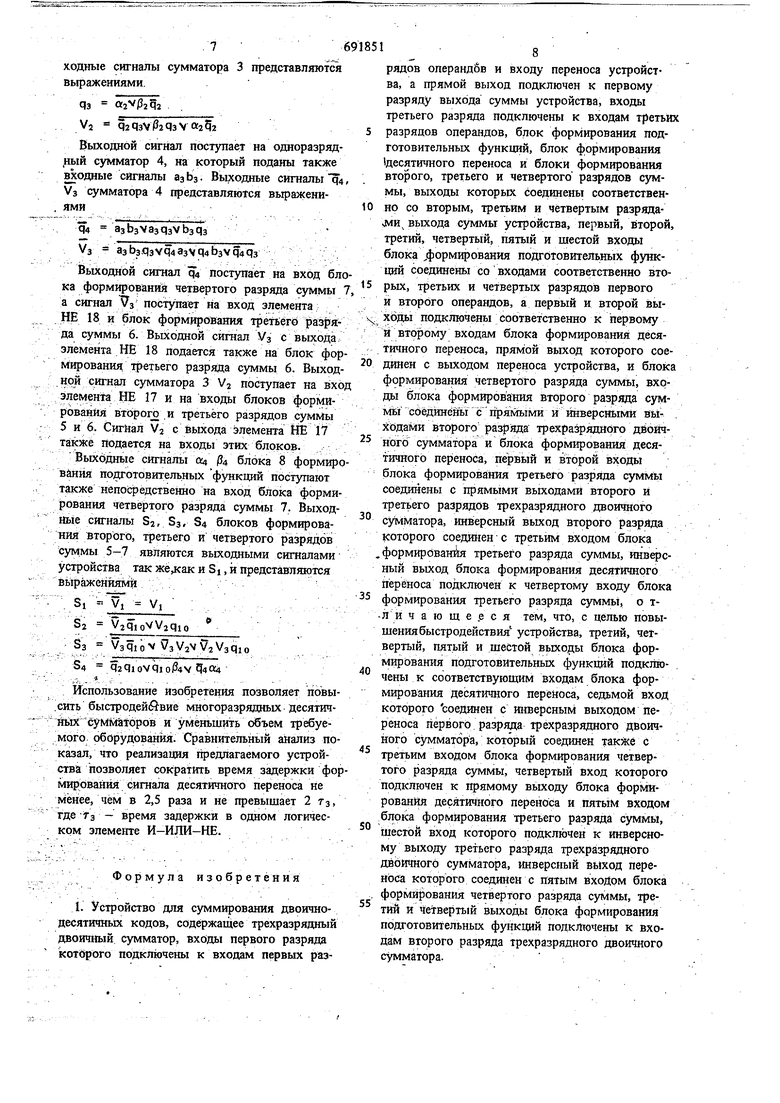

, . Изобретение относится к области вшислительной техники, в частности к арифметическим устройствам с десятичной системой счисдеНИЯ.-.... ,; . .. , ;,; .-Изобретение может быть нспрпьзбванЬ и . многоразрядных десятичных сумматорах с кодированием (1-2-4-8) и 11редставляет собой одаоразрядный десятичный суммато|р. Известны устройства для суммирования двоично-десятичньис кодов, в которьсс имеются технические решения, направленные на ускорение процесса считывания. Ускорение суммирования двоично-десятичных кодов достигается, в частности, формированием сигнала десятичного перено ;а из сигнала бходаого пере носа и нескорректированных сигна юв даоичных сумм, который затем используется для получения скорректированной двоично-десятичной суммы 1-3. Недостатком известных устройств являются малое быстродействие Опаздывания сигнала выходного переноса относительно сигнала входного переноса, что особенно снижает эффdkтивнocть использования этого устройства В младших разрядах многоразрядного десятнчйЬГЬ сумматора, и сложность аппаратзфного решения формирования сигнала выход11ого пег реноса. Известно также устройство для суммирования двоично-десятичных кодов, содержащее трехразрядный двоичный сумматор, входы перBoto разряда которого подключены к входам первых; разрядов операндов и входу переноса Уcipoйcтвa, а прямой вьгход подключен к первому разряду выхода суммы устройства, входы третьего разряда подключены к входам третьих разрядов операндов, блок формирования подirotoBHtejitbHbtx функций, блок формирования Десятичного переноса и блоки формирования второго, третьего и четвертого разрядов суммы, выходы котор ых соединены соьтветственНо Со вторым, третьим к четвертым разрядами выхода суммы устройства, первый, второй, третий, четвёртый, пятый и шестой входы блока формирования подготобительных функций соединены со входами соответственно вторых, третьих и четвертых разрядов первого чи второго операндов, а первый и второй вь136ходы подключены соответственно к первому и втО рому входам блока формирования десятичного переноса, прямой выход которого соединен с выходом переноса устройства, и блока формиро вания четвертого разряда суммы, входы бло,ка формирования второго разряда суммьг сое динены с прямыми и инверсными выходами второго разряда трехразрядного двоичного Iсумматора и блока формирования десятичного переноса, первый и второй входы блока формирования третьего разряда суммы соединены с прямыми выходами второго и третьего разрядов трёхразрядного двоичного сумматора, инверсный выход второго разряда которого соединен с третьим входом блока формирования третьего разряда суМмы, инверсный выход блока формирейания десятичного переноса под ключен к четвертому входу блока формгфования третьего разряда суммы 4). Недостатком известного устройства является низкое бь1с1родействие, обусловленное с равнитепьно медленным формированием сигнала деV сятйчного переноса. Это связаМо с Тем, что входными сигналами блока формирования десятичного переноса помимо сравнительно быстро реализуемых подготовительных функций являются сигналы суммы второго и третьего разрядов двоичного сумматора, а такйсе Перенос из третьего разряда. . Целью изобретения является повышение быстродействия устройства. Для этого третий, четвертый, пятый и шест выходы блока формирования подготовитеЛьнь1Х функций подключены к соотйетствующим входам блока формирования десятичного переноса, седьмой вход которого соединен с инверс.нь1М выходом переносапервого разряда трехразрядного двоичного сумматора, котсррый сое динен тйкже с третьим входом блока формирования четвертого разряда суммы, четвертый вход которого подключен к прямому выходу блока формирелания десятичного переноса и пятьтм входом блока формирования третьего разряда суммы, шестой вход которого подклю чен к инверсному выходу третьего разряда трехразрядного двоичного сумматора, инверсный выход переноса которого соединен с пя. тым входом блока формирования четвертого разряда суммы, третий и четвертый выходы блока формирования подготовительных функдий подкл1очены к входам второго разряда трехразрядного двоичного сумматора. Поставленная цель достигается также тем, что блок формирования подготовительных функций содержит четыре элемента И-ИЛИ-Н и два элемента И-НЕ, причем первь1Й и вто|рой входы блока соединены со входами перврго элемента И-НЕ и соответственно с первой И второй группами входов первого элемента И-ИЛИ-НЕ, третий, четвертый входы блока соединены соответственно с первой и второй группами входов второго элемента И-ИЛИ-НБ, пятый. и шестой входы блока соединены со входами второго элемента И-НЕ и соответственно с первой и второй группами рходов третьего и четвертого элементов И-ИЛИ-НЕ, третья группа входов четвертого элемента И-ИЛИ-НЕ соединена с третьим и четвертым входами блока, выходы третьего элемента И-ИЛИ-НЕ и второго элемента И-НЕ, соединены соответственно с первым и вторым выходами блока, выходы первого элемента И-ИЛИ-НЕ, первого элемента И-НЕ, второго и четвертого элементов И-ИЛИ-НЕ подключены соответственно к третьему, четвертому, пятому и шестому выходам блока. Блок формирования десятичного переноса содержит элемент НЕ и элемент И-ИЛИ-НЕ, первая группа входов которого соединена с первым и пятым входами блока, вторая группа входов - с шестым и седьмым входами ёлока, третья группа входов - с четвертым И шестьтм входами блока, четвертая группа входов - с первым, третьим и седьмым входами блока, пятая группа входов - со вторым, третьим, питым и седьмым входами блока, выход элемента И-ИЛИ-НЕ подключен к прямому выходу блока, а через Элемент НЕ, - к инверсному выходу блока. Блок форМ1фования третьего разряда суммы содержит элемент И-ИЛИ-НЕ, первая группа входов которого соединена с четвёртым и шестым входами блока, вторая группа входов - с первым и четвертым входами блока, третья группа входов - со Вторым, третьим и шестым входами блока, выход элемента И-ИЛИ-НЕ соединен с выходом блока. Блок формирования четвертого разряда суммы содержит элемент И-ИЛИ-НЕ, первая группа входов которого соединена с третьим и четвертым входами блока, вторая группа входов - со Вторым и четвертым входами блока, третья группа входов - с первым и пятым входами блока, выход элемента И-ИЛИ-НЕ соединен с выходом блока. На фиг. 1 представлено устройство для суммирования двоично-десятичных кодов, блоксхема; фиг. 2 - 3 - то же, принципиальная схема. ... . .... Устройство содержит трехразрядньшдвойчный сумматор 1,. состоящий из трех последовательно соединега1ых одноразрядных двоичных сумматоров 2-1, блоки 5-7 формирования второго, третьего и четвертого разрядов суммы, блок 8 формирования подготовитель56 .ных функций и блок 9 формирования десятичного переноса. Одноразрядные двоичные сумматоры 2-4 могут быть реализованы, например, как показа но на фиг. 2, 3 и элементах И-ИЛИ-НЕ 10.15 и элементах НЕ 16-18. Блоки 5-7 формирования второго, третьего и четвертого разрядов суммы и содержат элементы И-ЙЛИ-НЕ 19-21,Г , Ъпок В формирования. подгото8Йте 1ь1П.к функций содержит элементы И-ИЛИ-НЁ 2225 и элементы И-НЕ - 26-27. Блок 9 формирования десятиодого перейоса содержи элемент И-ИЛИ-НЕ 28 и йдейейт НЕ29. ;; V ;; - .;: ;ч :,:: v:-: Поставленная цель достигается тем, что момент начала формирования сигнала вьйоднбго (десятичного) переноса определяется моментом прихода сигаала входного переноса; при этим сокращается время формирования сигнала десятичнрго переноса (qio)- С этой целью uiofc 8 формирования подготовительных функвдй использует входные сигналы трех старших двоичных разрядов (эа, bj, 33. Ьз, 34, Ь4) для р еализации следующих логических ф)гшс: 1ЫЙ ,,.-,,. «2 aavb2 . PI 32 bj Оз a4Vb4Va3-Ьз 04 a4Vb4 a4b4 Эта реализация осуществляется с помощью ,элемштЬв И-НЕ 26-27 и И-ИЛИ-НЕ . Время формирования сигналов, йредетавйяющих собой вышеуказавйые подготовйТейьнъте фуйк1щи, не npeiBbiuiaeT задержки (Тз) в элементе И-ИЛИ-НЕ. Выходные сигналы блока 8 формирования пойготовитёльных, функщй «21 «3. «4. 02. Ть J подаются на блок 9 формирования десятичного переноса, на которьтй, кроме того, подан сигнал q2, сформированный на одноразрядном/с маторе из сигнала йсодного переноса cji и входньи сигналов младшего ДВОИЧНОГО разряда ai, bi. При этом сигнал qa реализуется элементам И-ИЛИ-НЕ ib;: : ..-... - : /.--. - .. , : q2 aibiVaiqivbiqi . Вь1Хбдной, сигшш бдока формирования десятич ного переноси образуется элементом И-ИЛИ-Н 28 и определяется выражением qio « oi4a3V7q2V7 ite4a2q2vfl4tt3a2q2 При этом время формирования сигнала qio меньше или равно Тз- Многократное использованне выше. перечисленных сигналов подготовительных функций позволяет уменьшить объем аппаратуры за счет введения новых свя зей. С этой целью выходньш сигналы oj, jSj блока 8 формирования подготовительных функ ПИЙ поступают также на два соответствующих входа второго разряда двоичного сумматора 1,. а два других выходньк сигнала о,, поступарт на два соответствующих входа блока фор- MHpoBaifflH четвертого разряда суммы 7. Кроме того, на остальные входы указанного блока поступают также сигналы q с выхода- первого разряда двоичного сумматора 1, q4 с выхода, третьего разряда и сигнал десятичного переноса qi о При этом выходной сигнал 84 блока формирования четвертого разряда двоичнодесятичной суммы реализует логическую операщсоq2qjoVqio/34V 4a4. Устройство работает следующим образом. На одноразрядный сумматор 2 поступают сигналы младшего двоичного разряда aibj и сигнал входного переноса qi с выхода предыдущего десятичного разряда. Сумматор 1 фрр-- мирует сигчал отрицания разрядной суммы (Vi) и сигнал отрицания входного переноса (qj) в соответствии с выражениями qiaivqjbivaib, aibjqiv qaai V qabj V 2qi Выходной сигнал 2 сумматора 1 поступает на вход блока формирования десятичного переноса. На вход блока формирования четвертого разряда суммы 7 и на вход одноразрядного двоичного сумматора 3. Выходной сигнал Vi поступает также на вход элемента НЕ 16, выходной сигнал которого представляет собой сигнал Si младшего разряда двоично-десятичной суммы, т.е. один из выходов устройства. Входные сигналы старших двоичных разрядов слагаемых а2, Ь2, зз, Ьз, 34, Ь4;поступают На блок 8 формирования подготовительных функций, выходные сигналы которого представляются вьфажениями 7 Зз ЬзУ 34Vb4 /34 34b4 Выходные сигналь блока 8 формирования подготовительных функций поступают на блок 12, который образует выходной сигнал qio вида qio «40:3 V7q2v)l32V 04 cit2q2V(34 «30252 Выходные сигналы «2 /32 блока 8 формирования подготовительных функций поступают также на вход одноразрядного сумматора 3, выходные сигналы сумматора 3 представляются вьфажениями. ЯЭ . . Vj q2 3yhq3 Выходной сигнал поступает на одноразрядный сумматор 4, на который поданы также входные сигналы ЭзЬз. Выходные сигналы q УЗ сумматора 4 представляются вьфажениямиqi a3b3Va3q3Vb3q3 УЗ a3b3,q3Vq4a3Vq4b3vq4q3Л Выходной сигнал q4 поступает на вход бло ка формирования четвертого разряда суммы а сигнал з поступает на вход элемента НЕ 18 и блок формирования третьего разряда суммы 6. Выходной сигнал УЗ с выхоДа. элемента.НЕ 18 подается также на блок фор мирования третьего разряда суммы 6. Выходной сигнал сумматора 3 У поступает на вхо элемента НЕ 17 и на входы блоков формирования втЬрого и третьего разрядов суммы 5 и 6. Сигнал Уг с выхода элемента НЕ 17 также подается на входы этих блоков. Выхбдные сигналы сх4 fo блока 8 формиро вания подготовительных функдий поступают также непофедственно на вход блока формирования четвёртого разряда суммы 7. ВыходHbie сигналы 82,83, 84 блоков формирования второго, третьего и четвертого разрядов суглмы 5-7 являются выходными сигналами устройства так и 8i, и представляются вьфажениями У, У S2 y qioVyaqiQ Зз V3qiov73V2VV2y3qio 84 - q2qiovqiol34V 404 ;,,.... . .;, .,..., использование изобретения позволяет повы . сить быстродеййвие многоразрядных десятичйьк сумматоров и уменьшить объем требуемого оборудования. Сравнительный анализ по казал, что реализация предлагаемого устройства позволяет сократить время задержки фо мирования сигнала десятичного переноса не менее, чем в 2,5 раза и не превышает 2 тз, где Тз - время задержки в одном логическом элементе И-ИЛИ-НЕ. Формула изобретения 1. Устройство для суммирования двоичнодесятичных кодов, содержащее трехразрядный двоичный сумматор, входы первого разряда которого подключены к входам первых разрядов операндбв и входу переноса устройства, а прямой выход подключен к первому разряду выхода суммы устройства, входы третьего разряда подключены к входам третьих разрядов операндов, блок формирования подготовительных функций, блок формирования (десятичного переноса и блоки формирования второго, третьего и четвертого разрядов суммы, выходы которых соедняены соответственно со вторым, третьим и четвертым разрядаии выхода суммы устройства, первый, второй, третий, четвертый, пятый и шестой входы блока Jфopмиpoвaния подготовительных функций соединены со входами соответственно вторых, третьих и четвертых разрядов первого и второго операндов, а первый и второй выходы подключены соответственно к первому и второму входам блока формирования десятичного переноса, прямой выход которого соединен с выходом переноса устройства, и блока формирования четвертого разряда суммы, входы блока формирования второго разряда сумMfei сбёдИнёШ с прямъши и йнверсньгМИ вы- . ходами второгоразряда трехразрядного дйойчного сумматора и блока формирования десятичного переноса, первый и второй входы блока формирования третьего разряда суммы соединены с прямыми выходами второго И третьего разрядов трехразрядного двоичного сумматора, инверсный выход второго разряда которого соединен с третьим входом блока формирования третьего разряда суммы, инверсный выход блока формирования десятичного переноса подключен к четвертому входу блока формирования третьего разряда суммьг, о т-л и ч а ю щ е е с я тем, что, с целью повышениябыстродействия устройства, третий, четвертый, пятый и шестой вькоды блока формир1эвания подготовительных функций подключены к соответствующим входам блока формирования десятичного переноса, седьмой вход которого соединен с инверсным выходом переноса первого. разряда трехразрядного двоичного сумматора, который соединен также с третьим входом блока формирования четвертого разряда суммы, четвертый вход которого подключен к прямому выходу блока формирования десятичного переноса и пятым входом блока формирования третьего разряда суммы, шестой вход которого подключен к инверсному выходу третьего разряда трехразрядного двоичного сумматора, инверсный выход переноса которого соединен с пятым входом блока формирования четвертого разряда суммы, третий и четвертый выходы блока формирования подготовительных функций подключены к входам второго разряда трехразрядного двоичного сумматора. 2. Устройство для суммирования двоичнодесятичных кодов по п. 1, отличающееся тем, что блок формирования подготовительньк функ1шй содержит четыре элемента И ИЛИ-ЙЕ и два элемента И-НЕ, прй,чем первый и второй входы блока, соединены со входами первого элемента И-НЕ и соответственно с первой и второй группами входов первого элемента И-ИЛИ-НЕ, третий и четвертый входы блока соедийепы соответствен но с первой и второй груПпами входов второго элемента И-ИДИ-НЕ, пятый и п1ёстой . входы блока соединены со входами второго элемента И-НЕ и, хзответственно с первой и второй группами входов третьего И четвертого элементов И-ИЛИ-НЕ, третья группа входов 4eTBepiTbro элемен1а Й-ИЛИ-НЕ соединена с третьим и четвертым входами блока, выходы третьего элемента И-ИЛИ-НЕ и второго элемента И-НЕ соединены соответственйо с nepBbiM и вторым выходами блока, а выходы первого элемента И-ИЛИ-НЕ, первого элеЦен Та И-НЕ, второго и четвертого элементов И-ИЛИ-НЕ подключены соответствейно к третьему, четвертому, пятому и щестому выходам блока. 3. Устройство для суммирования двоичнодесетичных кодов по п. 1, о т л и ч а юlil е е с я тем, что блок форлйфованйя д сятичного переноса содержит элемент НЕ и элемент И-ИЛИ-НЕ, первая группа входов которого соединена с первьтм и пятым входами бл ка, бторая rpjonia входов - с mecTiiivt и сёдймым входами блока и третья группа бходьв с четвертым и шестым входами блока, Четтвертая ipynna входов - с первым, третьим и йёдь мым входами блока, пятая группа входов - с вторым, третьим, и седьмым входами блока, выход элемента И-ИЛИ-НЕ подключен к прямому выходу блока, а через элемент НЕ - к инверсному выходу блока. 4. Устройство для суммирования двоичнодесятичных кодов по п. 1, о т л и ч а ющ е ее я тем, что блок формировали третье-го разряда суйШЫ содержит элемент И-ИЛИ-НЕ, первая группа входов которого соединена с четвертым и шестым входами блока, вторая группа входов - с первым и четвертым входами блока, третья группа входов - со вторым, третьим и шестым вхбдами блока, выход элемента И-ИЛИ-НЕ соединен с выходом блока. 5. Устройство для суммирования двоичнодесятичньк кодов по п. 1, о т л и ч а ющ е е с я тем что блок формирования четвертого разряда суммь содержит элемент И-ИЛИ-НЕ, первая группа входов которого соединена с третьим и четвертым входами блока, вторая группа входов - со вторым и четвертым входами блока, третья группа входов с первым и пятым входами блока, выход элемента И-ИЛИ-НЕ. соединен с выходом блока. 1Источники информации, принятые во внимание при экспертизе 1.Карцев М. А. Арифметика цифровых маший. М., Наука, 1969, с. 168. 2.Агравал. Ускоренное сложение двоичнодесятичных чисел, - Электроника, № 23, 1976, с. 56. 3.Карцев М. А. Арифметика цифровых машин. М., Наука , .1969, с. 195. 4.Сергеев Н. П. и др.. Повышение быстродействия цепей переноса в десятичных сумматорах для кода 8421, Известия вузов, сер. Приборостроение, N 5, 1974, с. 65.

-

лл

St

кг/гбзззШ

КЛРЗЗЗ

1

&S2

/ffflp33} fi)

V

ki

J

- .

rrf

V2

K1JIE33Z (i)

Л

8

E

т.

J

2

кглрззз()

О

| название | год | авторы | номер документа |

|---|---|---|---|

| "Одноразрядный десятичный сумматор в коде "5421" | 1988 |

|

SU1658143A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Одноразрядный десятичный сумматор в коде "5421 | 1988 |

|

SU1575171A1 |

| Сумматор-вычитатель | 1981 |

|

SU993254A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Преобразователь двоичного кодаВ дЕСяТичНый | 1979 |

|

SU830371A1 |

Авторы

Даты

1979-10-15—Публикация

1976-09-27—Подача