Изобретение относится к автоматика и вычислительной технике, в частности к устройствам для преобразования частоты в код. Известны преобразователи частоты в код, содержащие приемники информации, вычислитель частот, блок синхронизации и реверсивный счетчик, подклю ченные к блоку управления 1П Однако в них невозможно преобразование сигналов со случайной фазой. Наиболее близким по технической сущности к изобретению является преобразователь, содержащий приемники информации, вычитатель частот, блок синхронизации, реверсивный счетчик, сумматор и интегратор, подключенные к блоку управления 2 .. Недостатком-этого преобразователя является то, что его нельзя использо вать для преобразования в код частоты сигнала со случайной фазой, так .как в нем вычитатель частот непосредственно связан со входом-реверсив ного счетчика приращения частоты. При этом скачок входного сигнала, больший половины периода, приводит к нарушению соответствия между входным сигналом и его кодом в счетчике, поскольку вычитатель частот, являющийся детектором относительных фазовых сдвигов входного и восстановленного из кода сигналов ,при указанных связях между элементами схемы дает информацию лишь о знаке разности фаз указанных сигналов, по которому определяются еда1ничные приращения частоты.Таким образом,реакция известного преобразователя на скачок фазы входного сигнала выражается в появлении переходного процесса, необходимого для восстановления соответствия между входньм сигналом и его кодом, т.е. в течение переходного процесса код оказьшается недостоверным. Целью изобретения является расширение функциональных возможностей устройства при одновременном сокра39004474

щении времени преобразования и расти-10. Преобразователь П код - частота

рения диапазона преобразуемых частот.включен между выходом интегратора 10

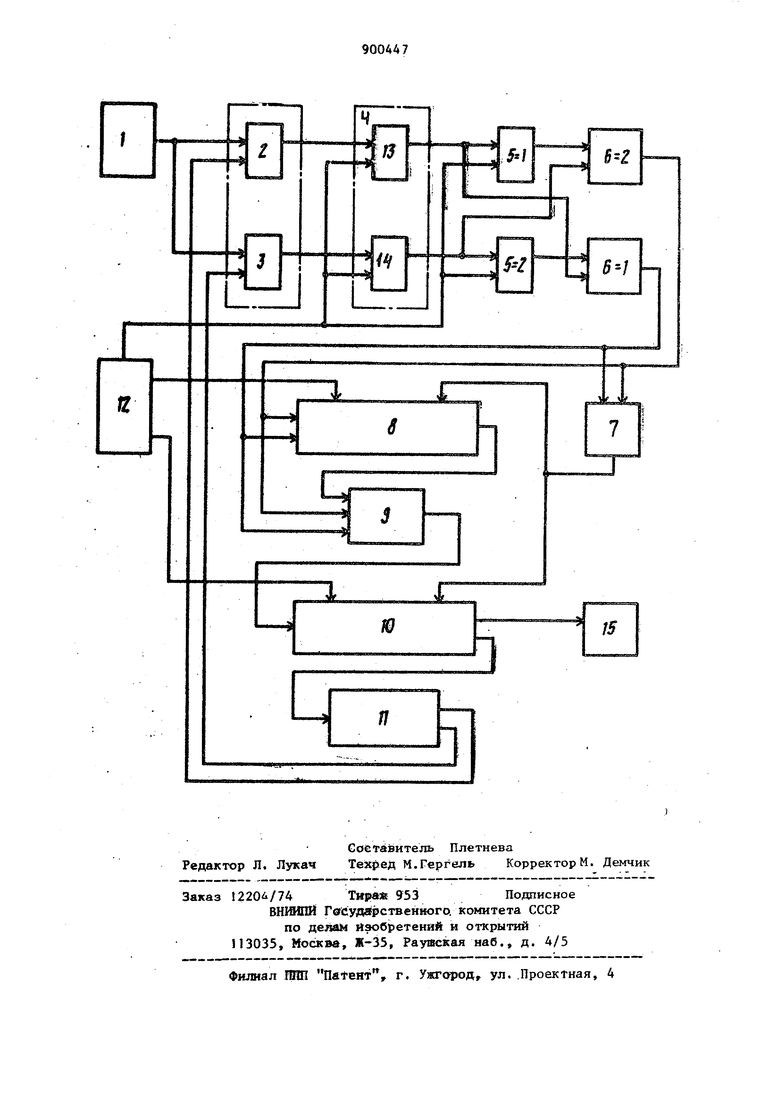

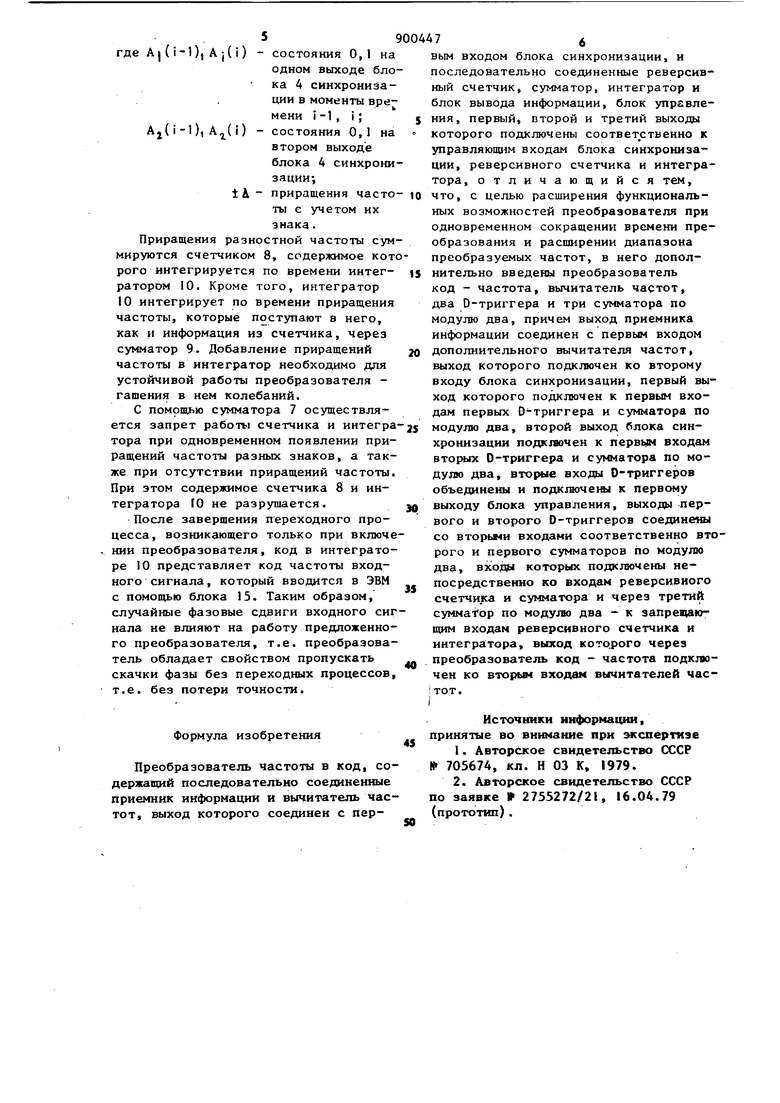

Поставленная цель достигается тем,и входами вычитателей частот 2 и 3. что в преобразователь частоты в код,К выходам блока 12 управления подклюсодержащий последовательно соединен- jчены блок 4, D-триггеры , , счетные приемник информации и вычитательсчетчик 8 и интегратор 10. Блок синчастот, выход которого соединен схронизации 4 выполнен на двух О-тригпервым входом блока синхронизации, игерах 13 и 14. К шяходу интегратора 10 последовательно соединенные реверсив-Ю подключен блок 15 вывода информаный счетчик, сумматор, интегратор и |0ции связи с ЭВМ. блок выхода информации, блок управления, первый, второй и третий выходы Преобразователь работает следуюкоторого подключены соответственнощн образом, к управляювдад входам блока синхронизации, реверсивного счетчика и интег- ,, в начале кодирования счетчик 8 и ратора, дополнительно введены преоб-интегратор 10 сбрасываются сигналами разователь код - частота, вычитательот блока 12 управления. Входной сигчастот, для D-триггера и три сумма-„ поступающий от приемника 1 на тора по модулю два, причем выход при-вьгчитатели2 и 3 частот и соответствуюемника информации соединен с первым j. У р устройства входом дополнительного вычитателя час-{i },2,3,...), сравнивается .по фазе тот, выход которого подключен ко ВТО-J. сигналом, поступакицим на другие вхорому входу блока синхронизации, пер-д вычитателей частоты, восстановленвый выход которого подключен к пер-„ из кода, содержащегося в интегравым входам первых D-триггера и сум- ,Q Восстановление сигнала из матора по модуле два, второй выход д помощью преобразователя 11 даблока синхронизации подключен к первым сигнал, соответствующий i-1-му входам вторых О-триггера и сумматорациклу работы преобразователя, так по модулю два, вторые входы О-триг- к код частоты сформирован в прегеров объединены и подклочены к пер- дыдущих циклах. Сигналы преобразовавому выходу блока управления, выходы jj „ J-Q выходах представпервого и второго О-триггеров соеди- д меандры, сдвинутые по фазе на йены со вторыми входами соответствен- но второго и первого сумматоров модуш) два, BbKOfS)j которых подключены непосредственно ко входам ревер- Сигналь разностной частоты с высивиого счетчика и сумматора и через одов вычитателя частот поступают на третий cyhMaTop по модулю два - к за-информационные входы блока синхронизапрещаюпвда входам реверсивного счет-ц и 4, тактирующие входы которого чшса и интегратора,выход которого че-воспринимают сигнал от блока 12 управрез преобразователь код-частота подклю-«. Синхронизированные с работой чей ко ВТОРЫМ входам вычитателей частот.вычислительных блоков преобразоватеНа чертеже представлена фушсциа- сигналы разностной частоты задернальная схема преобразователя часто- иваются на один цикл работа преобраты в код. 1жзователя в О-триггерах и .

Преобразователь содержит последа- сумматоры и формируют приравательно соединеюше приемник 1 инфор-щения разностной частоты и одновремации, вычитатели 2 и 3 частот, блок определяют знак прира цения: на 4 синхронизации, .D-триггеры 5«1 и ,выходе одного из сумматоров получаcyfftiaTOpti 6-1, 7 по модулю два. положительною приращения разВыходы двух су о«1торов 6-1 и под- ностной частоты, а иа выходе второго кяючены к соответствутции входам сум-сумматора - отрицательные приращения, матора 7 по модулю два, входам ревер-Работа сумматоров 6-1 и 6-2 может сивного счетчика 8 и входам суммато-g описана разностными уравиера 9. Третий вход сумматора 9 соедииеищ,ями. с выходом счетчика 8, а к выходу сум- г /. / матора 9 подключеи интегратор 10. Вы-. a iJmoda ход суйматора 7 подключеи к запрещаю-г г / д П щим входам счетчика 8 и интегратора4 г A,U-UJnio li где Aj(i-l), А j(i) состояния о,1 на одном выходе бло ка 4 синхронизации в моменты вре мени 1-1 , i; Aj(i-l),A(i) состояния О,1 на втором выходе блока 4 синхрони зации; приращения часто ты с учетом их знака. Приращения разностной частоты сум мируются счетчиком 8, содержимое кот рого интегрируется по времени интегратором 10. Кроме того, интегратор 10 интегрирует по времени приращения частоты, которые поступают в него, как и информация из счетчика, через сумматор 9. Добавление приращений частоты в интегратор необходимо для устойчивой работы преобразователя гашения в нем колебаний. С помощью сумматора 7 осуществляется запрет работы счетчика и интегра тора при одновременном появлении приращений частоты разных знаков, а также при отсутствии приращений частоты При этом содержимое счетчика 8 и интегратора 10 не разрушается. После завершения переходного процесса, возникающего только при включе нии преобразователя, код в интеграторе 10 представляет код частоты входного сигнала, который вводится в ЭВМ с помощью блока 15. Таким образом, случайные фазовые сдвиги входного сиг нала не влияют на работу предложенного преобразователя, т.е. преобразователь обладает свойством пропускать скачки фазы без переходных процессов т.е. без потери точности. Формула изобретения Преобразователь частола в код, содержащий последовательно соединенные приемник информации и вычитатель час тот, выход которого соединен с пер7вым входом блока синхронизации, и последовательно соединенные реверсивный счетчик, сутчматор, интегратор и блок вывода информации, блок управления, первый, второй и третий выходы которого подключены соответственно к управляющим входам блока синхронизации, реверсивного счетчика и интегратора, отличающийся тем, что, с целью расширения функциональных возможностей преобразователя при одновременном сокращении времени преобразования и расширении диапазона преобразуемых частот, в него дополнительно введены преобразователь код - частота, вычитатель частот, два D-триггера и три сумматора по модулю два, причем выход приемника информации соединен с первым входом дополнительного вычитателя частот, выход которого подклочен ко второму входу блока синхронизации, первый выход которого подключен к первым входам первых 0-триггера и сумматора по модулю два, второй выход блока синхронизации подклочен к первом входам вторых 0-триггера и cy в aтopa по модулю два, вторые входы О-триггеров объединены и пoдкJвoчeшJI к первому выходу блока управления, выходы первого и второго О-триггеров соедине№1| со вторьми входами соответственно второго и первого сумматоров по модулю два, входы которых подключены непосредственно ко входам реверсивного счетчика и сумматора и через третий сумматор по модулю два - к эапрев ающим входам реверсивного счетчика и интегра:тора, выход которого через преобразователь код - частота подключен ко вто{и м входам вычнтателей часИсточники чиформащия, принятые во внимание при экспертизе 1.Авторское свндетельство CCCf 705674, кл. Н 03 К. 1979. 2.Авторское свндетельство СССР о заявке 2755272/21, 16.04.79 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный преобразователь частоты в код | 1980 |

|

SU936422A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| СЛЕДЯЩИЙ АЦП МНОГОРАЗРЯДНЫХ ПРИРАЩЕНИЙ | 2016 |

|

RU2619887C1 |

| Система для передачи телеизмерительной информации | 1982 |

|

SU1113832A1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД | 2018 |

|

RU2699679C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| Приемник сигналов офсетной фазовой манипуляции | 1987 |

|

SU1434559A1 |

Авторы

Даты

1982-01-23—Публикация

1980-05-29—Подача