Изобретение относится к автоматике и вычислительной технике, в частности к устройствам преобразования частот в коды.

Известен многоканальный преобразователь частоты в код, содержащий в каждом из каналов элемент ЗАПРЕТ, счетчик импульсов, блок установки коэффициента пересчета, триггер и генератор одиночных импульсов. Общими узлами для всех каналов преобразователя являются генератор калиброванной частоты, измерительный счетчик, элемент ИЛИ, блок памяти, элемент И, блок управления и счетчик адреса (см. АС СССР №859944 кл. G01R 23/02, H03K 13/20).

Недостатками его являются сложность структуры и отсутствие интерфейса обмена с ЭВМ.

Наиболее близким по технической сущности (прототипом) к заявленному устройству является многоканальный преобразователь частоты в код, содержащий m приемников информации, каждый из которых подключен к соответствующему счетчику периодов сигнала. Выходы m счетчиков периодов сигнала соединены с входами коммутатора, выход которого подключен к одному из входов вычитателя периодов. Выход вычитателя периодов соединен через блок синхронизации с входами реверсивного счетчика и интегратора. Другой вход интегратора подключен к выходу реверсивного счетчика. К выходу интегратора подключены второй вход вычитателя периодов и вход преобразователя период-частота, выход которого соединен с блоком связи с ЭВМ. Другие входы счетчиков периодов сигналов, коммутатора, вычитателя периодов, блока реверсивного счетчика, интегратора, преобразователя период-частота и блока связи с ЭВМ подключены к соответствующим выходам блока управления. Реверсивный счетчик включает в себя одноразрядный сумматор и регистр сдвига, соединенные по кольцевой схеме, а интегратор также включает в себя одноразрядный сумматор и регистр сдвига, соединенные по кольцевой схеме (см. АС СССР №936422 кл. H03K 13/20). Недостатками прототипа являются сложность структуры, а также то, что его нельзя использовать для контроля в приемниках информации частоты сигналов в опросном режиме по запросу ЭВМ.

Задачей предлагаемого технического решения является создание более простой структуры многоканального преобразователя частоты в код, позволяющего осуществлять контроль частоты сигналов в m приемниках в информации в опросном режиме по запросу ЭВМ.

Решение поставленной задачи достигается тем, что в многоканальный преобразователь частоты в код, содержащий m приемников информации, m счетчиков периодов сигналов, блок связи с ЭВМ и блок управления, выход которого соединен с первыми входами всех m счетчиков периодов сигналов, вторые входы которых соединены с соответствующими выходами m приемников информации, введены m буферных устройств, блок чтения слов данных и формирователь импульсов сброса, выход которого соединен с входами начальной установки всех m счетчиков периодов сигналов, блока управления и блока чтения слов данных, причем выходы каждого из m счетчиков периодов сигналов подключены через соответствующие буферные устройства к входной шине данных блока связи с ЭВМ, выходы разрешения обмена и чтения данных которого соединены с соответствующими входами блока чтения слов данных, m выходов которого соединены с соответствующими входами m буферных устройств, причем первый выход блока чтения слов данных дополнительно соединен с другим входом начальной установки блока управления, счетный вход которого соединен с выходом синхронизации блока связи с ЭВМ.

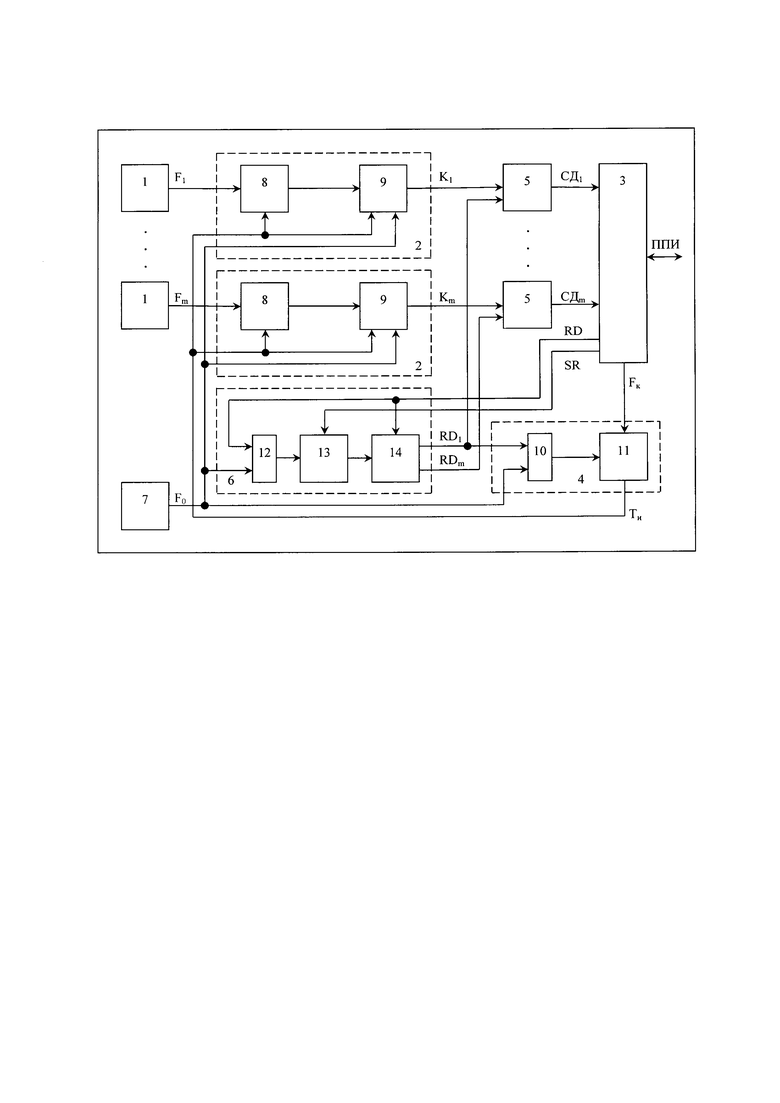

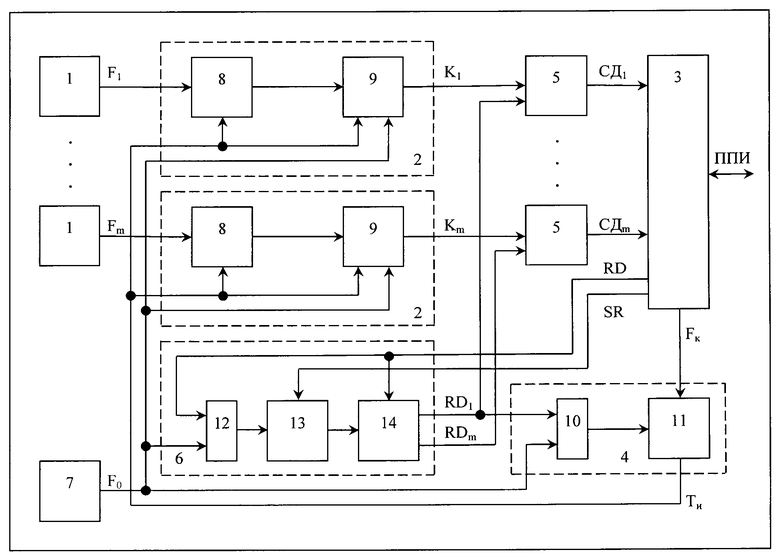

На чертеже представлена структурная схема многоканального преобразователя частоты в код.

Многоканальный преобразователь частоты в код содержит m приемников 1 информации, m счетчиков 2 периодов сигналов, блок 3 связи с ЭВМ и блок 4 управления, выход которого соединен с первыми входами всех m счетчиков 2 периодов сигналов, вторые входы которых соединены с соответствующими выходами m приемников 1 информации, введенные m буферных устройств 5, блок 6 чтения слов данных и формирователь 7 импульсов сброса, выход которого соединен с входами начальной установки всех m счетчиков 2 периодов сигналов, блока 4 управления и блока 6 чтения слов данных, причем Выходы каждого из m счетчиков 2 периодов сигналов подключены через соответствующие буферные устройства 5 к Входной шине данных блока 3 связи с ЭВМ, выходы разрешения обмена и чтения данных которого соединены с соответствующими входами блока 6 чтения слов данных, m выходов которого соединены с соответствующими входами m буферных устройств 5, причем первый выход блока 6 чтения слов данных дополнительно соединен с другим входом начальной установки блока 4 управления, счетный вход которого соединен с выходом синхронизации блока 3 связи с ЭВМ. Счетчик 2 периодов сигнала включает в себя последовательно соединенные счетчик 8 импульсов и выходной регистр 9. Блок 4 управления включает в себя последовательно соединенные схему ИЛИ 10 и формирователь 11 интервала измерения. Блок 6 чтения слов данных включает в себя последовательно соединенные схему ИЛИ 12, счетчик 13 адреса и дешифратор 14.

Многоканальный преобразователь частоты в код работает следующим образом.

Включение преобразователя в составе системы сбора и обработки информации производится путем подачи на него напряжения питания. В момент включения питания с формирователя 7 импульсов сброса поступает импульс F0 на входы начальной установки всех m счетчиков 2 периодов сигналов, блока 4 управления и блока 6 чтения слов данных и устанавливает их в нулевое состояние, кроме блока 6 чтения слов данных, в котором в режиме предустановки (при отсутствии сигнала разрешения обмена SR с блока 3 связи с ЭВМ) происходит по заднему фронту импульса F0 через схему ИЛИ 12 запись в счетчик 13 адреса начального кода, подготавливающего дешифратор 14 для формирования сигнала RD1 с первого выхода.

По окончании импульса сброса F0, поступающего в блоке 4 управления через элемент ИЛИ 10 на вход обнуления формирователя 11 интервала измерения, происходит перевод его в режим счета тактовых импульсов калиброванной частоты Fк с выхода синхронизации блока 3 связи с ЭВМ. Через определенное количество тактовых импульсов калиброванной частоты Fк в блоке 4 управления на выходе формирователя 11 интервала измерения формируется измерительный импульс нормированной длительности Ти, который поступает на первые входы всех m счетчиков 2 периодов сигналов и разрешает преобразование поступающих на вторые их входы частот контролируемых сигналов F1…Fm с соответствующих m приемников 1 информации в фиксируемые на выходах соответствующих счетчиков 2 периодов сигналов коды K1…Km. При этом преобразование осуществляется следующим образом: по переднему фронту измерительного импульса нормированной длительности Ти во всех m счетчиках 2 периодов сигналов счетчики 8 импульсов переводятся в режим счета, а выходные регистры 9 продолжают сохранять начальное нулевое состояние; по заднему фронту измерительного импульса нормированной длительности Ти во всех m счетчиках 2 периодов сигналов счетчики 8 импульсов обнуляются, а выходные регистры 9 фиксируют коды K1…Km состояния счетчиков 8 импульсов, предшествующие их обнулению. Погрешность преобразования в таком случае не превышает ±1 период частоты контролируемых сигналов F1…Fm.

С момента фиксации на выходах всех m счетчиков 2 периодов сигналов кодов K1…Km преобразователь готов к первому циклу опроса состояния этих счетчиков по запросу ЭВМ. В этом случае при запросе информации ЭВМ через последовательный периферийный интерфейс (ППИ) блок 3 связи с ЭВМ формирует на выходе разрешения обмена сигнал SR, который переводит в блоке 6 чтения слов данных счетчик 13 адреса в режим счета. При поступлении с выхода чтения данных блока 3 связи с ЭВМ m сигналов чтения RD на m выходах дешифратора 14 блока 6 чтения слов данных формируются последовательно сигналы опроса RD1…RDm, которые осуществляют передачу с выходов m счетчиков 2 периодов сигналов зафиксированных в них кодов K1…Km измеренных частот контролируемых сигналов F1…Fm через соответствующие буферные устройства 5 в виде слов данных СД1…СДm на входную шину данных блока 3 связи с ЭВМ. Дополнительно сигнал опроса RD1 с первого выхода дешифратора 14 блока 6 чтения слов данных поступает на другой вход начальной установки блока 4 управления и сбрасывает в нем через схему ИЛИ 10 формирователь 11 интервала измерения в нулевое состояние. При этом по окончании сигнала опроса RD1 происходит перевод формирователя 11 интервала измерения в режим счета тактовых импульсов калиброванной частоты Fк с выхода синхронизации блока 3 связи с ЭВМ. В результате через определенное количество тактовых импульсов калиброванной частоты Fк в блоке 4 управления на выходе формирователя 11 интервала измерения формируется очередной измерительный импульс нормированной длительности Ти, подготавливая все m счетчиков 2 периодов сигналов к очередному преобразованию частот контролируемых сигналов F1…Fm в коды K1…Km.

При завершении опроса Состояния всех m счетчиков 2 периодов сигналов с выхода разрешения обмена блока 3 связи с ЭВМ снимается сигнал SR. В результате счетчик 13 адреса блока 6 чтения слов данных переходит в режим предустановки и по заднему фронту m+1 сигнала чтения RD через схему ИЛИ 12 происходит запись в счетчик 13 адреса начального кода, подготавливающего дешифратор 14 для формирования сигнала RD1 с первого выхода в следующем цикле опроса.

Таким образом, такое техническое решение многоканального преобразователя частоты в код, когда преобразование частот контролируемых сигналов F1…Fm в коды K1…Km осуществляется не постоянно, а только по инициативе ЭВМ в требуемые моменты времени в соответствии с заложенными в программном обеспечении циклами опроса, позволяет упростить его структуру и, как следствие, повысить надежность его работы.

Совокупность признаков, подобная рассмотренной автором в данном предложении, не встречалась ранее для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям "новизна" и "изобретательский уровень".

Рассмотренный многоканальный преобразователь частоты в код можно использовать в устройствах контроля частоты вращения двигателей электронасосных агрегатов космических аппаратов и в других устройствах, где требуется многоканальный контроль изменения частоты сигналов в опросном режиме по запросу ЭВМ. Блоки предложенного преобразователя могут быть выполнены на интегральных микросхемах любого типа и степени интеграции, в частности на микросхемах серии 1554, а блок связи с ЭВМ на специализированной микросхеме Н5503ХМ5-171 АЕЯР.431260.146 ТУ карта заказа ЮШКР.430103.009Д.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Приемник последовательного кода | 1988 |

|

SU1674378A1 |

| АВТОМАТИЗИРОВАННОЕ РАБОЧЕЕ МЕСТО ОПЕРАТОРА УПРАВЛЕНИЯ ВОЗДУШНЫМ ДВИЖЕНИЕМ | 2001 |

|

RU2219586C2 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1474635A1 |

| Устройство для ввода информации | 1979 |

|

SU855649A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам преобразования частот в коды. Технический результат - создание более простой структуры многоканального преобразователя частоты в код, позволяющего осуществлять контроль частоты сигналов в m приемниках в информации в опросном режиме по запросу ЭВМ. Для этого в многоканальный преобразователь частоты в код, содержащий m приемников информации, m счетчиков периодов сигналов, блок связи с ЭВМ и блок управления, выход которого соединен с первыми входами всех m счетчиков периодов сигналов, вторые входы которых соединены с соответствующими выходами m приемников информации, введены m буферных устройств, блок чтения слов данных и формирователь импульсов сброса. Выходы каждого из m счетчиков периодов сигналов подключены через соответствующие буферные устройства к входной шине данных блока связи с ЭВМ. Выходы разрешения обмена и чтения данных блока связи с ЭВМ соединены с соответствующими входами блока чтения слов данных, m выходов которого соединены с соответствующими входами m буферных устройств. Первый выход блока чтения слов данных дополнительно соединен с другим входом начальной установки блока управления, счетный вход которого соединен с выходом синхронизации блока связи с ЭВМ. 1 ил.

Многоканальный преобразователь частоты в код, содержащий m приемников информации, m счетчиков периодов сигналов, блок связи с ЭВМ и блок управления, выход которого соединен с первыми входами всех m счетчиков периодов сигналов, вторые входы которых соединены с соответствующими выходами m приемников информации, отличающийся тем, что в него введены m буферных устройств, блок чтения слов данных и формирователь импульсов сброса, выход которого соединен с входами начальной установки всех m счетчиков периодов сигналов, блока управления и блока чтения слов данных, причем выходы каждого из m счетчиков периодов сигналов подключены через соответствующие буферные устройства к входной шине данных блока связи с ЭВМ, выходы разрешения обмена и чтения данных которого соединены с соответствующими входами блока чтения слов данных, m выходов которого соединены с соответствующими входами m буферных устройств, причем первый выход блока чтения слов данных дополнительно соединен с другим входом начальной установки блока управления, счетный вход которого соединен с выходом синхронизации блока связи с ЭВМ.

| Многоканальный преобразователь частоты в код | 1980 |

|

SU936422A1 |

| Многоканальный преобразователь частоты в код | 1978 |

|

SU712953A1 |

| Преобразователь частоты в код | 1972 |

|

SU482002A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

2019-09-09—Публикация

2018-12-04—Подача