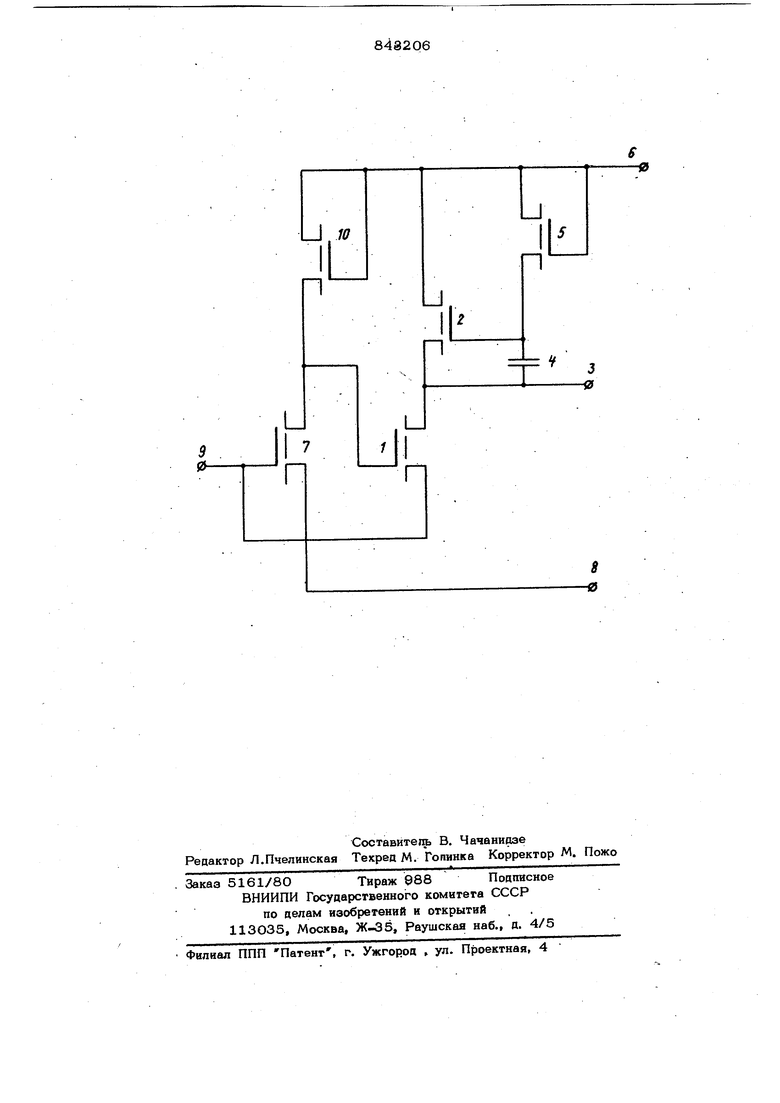

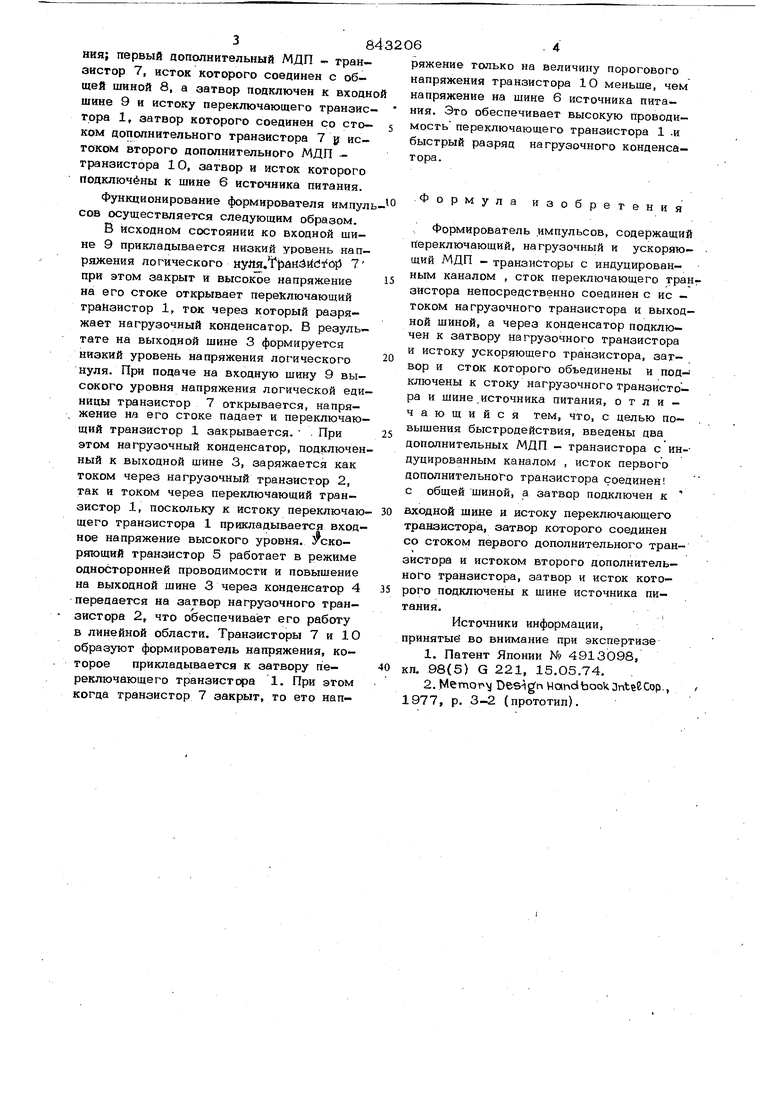

Изобретение относится к автоматике и вычислительной технике. Известны формирователи импульсов , содержащие переключающий, нагрузочный и ускоряющий МДП - транзисторы с индуцированным каналом, а также конаен- сатор Наиболее близок к предцагаемому форми рователь импупьсов, содержащий переключающий,нагруЗОННЫЙ и ускоряющий МДП-тран зисторы с индуцированным каналом, сток переключающего транзистора непосредстве но соединен с истоком нагрузочного транзистора и выходной шиной, а через конденсатор подключен к затврру нагрузочного транзистора и истоку ускор5пощего транзистора, затвор и сток которого объединены и подключены к стоку нагрузочного транзистора и шине источника питания Недостаток: известных устройств - низкое быстродействие. . Цель изобретения - повышенве быстродействия формирователя импульсов. Указанная цель достигается за счет того, что в формирователь импульсов введены два дополнительных МДП - транзисторы с индуцированным каналом, исток первого дополнительногб транзистора соединен с общей шиной, а затвор подключен к входной шине и истоку переключающего транзистора, затвор которого соединен со стоком первого дополнительного транзистора и истоком второго дополнительного . транзистора, затвор и исток которого подкшочены к шине источника питания. На чертеже представлена принципиальная схема формирователя импульсов. Схема содержит следующие элементы перекпючающий МДП - транзистор 1, сток которого непосредственно соединен с источником нагрузочного МДП -транзистора 2, и выходной шиной 3, а через конденсатор 4 подключен к затвору нагрузочного транзистора 2 и истоку ускоряющего МДП - транзистора 5, затвор и сток которого объединены и подключены к стоку нагрузочного транзистора 2 и шине 6 источника пита38ння; первый допсшнигельный МДП - гранаисгор 7, исток которого соединен с общей шиной 8, а затвор подключен к входн шине 9 и истоку переключающего транаис тора 1, затвор которого соединен со сто- ком дополнительного транзистора 7 g истоком второго дополнительного МДП транзистора 10, затвор и исток которого подключены к шине 6 источника питания. Функционирование формирователя импул сов осуществляется следующим обрааом. В исходном состоянии ко входной шине 9 прикладывается низкий уровень напряжения логического муйя.ТрййЗ бтф 7 при этом закрыт и высокое напряжение на его стоке открывает переключающий транзистор 1, ток через который разряжает нагрузочный конденсатор. В результате на выходной шине 3 формируется низкий уровень напряжения логического нуля. При подаче на входную шину 9 высокого уровня напряжения логической еди ницы транзистор 7 открывается, напряжение на его стоке падает и переключающий транзистор 1 закрывается. При этом нагрузочный конденсатор, подключен ный к выходной шине 3, заряжается как током через нагрузочный транзистор 2, так и током через переключающий тран- аистор 1, поскольку к истоку переключаю

щего транзистора 1 прикладывается входное напряжение высокого уровня. Ускоряющий транзистор 5 работает в режиме односторонней проводимости и повышение на выходной шине 3 через конденсатор 4 передается на затвор нагрузочного транзистора 2, что обеспечивает его работу в линейной области. Транзисторы 7 и 1О образуют формирователь напряжения, которое прикладывается к затвору переключающего транзистора 1. При этом когда транзистор 7 закрыт, то ето наптранзистора, затвор которого соединен со стоком первого дополнительного транзистора и истоком второго дополнительного транзистора, затвор и исток которого подключены к шине источника питания.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии № 4913098, кп. 98(5) G 221, 15.05.74. 2. Memorvj Des-igfn Handbook .,

1977, p. 3-2 (прототип). 6 ряжение только на величину порогового напряжения транзистора 10 меньше, чем напряжение на шине 6 источника питания. Это обеспечивает высокую Проводимость переключающего транзистора 1 -и быстрый разряд нагрузочного конденсатора. Формула изобретения Формирователь импульсов, содержащий Переключающий, нагрузочный и ускоряющий МДП - транзисторы с индуцированным каналом , сток переключающего гранг зистора непосредственно соединен с ис - током нагрузочного транзистора и выходной шиной, а через конденсатор подключен к затвору нагрузочного транзистора и истоку ускоряющего транзистора, затвор и сток которого объединены и под-ключены к стоку нагрузочного транзистора и шине .источника питания, отличающийся тем, что, с целью по- . вышения быстродействия, введены два дополнительных МДП - транзистора с ин-дуцированным каналом , исток первого дополнительного транзистора соединен с общей шиной, а затвор подключен к входной шине и истоку переключающего

П

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное устройство | 1980 |

|

SU902258A1 |

| Формирователь импульса по включению напряжения питания | 1985 |

|

SU1272496A1 |

| Формирователь импульсов | 1985 |

|

SU1309278A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| Дешифратор адреса | 1978 |

|

SU741470A1 |

| Управляемый инвертор на мдп-транзисторах | 1976 |

|

SU641655A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

LJ

I I

9 0u

n

8

-0

Авторы

Даты

1981-06-30—Публикация

1979-10-31—Подача