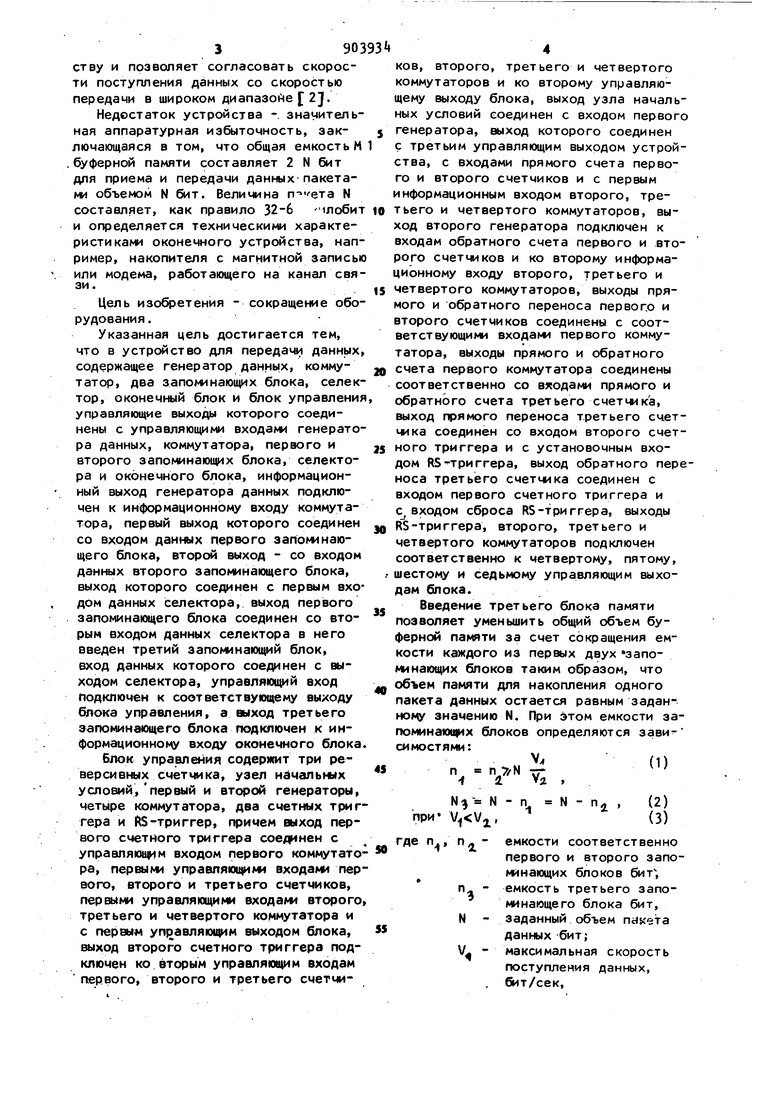

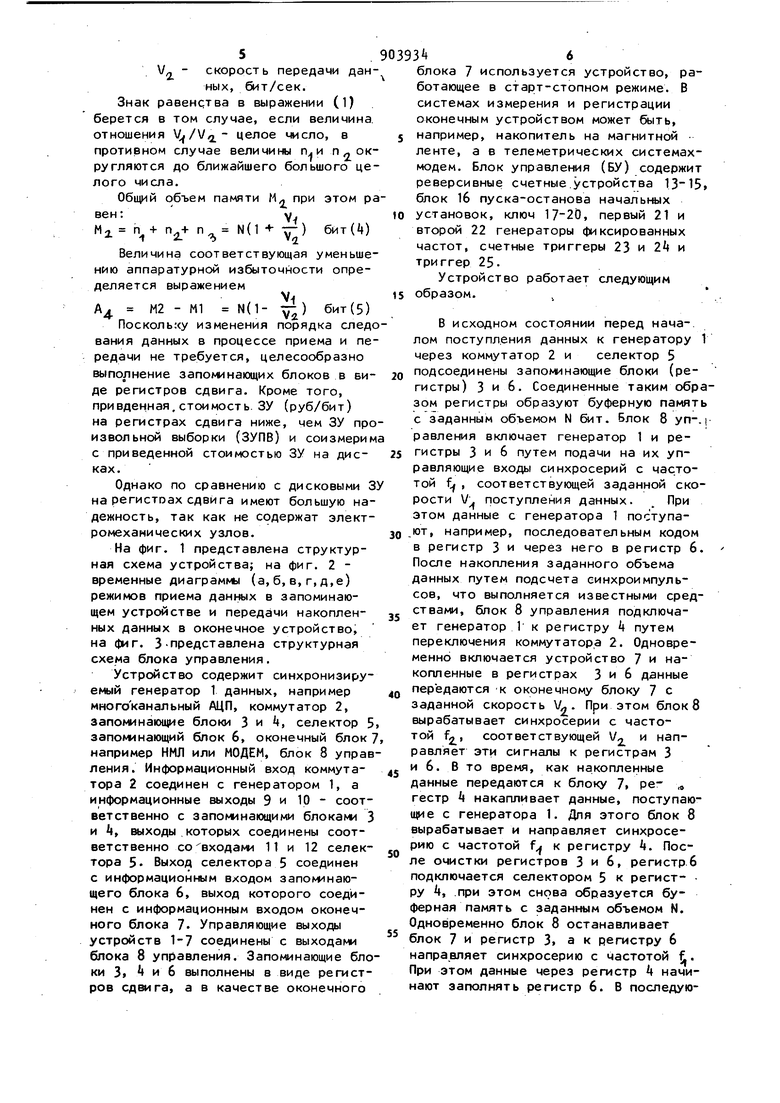

Изобретение относится к передаче информации, а точнее к устройствам для изменения скорости прохождения данных, может быть использовано в различных устройствах регистрации цифровых данных, а также в системах передаем данных по каналам связи. Известно устройство передачи данных, содержащее генератор данных, состоящий из дискретизатора и аналого-цифрового преобразователя (АЦП), блок сжатия данных, состоящий из бло ка управления, блоков обработки данных и буферного запоминающего устрой ства (БЗУ). Выход БЗУ подключен к каналу связи р. Однако в этом устройстве во время передачи данных в канал связи БЗУ не может принимать поступающие данны вследствие чего часть их теряется. Наиболее близко по технической сущности к предлагаемому,устройство, содержащее генератор данных, состоя1Э1Й из устройств для определения физ ических величин и преобразования этих величин в частотный сигнал, селективный запоминающий блок, состоящий из входного селектора, двух запоминающих устройств, выполненных в виде дисковых накопителей, выходного селектора и двух блоков управления приводами дисковых накопителей, а также оконечное устройство (накопитель .на магнитной ленте), синхрогенератор и блок .управления оконечным устройством и селективным запоминающим блоком. Селективный блок включен между генератором данных и оконечкмм устройством, при этом каждое из двух запоминающих устройств ( ЗУ)поочередно, подключаются входным и выходным селекторами к генератору данных и к оконечному устройству так, что всегда одно ЗУ подключено к генератору данных, в то время как другоек оконечному устройству. Это устрой- . ство исключает потери данных во времени передачи к оконечному .устрой390ству и позволяет согласовать скорости поступления данных со скоростью передачи в широком диапазойе f . Недостаток устройства -. зиа14ительная аппаратурная избыточность, заключающаяся в том, что общая емкостьМ .буферной памяти составляет 2 N бит для приема и передачи данных пакетами объемом N бит. Величина п---ета N составляет, как правило 32-6 шобит и определяется техническими характеристиками оконечного устройства, например, накопителя с магнитной записью или модема, работающего на канал свя Цель изо етения - сокращение оборудования. Указанная цель достигается тем, что в устройство для передачи данных содержащее генератор данных, коммутатор, два запоминающих блока, селек тор, оконечный блок и блок управлени управляющие выходы которого соединены с управляющими входами генерато ра данных, коммутатора, первого и второго запоминающих блока, селектора и оконечного блока, информационный выход генератора данных подключен к информационному входу коммутатора, первый выход которого соединен со входом данных первого запоминающего блока, второй выход - со входом данных второго запоминающего блока, выход которого соединен с первым вхо дом данных селектора, выход первого запоминающего блока соединен со вто рым входом данных селектора в него введен третий запоминающий блок, вход данных которого соединен с выходом селектора, управляющий вход Подключен к соответствую||(ему выходу блока управления, а выход третьего з атюминающего блока подключен к информационному входу оконечного блока блок управления содержит три ревер си вьмх счетчика, узел начальных условий,первый и второй генераторы, четыре коммутатора, два счетных триг гера и ftS-триггер, причем выход первого счетного триггера соединен с управляю1и9 м входом первого коммутато ра, первыми управляющими входами пер вого, второго и третьего счетчиков, первыми управляющими входами второго третьего и четвертого коммутатора и с первым уп авляюир м выходом блока, выход второго счетного триггера подключен ко вторым управляющим входам первого, второго и третьего счетчиков, второго, третьего и четвертого коммутаторов и ко второму управляющему выходу блока, выход узла начальных условий соединен с входом первого генератора, выход которого соединен с третьим управляющим выходом устройства, с входами прямого счета первого и второго счетчиков и с первым информационным входом второго, третьего и четвертого коммутаторов, выход второго генератора подключен к входам обратного счета первого и второго счетчиков и ко второму информационному входу второго, третьего и четвертого коммутаторов, выходы прямого и обратного переноса первого и второго счетчиков соединены с соответствующими входами первого коммутатора, выходы прямого и обратного счета первого коммутатора соединены соответственно со входами прямого и обратного счета третьего счетчика, выход прямого переноса третьего счетчика соединен со входом второго счетного триггера и с установочным входом RS- триггера, выход обратного переноса третьего счетчика соединен с входом первого счетного триггера и с входом сброса RS-триггера, выходы RS-триггера, второго, третьего и четвертого коммутаторов подключен соответственно к четвертому, пятому, шестому и седьмому управляющим выходам блока. Введение третьего блока памяти позволяет уменьшить общий объем буферной памяти за счет сокращения емкости каждого из первых двух запоминающих блоков таким образом, что объем памяти для накопления одного пакета данных остается равным заданному значению N. При этом емкости запоминающих блоков определяются зави симостями:(1) % V V . N9 N - л N - п, при ,, где л, . емкости соответственно первого и второго запоминающих блоков бит, п - емкость третьего запоминающего блока бит, N - заданный объем пакета данных бит; V - максимальная скорость поступления данных, . бит/сек. скорость передачи дан ных, бит/сек. Знак равенства в выражении (1) берется в том случае, если величина отношения целое число, в противном случае величины п. и п ок ругляются до ближайшего большого це лого числа. Общий сэбъем памяти Мл при этом р вен :V М-, п. + п N{ 1 - ) бит (4) ) ч - -ц 2. Величина соответствующая уменьше нию аппаратурной избыточности определяется выражением А. М2 - Ml N(1- у) бит (5) Поскольху изменения порядка след вания данных в процессе приема и пе редачи не требуется, целесообразно выполнение запоминающих блоков в виде регистров сдвига. Кроме того, привденная, стоимость. ЗУ (руб/бит) на регистрах сдвига ниже, чем ЗУ про извольной выборки (ЗУПВ) и соизмерим с приведенной стоимостью ЗУ на дисках. Однако по сравнению с дисковыми З на регистоах сдвига имеют большую надежность, так как не содержат электромеханических узлов. На фиг. 1 представлена структурная схема устройства; на фиг. 2 временные диаграммы (а,б,в,г,д,е) режимов приема данных в запоминающем устройстве и передачи накопленных данных в оконечное устройство, на фиг. 3-представлена структурная схема блока управления. Устройство содержит синхронизируемый генератор 1 данных, например многоканальный АЦП, коммутатор 2, запоминающие блоки 3 и , селектор 5 запоминающий блок 6, оконечный блок например НМЛ или МОДЕМ, блок 8 управ ления. Информационный вход коммутатора 2 соединен с генератором 1, а информационные выходы 9 и 10 - соответственно с запоминающими блоками 3 и Ц, выходы которых соединены соответственно со входами 11 и 12 селектора 5- Выход селектора 5 соединен с информационным входом запоминающего блока 6, выход которого соединен с информационным входом оконечного блока 7. Управляющие выходы устройств 1-7 соединены с выходами блока 8 управления. Запоминающие бло ки 3 j и 6 выполнены в виде регистров сдвига, а в качестве оконечного блока 7 используется устройство, работающее в старт-стопном режиме. В системах измерения и регистрации оконечным устройством может , например, накопитель на магнитной ленте, а в телеметрических системахмодем. Блок управления (БУ) содержит реверсивные счетные.устройства 13 15 блок 16 пуска-останова начальных установок, ключ 17-20, первый 21 и второй 22 генераторы фиксированных частот, счетные триггеры 23 и 2 и триггер 25. Устройство работает следующим образом., В исходном состоянии перед нача-. лом поступления данных к генератору 1 через коммутатор 2 и селектор 5 подсоединены запоминающие блоки (регистры) 3 и 6. Соединенные таким образом регистры образуют буферную память с заданным объемом N бит. Блок 8 уп-. | равления включает генератор 1 и регистры 3 и 6 путем подачи на их управляющие входы синхросерий с частотой f , соответствующей заданной скорости V. поступления данных. При этом данные с генератора 1 поступают, например, последовательным кодом в регистр 3 и через него в регистр 6. После накопления заданного объема данных путем подсчета синхроимпульсов, что выполняется известными средствами, блок 8 управления подключает генератор 1 к регистру k путем переключения коммутатора 2. Одновременно включается устройство 7 и накопленные в регистрах 3 и 6 данные передаются к оконечному блоку 7 с заданной скорость V,-. При этом блок 8 вырабатывает синхросерий с частотой f2, соответствующей /, и направляет эти сигналы к регистрам 3 и 6. В то время, как накопленные данные передаются к блоку 7 ре- ,в гестр k накапливает данные, поступающие с генератора 1. Для этого блок 8 вырабатывает и направляет синхросерию с частотой f к регистру Ц. После очистки регистров 3 и 6, регистр 6 подключается селектором 5 к регист- РУ . при этом снова образуется буферная память с заданным объемом N. Одновременно блок 8 останавливает блок 7 и регистр 3, а к регистру 6 направляет синхросерию с частотой . При этом данные через регистр k начинают заполнять регистр 6. В последую|цие интервалы времени процесс повторяется. На фиг. 2 представлены диаграммы а,,г,д,е интервалов соответственн поступления данных в регистр 3t передачи данных из регистра 3 к оконеч ному блоку (ОБ) 7 поступления данных в регистр 6, передачи данных из регистра 6 к ОБ и интервалов работы ОБ, поступления данных в регистр k, передачи данных из регистра i к ОБ. Таким образом, емкость каждого из запоминающих блоков (регистров) 3 и i определяется только тем объемом данных, буферизация которых не-, обходима в интервалы времени, а течение которых происходит передача накопленных данных к оконечному блоку.. Сокращение общего объема буферной памяти-позволяет уменьшить стоимость потребляющую мощность и габариты устройства. Формула изобретения . Г. Устройство для передачи данных содержащее генератор данных, коммутатор, два запоминающих блока, се лектор, оконечный блок и блок управления, управляющие выходы которого соединены с управляющими входами генератора данных, коммутатора, первого и второго запоминающих блока, селектору и оконечного блока, информационный выход генератора данных подключен к информационному входу комму татора, первый выход которого соединен со входом данных первого запоминающего блока, второй выход - со входом данных второго запоминающего блока, выход KofToporo соединен с пер вым входом данных селектора, выход первого запоминающего блока соединен со вторым входом данных селектора, отличающееся тем, что, с целью сокращения оборудования в него введен третий запоминающий бпок вход данных 1ютороро соединен с выходом селектора, управляющий вход подключен к соответствующему выходу блока управления, а выход третьего запоминающего блока подключен к инфо мационному входу оконечного блока. 2. Устройство по п. 1, о т л ичающееся тем, управ ления содержит три реверсивных счетчика узел начальных условий, первый генератор и второй генератор, четыре коммутатора, два счетных триггера и RS-триггер, причем выход первого счетного триггера соединен с управляющим входом первого коммутатора, первым управляющим входом первого, второго и третьего счетчиков, первыми управляющими вxoдa «1 второго, третьего и четвертого коммутатора и с первым управляющим выходом блока, выход второго счетного триггера подключен ко вторым управляющим входам первого, второго и третьего счетчиков, второго, третьего и четвертого коммутаторов и ко второму управляющему выходу блока, выход узла начальных условий соединен с входом первого генератора, выход которого соединен с третьим управляющим выходом устройства, с входами прямого счета первого и второго счетчиков и с первым информационным входам второго, третьего и четвертого коммутаторов, выход второго генератора подключен ко входам обратного счета первого и второго счетчиков и ко второму информационному входу, второго, третьего и четвертого коммутаторов, выходы прямого и обратного переноса первого и второго счетчиков соединены с соответствующими входами первого коммутатора, выходы прямого и обратного счета первого коммутатора соединены соответственно со входами прямого и обратного счета третьего счетчика выход прямого переноса третьего счетчика соединен с входом второго счетного триггера и с установочным входом RS-триггера, выход обратного переноса третьего счетчика соединен с входом первого счетного триггера и с входом сброса RS-триггера, выходы RS-триггера, второго, третьего и четвертого коммутаторов подкпючены соответственно к четвертому, пятому, шестому и седьмому управляющим выходам блока. Источники информации, принятые во внимание при экспертизе 1.Свириденко В.А. Анализ систем со сжатием данных. Н., Связь, 1977, с. 122. с. 2.Патент США И 137553, ЗбО - 6, опублик. 1979 (прототип). f

фуг. /

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство для обслуживания сообщений | 1983 |

|

SU1128256A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Позиционный дискретный электропривод | 1985 |

|

SU1352474A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| МНОГОКАНАЛЬНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 2011 |

|

RU2455672C1 |

| Устройство для управления обменом информации | 1981 |

|

SU1109729A1 |

| Устройство для сопряжения телеграфного аппарата с электронной вычислительной машиной | 1984 |

|

SU1242973A1 |

| Устройство для измерения отношения сигнал/шум | 1987 |

|

SU1465827A1 |

Фг/г.1

Авторы

Даты

1982-02-07—Публикация

1980-04-08—Подача