Uon

4i 0д

rs:)

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания для полупроводникового запоминающего устройства на полевых транзисторах с барьерным переходом | 1983 |

|

SU1109797A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Логический элемент на полевых транзисторах | 1986 |

|

SU1406778A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

Изобретение относится к микроэлектронике более конкретно к. интегральным схемам памяти, и может быть использовано в интегральных схемах оперативных, буферных и постоянных запоминающих усфоиств статического типа для считывания информации записанной в выбранном элементе памяти. Целью изобретения является повышение быстродействия усилителя считывания. Усилитель считывания содержит шину 1 считывания являюшуюся входом усили1еля считывания, подключенную к первому выводу нагрузочного элемента 2 и к входу инвертора 3 второй вывод нагрузочного элемента и вы хот инвертора объединены и подключены к входу усилительного элемента 4, выход 5 усичительного элемента является выходом СИ1ителя считывания. Максимальный эффект достигается выполнением нагрузочного элемента в виде полевого транзистора. 2 ил. § (Л с:

ц

сг

6 -ОИзобретение относится к микроэлектронике, более конкретно к интегральным схемам памяти, и мож ет быть иснользовано в интегральных схемах оперативных, буферных и постоянных запоминаюдшх устройств (ЗУ) статического типа для считывания информации, записанной в выбранном элементе памяти.

Целью изобретения является повышение быстродействия усилителя считывания.

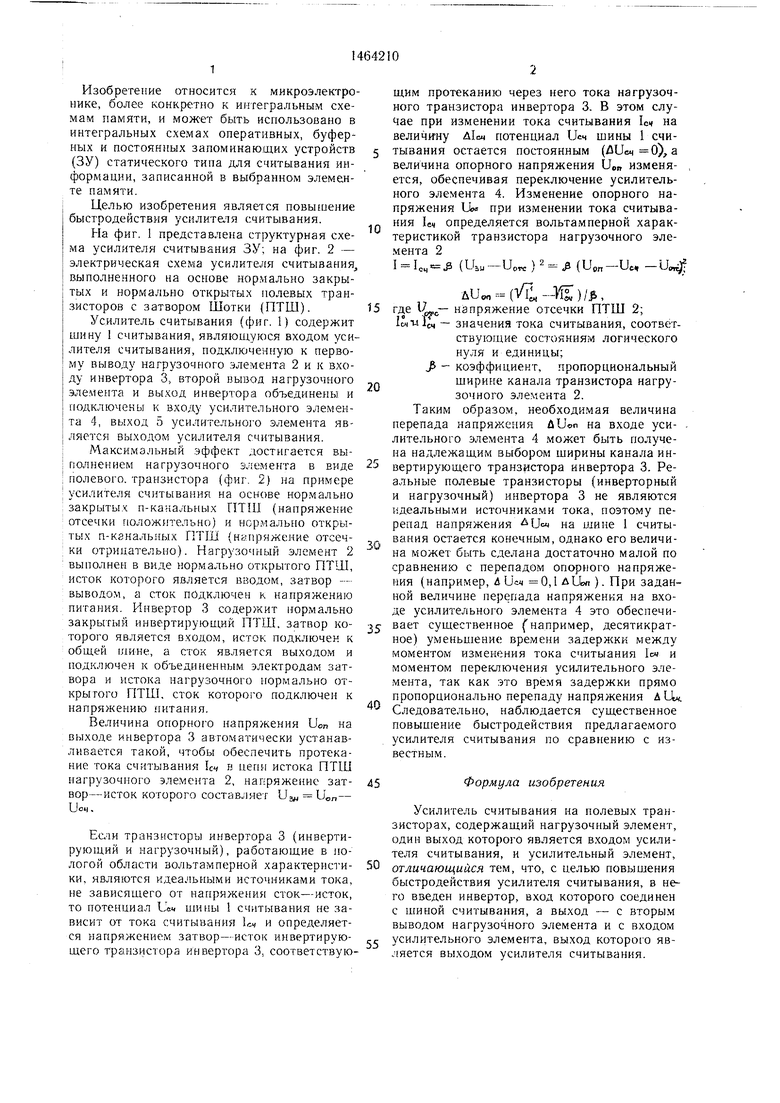

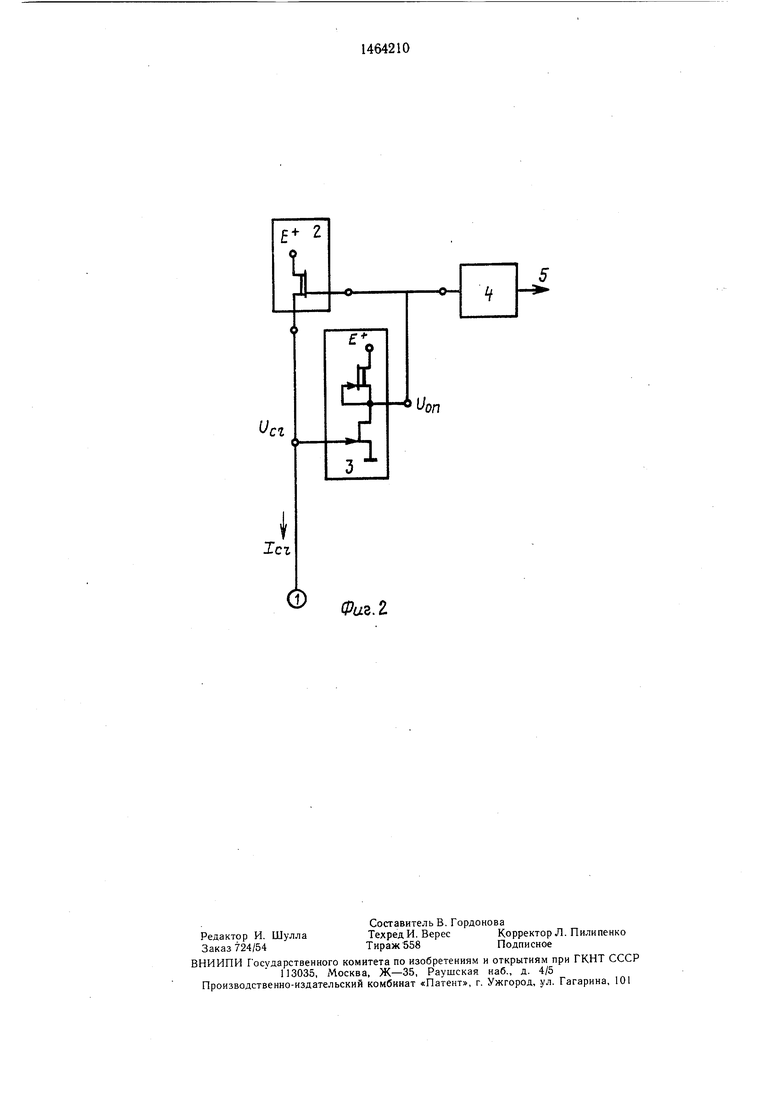

На фиг. 1 представлена структурная схема усилителя считывания ЗУ; на фиг. 2 - электрическая схема усилителя считывания выполненного на основе нормально закрытых и нормально открытых полевых транзисторов с затвором Шотки (ПТШ).

Усилитель считывания (фиг. 1) содержит шину 1 считывания, являющуюся входом усилителя считывания, подключенную к первому выводу нагрузочного элемента 2 и к входу инвертора 3, второй вывод нагрузочного элемента и выход инвертора объединены и подключены к входу усилительного элемента 4, выход 5 усилительного элемента является выходом усилителя считывания.

Максимальный эффект достигается выполнением нагрузочного элемента в виде полевого, транзистора (фиг. 2) на примере усилителя считывания на осн ове нормально закрытых п-канальных ПТШ (напряжение отсечки положительно) и нормально открытых п-кзнальных ПТШ (напряжение отсечки отрицательно). Нагрузочный элемент 2 выполнен в виде нормально открытого ПТШ,

исток которого является вводом, затвор -

выводом, а сток подключен к напряжению питания. Инвертор 3 содержит нормально закрытый инвертирующий ПТШ, затвор которого является входом, исток подключен к общей 1яине, а сток яв.ляется выходом и подключен к объединенным электродам затвора и истока нагрузочного нормально открытого ПТШ, сток которого подключен к напряжению питания.

Величина опорного напряжения Uon на выходе инвертора 3 автоматически устанавливается такой, чтобы обеспечить протекание тока считывания « в цепи истока ПТШ нагрузочного элемента 2, напряжение затвор- исток которого составляет U, Ucn-

Uo4.

Если транзисторы инвертора 3 (инвертирующий и нагрузочный), работающие в но- логой области вольтамперной характеристики, являются идеальными источниками тока, не зависящего от напряжения сток-исток, то потенциал Ue тины 1 считывания не зависит от тока считывания « и определяется напряжением затвор-исток инвертирующего транзистора инвертора 3, соответствую0

5

0

.5

0

5

0

5

0

5

щим протеканию через него тока нагрузочного транзистора инвертора 3. В этом случае при изменении тока считывания 1сч на величи ну Д1сч потенциал Ucs шины 1 считывания остается постоянным (), а величина опорного напряжения Uon изменя- , ется, обеспечивая переключение усилительного элемента 4. Изменение опорного напряжения Liw при изменении тока считывания 1еч определяется вольтамнерной характеристикой транзистора нагрузочного элемента 2

I IOM- (Ui.-Uo«) (Uon-Ut, иц

AU(VC.-.4iI)/, где i«.c напряжение отсечки ПТШ 2; 11 -и1сц - значения тока считывания, соответствующие состояниям логического нуля и единицы;

J5 - коэффициент, пропорциональный щирине канала транзистора нагрузочного элемента 2.

Таким образом, необходи.мая величина перепада напряжения и Uon на входе уси- . лительного элемента 4 может быть получена надлежащим выбором щирины канала инвертирующего транзистора инвертора 3. Реальные полевые транзисторы (инверторный и нагрузочный) инвертора 3 не являются идеальными источниками тока, поэтому перепад напряжения U« на шине 1 считывания остается конечным, однако его величина может быть сделана достаточно малой по сравнению с перепадом опорного напряжения (например, 4 UM 0,1 AllU ). При заданной величине перепада напряжения на входе усилительного элемента 4 это обеспечивает существенное (например, десятикратное) уменьшение времени задержки между моментом изменения тока считьгания 1сч и моментом переключения усилительного элемента, так как это время задержки прямо пропорционально перепаду напряжения дЦч. Следовательно, наблюдается существенное повышение быстродействия предлагаемого усилителя считывания по сравнению с известным.

Формула изобретения

Усилитель считывания на нолевых транзисторах, содержащий нагрузочный элемент, один выход которого является входом усилителя считывания, и усилительный элемент, отличающийся тем, что, с целью повыщения быстродействия усилителя считывания, в него введен инвертор, вход которого соединен с шиной считывания, а выход - с вторым выводом нагрузочного элемента и с входом усилительного элемента, выход которого является выходом усилителя считывания.

Фаъ.1

Авторы

Даты

1989-03-07—Публикация

1987-07-17—Подача