Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при разработке электрически стираемых программируемых постоянных запоминающих устройств (ЭСППЗУ) большой информационной емкости.

Цель изобретения - повышение надежности считывания информации.

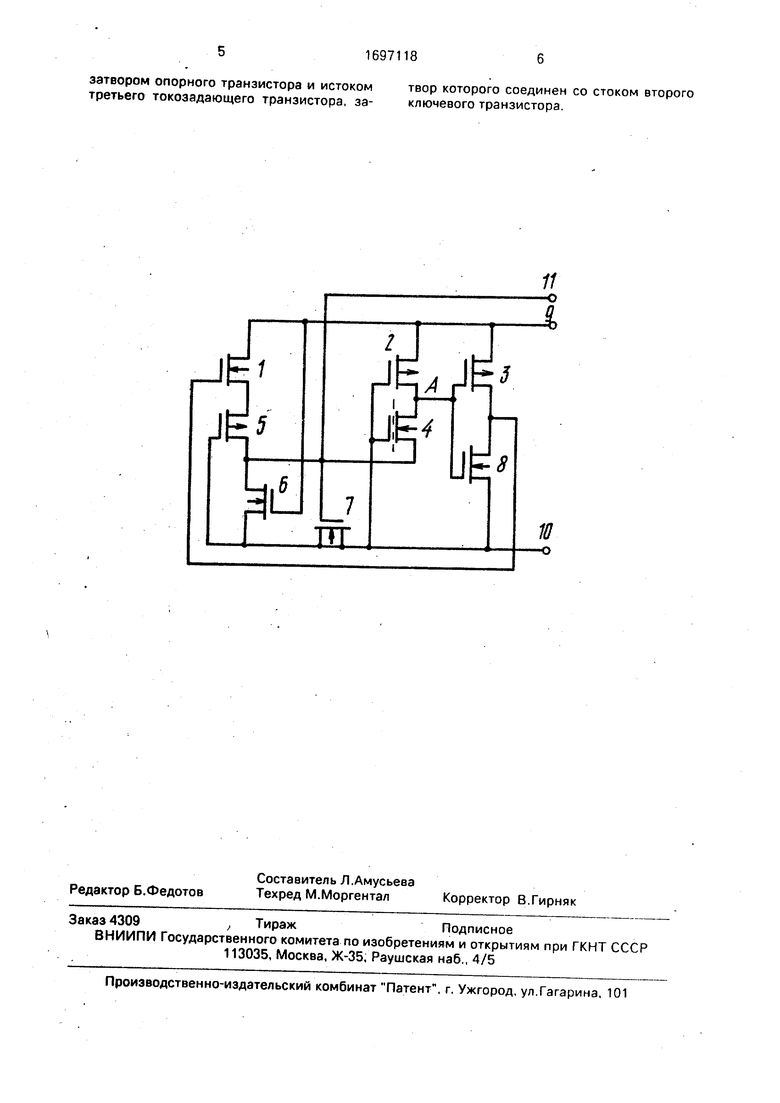

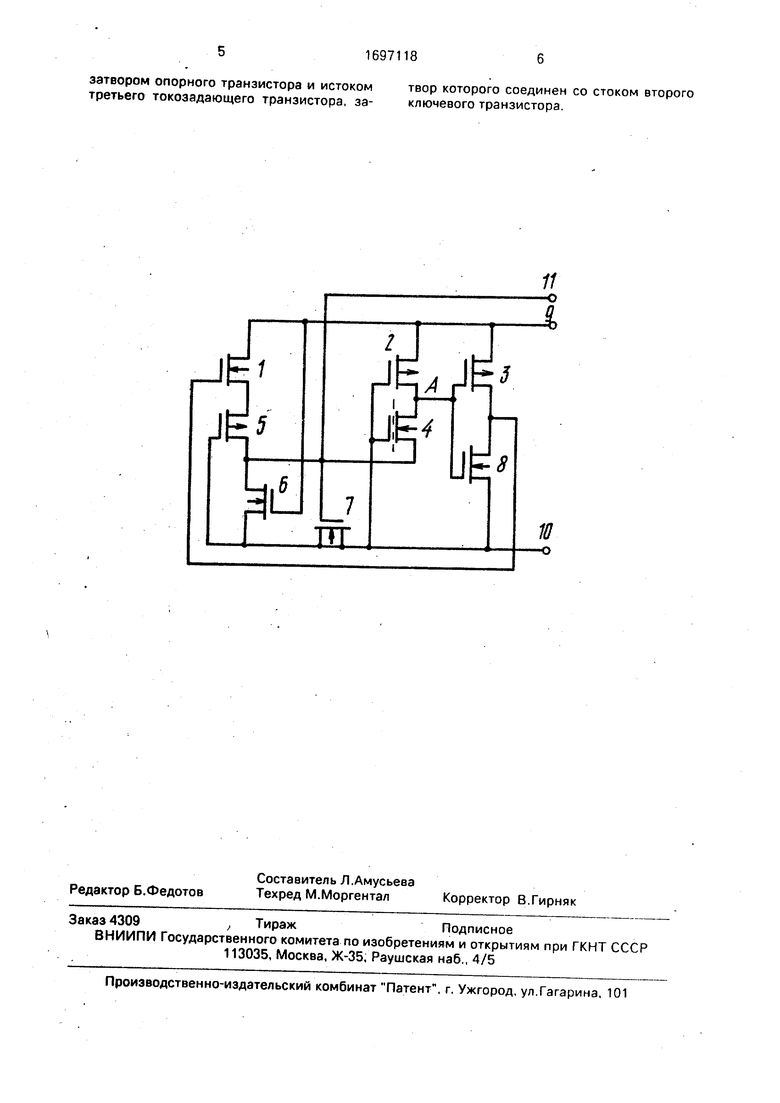

На чертеже представлена электрическая схема формирователя сигналов считывания.

Формирователь содержит второй ключевой транзистор 1 с каналом n-типа, первый токозадающий транзистор 2 с каналом р-типа, третий ключевой транзистор 3 с каналом р-типа, опорный транзистор 4 с кана- лом n-типа, второй токозадающий транзистор 5 с каналом р-типа, третий токозадающий транзистор 6 с каналом п-типа, накопительный транзистор 7 с каналом п- типа, первый ключевой транзистор 8 с каналом n-типа, шину 9 питания, шину 10 нулевого потенциала, выход 11.

Способ считывания информации из элементов памяти на полевых транзисторах заключается в следующем. Элемент памяти представляет собой n-канальный МНОП- транзистор. Для считывания информации из него на сток и затвор подают положительное напряжение относительно подложки, например 2 В и 4 В соответственно, а на исток - напряжение той же полярности, что на затвор и сток. При этом напряжение на истоке элемента памяти является запирающим p-n-переход исток-подложка Это напряжение изменяют пропорционально изменению порогового напряжения элемента памяти. При считывании информации изменение порогового напряжения элемента памяти происходит за счет изменения заряда в обпасти обеднения подложки и не меняет величину информационного заряда

О

о

VI

00

элемента памяти, а также его логическое .состояние. Изменение порогового напряжения элемента памяти ограничено нулевым значением, чтобы исключить ложное считывание информации из соседних невыбранных элементов памяти (на затворе которых напряжение равно нулю), через которые также может протекать ток, если пороговое напряжение этих элементов (в случае использования n-канальной технологии) в результате стирания информации примет отрицательные значения.

При подключении напряжения на исток в запирающем для элемента памяти направлении (т,е. повышающем его пороговое напряжение) его пороговое напряжение увеличивается. При этом низкий уровень порогового напряжения из отрицательного (для n-канальных приборов) становится нулевым.

Способ считывания информации из элементов памяти на полевых транзисторах может быть осуществлен с использованием формирователя сигналов считывания. Формирователь работает следующим образом.

В процессе стирания информации пороговое напряжение опорного транзистора 4 становится отрицательным.

Подбором геометрических размеров транзисторов 2 и 4 добиваются того, что в этом случае потенциал в узле А становится ниже потенциала запирания транзистора 8 и выход 11 начинает заряжаться от шины 9 питания через транзисторы 1,5, причем размером транзистора 5 регулируется ток (постоянная времени заряда выхода 11), С повышением напряжения на выходе 11, а следовательно и на истоке транзистора 4 пороговое напряжение последнего возрастает и при достижении определенной величины становится равным нулю. Транзистор 4 (опорный элемент памяти) закрывается, а потенциал в узле А становится равным напряжению питания, что достаточно для запирания транзистора 3.

В результате этого потенциал выхода 11 начинает понижаться за счет разряда емкости транзистора 7 через открытый канал транзистора 6. Ток разряда (постоянная времени разряда) регулируется подбором геометрических размеров транзистора 6. Как только напряжение навыходе 11 достигнет величины, достаточной для отпирания транзистора 4. потенциал в узле А понижается, и емкость выхода 11 снова начинает заряжаться, т.е. напряжение на выходе 11 начинает возрастать. Таким образом, величина напряжения выхода 11 поддерживается на некотором заданном уровне, определяемом уровнем порогового напряжения транзистора 4,

Выход 11 подключается схемой управления к истокам запоминающих элементов матрицы накопителя в режиме считывания. Формула изобретения

51. Способ считывания информации из

элементов памяти на полевых транзисторах, включающий формирование на электродах затвора и стока элемента памяти постоянных уровней напряжения относи10 тельно напряжения на подложке и определение информации, хранящейся в элементе памяти, по величине тока, протекающего через элемент памяти, отличающийся тем, что, с целью повышения надежности

15 считывания информации, одновременно с формированием постоянных уровней напряжения на электродах стока и затвора элемента памяти на электрод истока элемента памяти подают напряжение той же

20 полярности относительно напряжения на подложке, что и на электроды стока и затвора элемента памяти, изменяют напряжение на электроде истока элемента памяти пропорционально изменению порогового на25 пряжения элемента памяти до достижения им нулевого значения.

2. Формирователь сигналов считывания, содержащий первый и второй ключевые транзисторы с каналом n-типа, третий

30 ключевой транзистор с каналом р-типа, первый и второй токоэадающие транзисторы с каналом р-типа, третий токозадающий транзистор с каналом n-типа, накопительный транзистор с каналом n-типа, опорный тран35 зистор с каналом n-типа, сток которого соединен с затворами первого и третьего ключевых транзисторов и стоком первого токозадающего транзистора, исток которого соединен с истоком третьего ключевого

40 транзистора и подключен к шине питания формирователя, а затвор соединен с затвором опорного ключевого транзистора, сток третьего ключевого транзистора соединен со стоком первого ключевого транзистора,

45 исток которого подключен к шине нулевого потенциала формирователя и соединен с истоком накопительного транзистора и истоком третьего токозадающего транзистора, сток которого соединен со стоком второго

50 токозадающего транзистора, затвор которого соединен со стоком накопительного транзистора, отличающийся тем, что сток и затвор второго ключевого транзистора соединены с истоком и стоком третьего

55 ключевого транзистора соответственно, а исток соединен с истоком второго токозадающего транзистора, сток которого соединен 6 истоком опорного транзистора, затвором накопительного транзистора и является выходом формирователя, а затвор соединен с

затвором опорного транзистора и истоком третьего токозадающего транзистора, затвор которого соединен со стоком второго ключевого транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов записи | 1986 |

|

SU1381594A2 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Формирователь напряжения записи | 1989 |

|

SU1681334A1 |

| Формирователь импульсов записи | 1985 |

|

SU1297114A1 |

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Формирователь импульсов записи | 1986 |

|

SU1339651A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при разработке репрог- раммируемых постоянных запоминающих устройств большой информационной емкости. Цель изобретения - повышение надежности считывания информации, Поставленная цель достигается подачей сигналов управления считывания на исток в запирающем для элемента памяти направлении и изменением их амплитуды пропорционально изменению уровня порогового элемента памяти до достижения им нулевого значения и обеспечивается расширением области допустимых значений порогового напряжения, исключением из состава ячейки памяти адресного транзистора. 1 з.п.ф- лы, 1 ил.

№

11

-О

1

Jg

7

387

-о

| Электроника, 1981, N 4, с | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Электроника, 1981, № 9, с | |||

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Авторское свидетельство СССР № 1200333, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-12-07—Публикация

1989-05-22—Подача