(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель постоянного запоминающего устройства с электрической записью информции | 1973 |

|

SU466552A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Ячейка памяти статического оперативного запоминающего устройства с радиоактивным источником питания | 2021 |

|

RU2777553C1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Формирователь импульсов записи | 1985 |

|

SU1297114A1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

I

Изобретение относится к мшсроэпект- ронике, а именно к конструированию микросхем памяти с электрической записью информации на МОП-транзистгорах.

Известны устройства, выполненные в виде интегральных схем на МОП-транзисторах, Где информация представлена зарядом на плавающем затворе. Эти устройства представляют собой матрицу координатных шин Ч и М , в узлах которых включены -транзисторы выборки, соединенные последовательно с запоминающими транзисторами. Запоминание информации основано на лавинно-инжекционном пробое стокового р - и перехода С11

и 1:21.

Недостатком указанных устройств является трудность записи информации в и -канальных устройствах из-за низкой эффективности инжекиии дЫрок.

Наиболее близким по технической сушности к предлагаемому является постоянное запоминающее устройство с электрической записью информации СЗЗ .

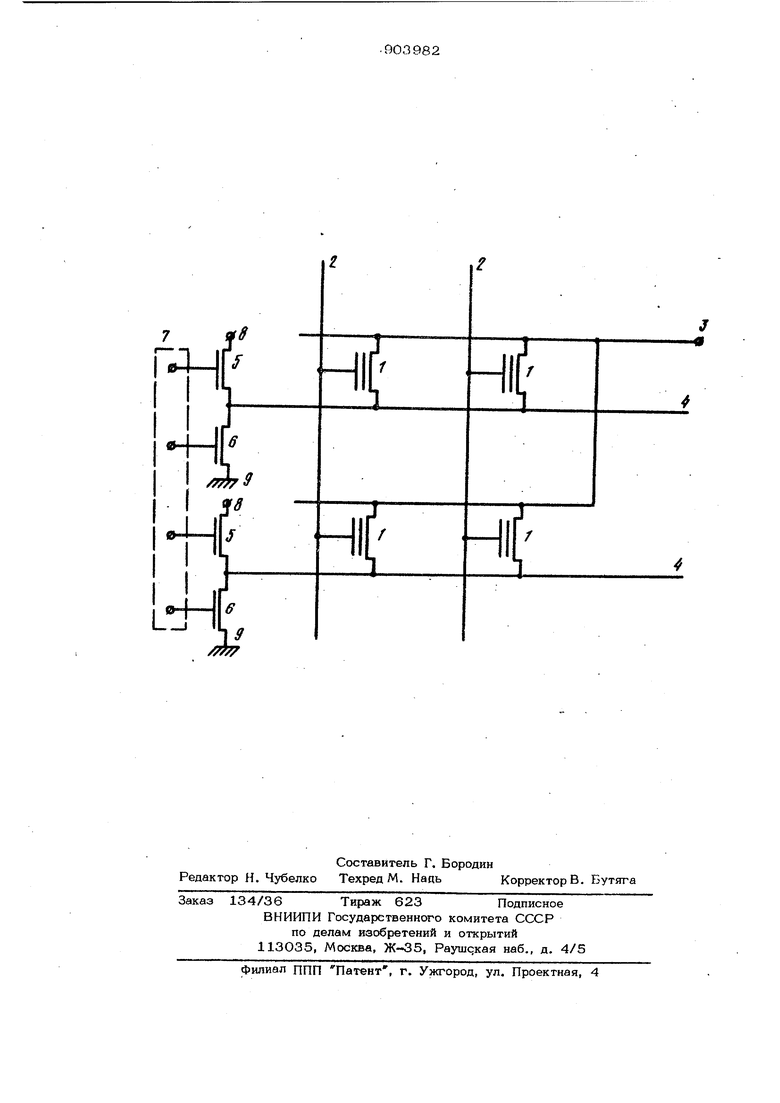

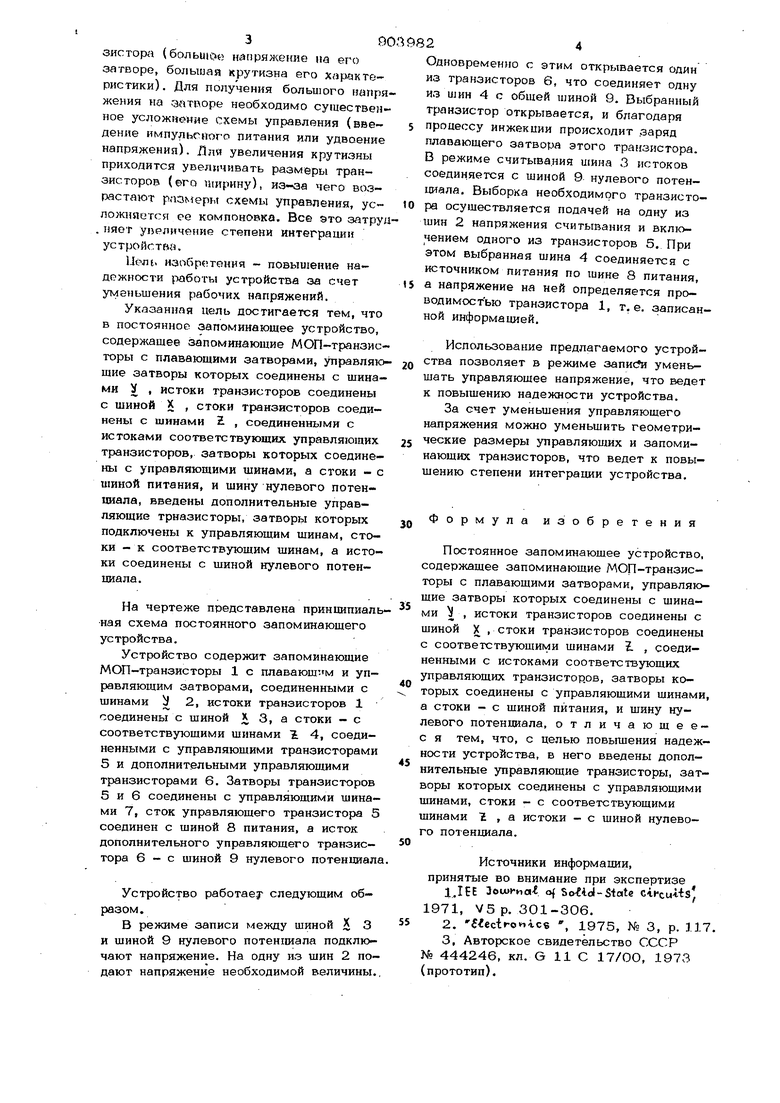

В этом устройстве запоминающие МОП-транзисторы имеют дополнительные управляющие затворы, соединенные с шинами нaкqпитeля, а их стоки соединены с ишнами X . Истоки всех запоминающих транзисторов объединены. При выборке координатной шины, в частности шины X стоков, дешифратор открывает соответствующий управляющий транзистор, который подает иапряжение на выбранную шину. При этом на шину X должен поступать ток, величина которого определяется рядом факторов и не практике составляет обычно несколько миллиампер. Это требует, чтобы выходное сопротивление управляющего транзистора было небольшим. В то же время управляющий транзистор работает с очень сильной отрицательной обратной связью по истоку, так как его нагрузка (запоминающие транзисторы) включены в его исток. Это приводит к необходимости применять специальные меры йля достижения небольшого выходного сопротивления управляющего транзистора (больиюй напряжение на его затворе, большая крутизна его характеристики). Для получения большого напря жения на -эатроре необходимо существенное усложнение схемы управления (введение импульсного питания или удвоение напряжения). Лля увеличения крутизны приходится увеличивать размеры транзисторов (его ширину), из-за чего возрастают схемы управления, усложняется ее компоновка. Все это затруд . няет у15елнчение степени интеграции устройствй. Шлл1. изобретения - повыиюиие надежности таботы устройства за счет уменьшения рабочих напряжений. Указанная цель достигается тем, что в постоянное эапоминаюшее устройства, содержащее запомт1ающие МОП-транзисторы с плавающими затворами, управляю шие затворы которых соединены с шинами V , истоки транзисторов соединены с шиной X , стоки транзисторов соединены с шинами Е , соединенными с истоками соответствующих управляющих транзисторов, затворы которых соединены с управляющими шинами, а стоки - с шиной питания, и шину нулевого потенциала, введены дополнительные управляющие трназисторы, затворы которых подключены к управляющим шинам, стоки - к соответствующим шинам, а истоки соединены с шиной нулевого потенциала. На чертеже представлена принципиаль ная схема постоянного запоминающего устройства. Устройство содержит запоминающие МОП-транзисторы 1 с плавающ-м и управляющим затворами, соединенными с шинами 2, истоки транзисторов 1 соединены с шиной i 3, а стоки - с соответствующими шинами t 4, соединенными с управляющими транзисторами 5 и дополнительными управляющими транзисторами 6, Затворы транзисторов 5 и 6 соединены с управляющими шинами 7, сток управляющего транзистора 5 соединен с шиной 8 питания, а исток дополнительного управляющего транзистора 6 - с шиной 9 нулевого потенциал Устройство работаем следующим образом. В режиме записи между шиной J 3 и шиной 9 нулевого потенциала подключают напряжение. На одну иэ шин 2 подают напряжение необходимой величины 90 24 Одновременно с этим открывается один из транзисторов 6, что соединяет одну из шин 4 с обшей шиной 9. Выбранный транзистор открывается, и благодаря процессу инжекиии происходит заряд плавающего затвора этого транзистора. В режиме считывания шина 3 истоков соединяется с шиной 9 нулевого потенциала. Выборка необходимого транзистора осуществляется подачей на одну из шин 2 напряжения считывания и включением одного из транзисторов 5. При этом выбранная шина 4 соединяется с источником питания по шине 8 питания, а напряжение на ней определяется проводимостью транзистора 1, т. е, записанной информацией. Использование предлагаемого устройства позволяет в режиме записки уменьшать управляющее напряжение, что ведет к повышению надежности устройства. За счет уменьшения управляющего напряжения можно уменьшить геометрические размеры управляющих и запоминающих транзисторов, что ведет к повышению степени интеграции устройства. Формула изобретения Постоянное запоминающее устройство, содержащее запоминающие МОП-транзисторы с плавающими затворами, управляющие затворы которых соединены с шинами , истоки транзисторов соединены с шиной X , стоки транзисторов соединены с соответствующими шинами 2. , соединенными с истоками соответствующих управляющих транзистор.ов, затворы которых соединены с управляющими шинами, а стоки - с шиной питания, и шину нулевого потенциала, отличающеес я тем, что, с целью повышения надежности устройства, в него введены дополнительные управляющие транзисторы, затворы которых соединены с управляющими щинами, стоки - с соответствующими шинами 1 , а истоки - с шиной нулевого потенциала. Источники информации, принятые во внимание при экспертизе 1,1БЕ ЗоюИиа-б о{ So tof-Sinte Cthtu-itS 1971, V5 р, 301-306, 2,ггеагонгсв , 1975, № З, р. 117, 3,Авторское свидетельство СССР МЬ 444246, кл. G 11 С 17/ОО, 1973 (прототип).

Г4-1К

J

tf

I

4

Авторы

Даты

1982-02-07—Публикация

1980-06-06—Подача