1

Изобретение относится к вычислительной технике, а именно к запо/линаетцимустройствам, и может быть использовано .для повышения быстродействия статических ЗУ.

Известны динамические запоминающие устройства (ЗУ), в которых осуществляется предварительный заряд шин накопителя, а при поступлении кода ёшреса все невыбранные шины разряжаются 1. ,

Однако для указанного устройства характерно недостаточное быстродействие при считывании, что связано с тем, что напряжение предзаряда шин ниже напряжения источника питания на величину порогового напряжения транзисторов предзаряда.

Наиболее близким по технической сущности к предлагаемому является статическое ЗУ, соде ржа1цее адресные .усилители, дешифраторы и накопитель. В таком устро(4стве в качестве нагрузочных транзисторов используются транзисторы с встроенным,каналом, что обеспечивает равенство уровня логической единицы напряжению источника питания 2.

Недостатком известного устройства явяяetcя ограниченное а 1стродействие

что связано с тем, что время заряда шин дешифратора и накопителя определяется сопротивлением нагрузочных транзисторов адресного усилителя и

:дешифраторов однако величина нагрузочных транзисторов определяется параметрами ключевого транзистора, а размеры ключевых транзисторов накопителя и дешифраторов ограничены.

10 Кроме того, статическое ЗУ имеет

. большую мощность потребления..

Цель изобретения - увеличение быстродействия и снижение потребляемой мощности устройства.

15

Поставленная цель достигаетсятем, что полупроводниковое запоминающее, устройство, содержащее адресные уси20 лители, выходы которых соединены с входами первого и второго ; ешифраторов, выходы которых соединены с соответствую1Цими шинами ю борки накопителя, дополнительно содержит , ключи, одни выходы которых соедине25ны, с шиной нулевого потенциала, другие - с дополнит ель н11ми выходами адресных усилителей первого и второго дешифраторов и накопителя., управляющие входы ключей являются уп30равлянцими в ход гили устройства.

Кроме того,адресные усилители содержат нагрузочные транзисторы, стоки которых прдключены к шине питания, истоки соединены со стоками ключевых транзисторов и являются выходами усилителя, истоки ключевых транзисторов объединены и являются дополнительными выходами усилителей, затворы нагрузочных транзисторов являются соответствующими управлякяцими входами усилителя.

При этом дешифратора содержат ключевые транзисторы, истоки которых Об

единены, затворы объединены и являются входами дешифраторов, стоки соединены с истоками нагрузочных транзисторов, стоки которых подключены к шине питания, затворы нагрузочных транзисторов являются соответствующими управляющими входами дешифратора ,

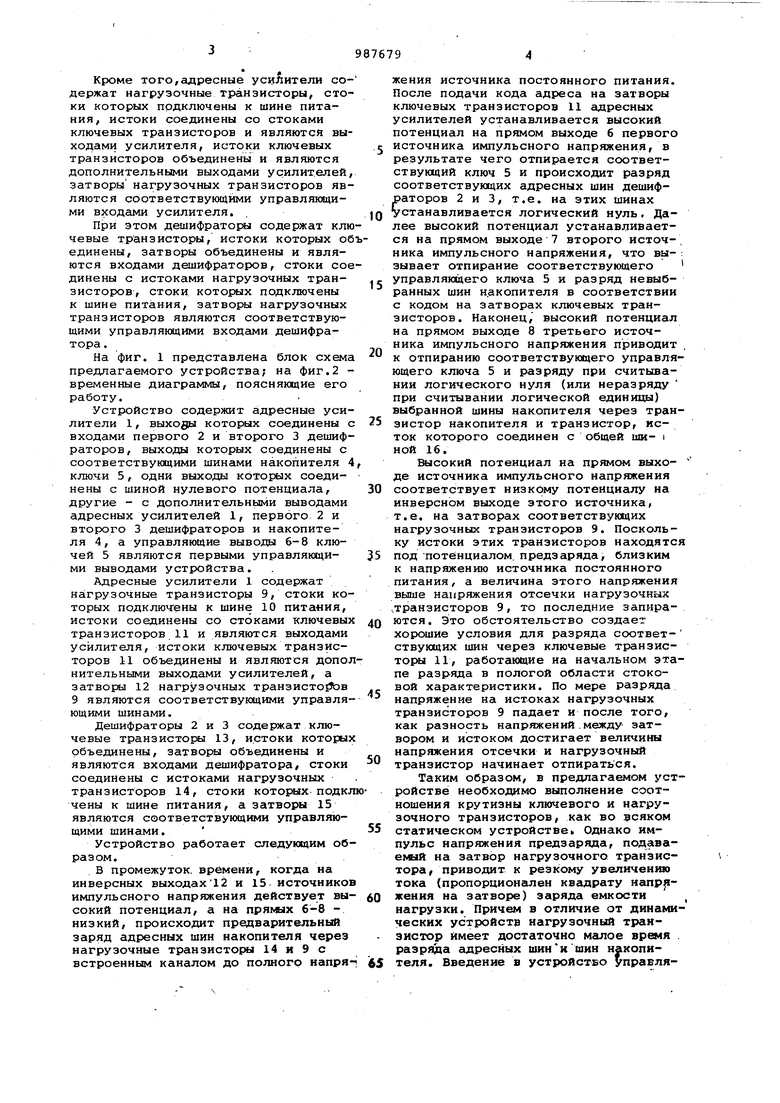

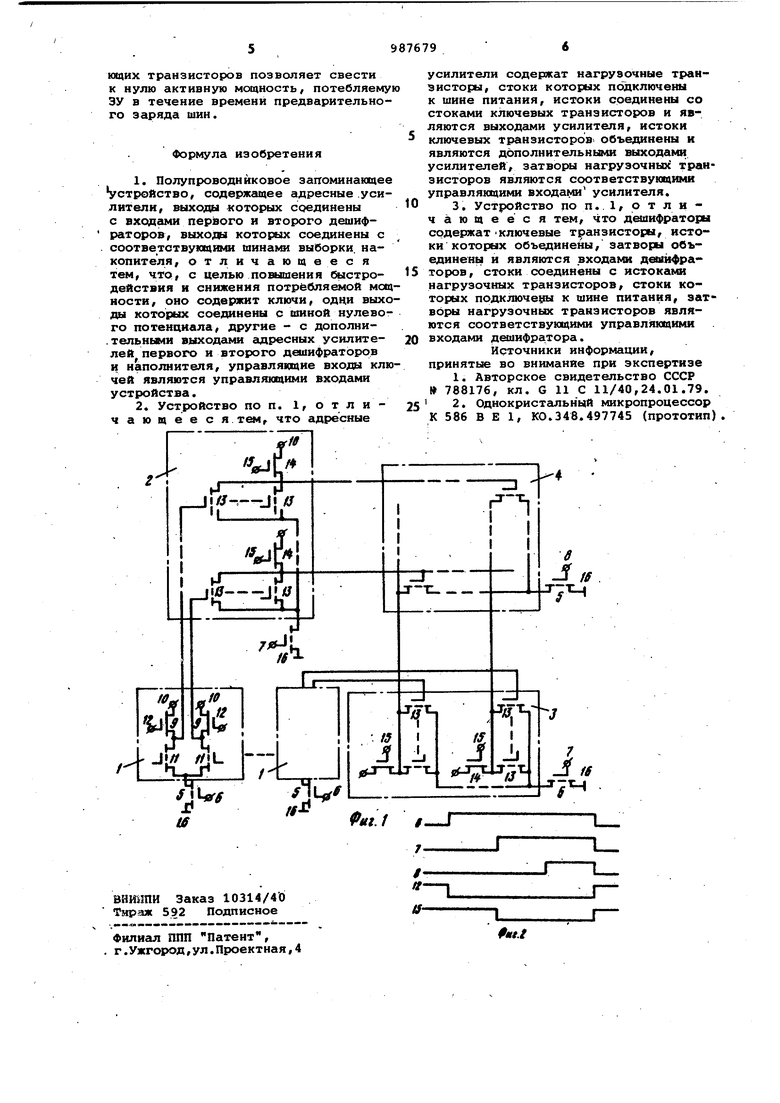

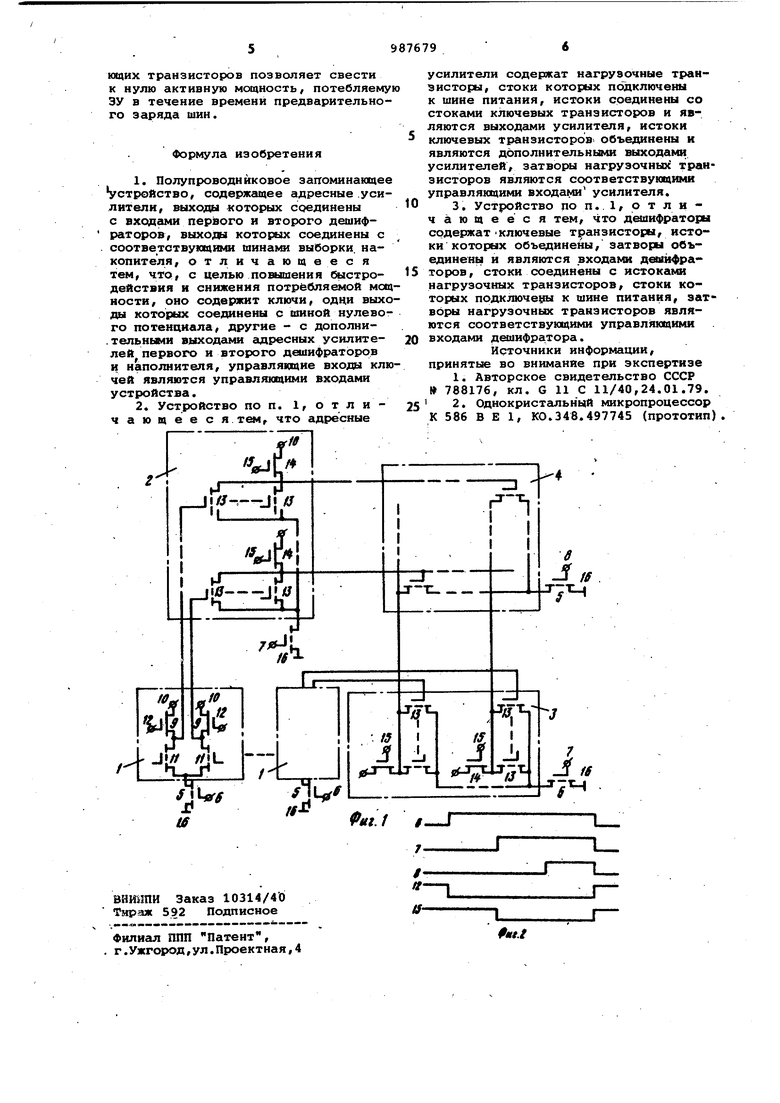

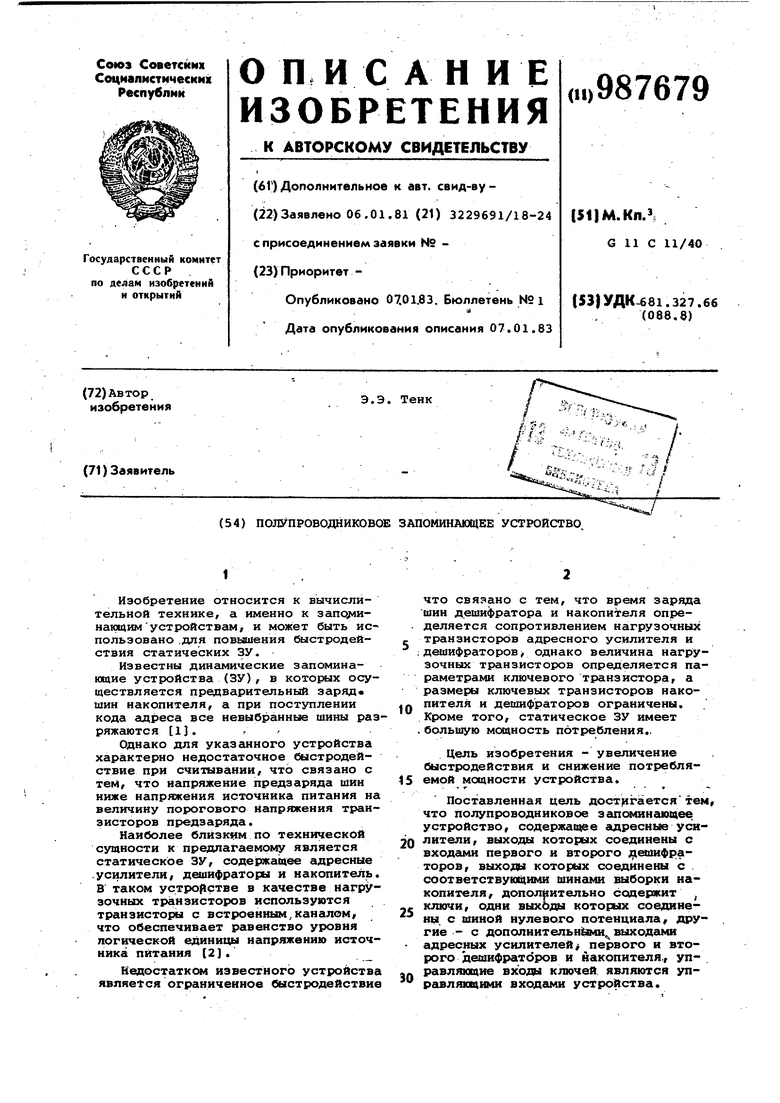

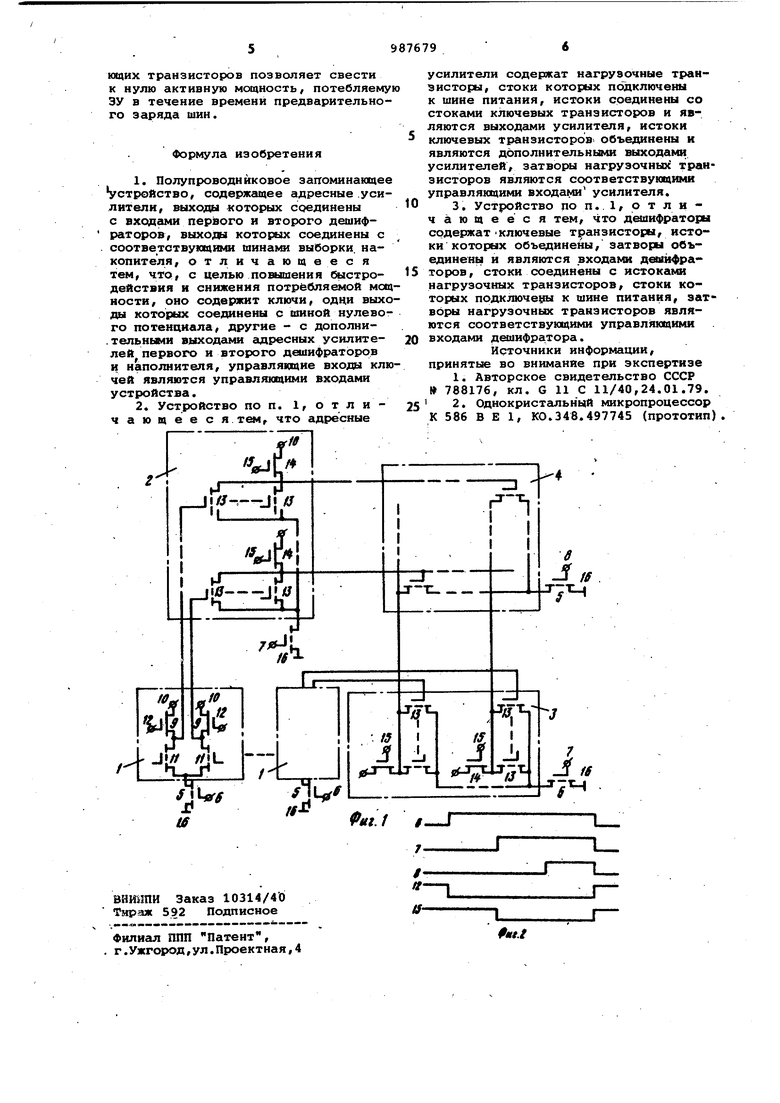

На фиг. 1 представлена блок схема предлагаемого устройства; на фиг.2 временные диаграммы, поясняющие его работу.

Устройство содержит адресные усилители 1, выходы которых соединены с входами первого 2 и второго 3 дешифраторов, выходы которых соединены с соответствующими шинами накопителя 4 ключи 5, одни выходы которых соединены с шиной нулевого потенциала, другие - с дополнительными выводами адресных усилителей 1, первого 2 и второго 3 дешифраторов и накопителя 4, а управляющие выводы 6-8 ключей 5 являются первыми управляющими выводами устройства.

Адресные усилители 1 содержат нагрузочные транзисторы 9, стоки которых подключены к шине 10 питания, истоки соединены со стоками ключевых транзисторов 11 и являются выходами усилителя, истоки ключевых транзисторов 11 объединены и являются дополнительными выходами усилителей, а затворы 12 нагрузочных транзистора 9 являются соответствуквдими управляющими шинами.

Дешифраторы 2 и 3 содержат ключевые транзисторы 13, истоки которых объединены, затворы объединены и являются входами дешифратора, стоки соединены с истоками нагрузочных транзисторов 14, стоки которлх-подкл чены к шине питания, а затворы 15 являются соответствующими управляющими шинами.

Устройство работает следующим образом.

В промежуток, времени, когда на инверсных выходах12 и 15 источников импульсного напряжения действует высокий потенциал, а на прямых 6-8 низкий, происходит предварительный заряд адресных шин накопителя через нагрузочные транзисторы 14 и 9 с встроенным каналом до полного напряжения источника постоянного питания. После подачи кода адреса на затворы ключевых транзисторов 11 адресных усилителей устанавливается высокий потенциал на прямом выходе 6 первого источника импульсного напряжения, в результате чего отпирается соответствующий ключ 5 и происходит разряд соответствующих адресных шин дешифраторов 2 и 3, т.е. на этих шинах устанавливается логический нуль, Далее высокий потенциал устанавливается на прямом выходе7 второго источника импульсного напряжения, что вызывает отпирание соответствующего управляющего ключа 5 и разряд невыбранных шин накопителя в соответствии с кодом на затворах ключевых транзисторов. Наконец, высокий потенциал на прямом выходе 8 третьего источника импульсного напряжения приводит к отпиранию соответствующего управляющего ключа 5 и разряду при считывании логического нуля (или неразряду при считывании логической единицы) выбранной шины накопителя через транзистор накопителя и транзистор, исток которого соединен с общей ши- i ной 16.

Высокий потенциал на прямом выходе источника импульсного напряжения соответствует низкому потенциалу на инверсном выходе этого источника, т.е. на затворах соответствующих нагрузочных транзисторов 9. Поскольку истоки этих транзисторов находятс под потенциалом, предзаряда, близким к напряжению источника постоянного питания, а величина этого напряжения выше напряжения отсечки нагрузочных ..транзисторов 9, то последние запираются. Это обстоятельство создает хорошие условия для разряда соответствуюдих шин через ключевые транзисторы 11, работающие на начальном этапе разр-яда в пологой области стоковой характеристики. По мере разряда напряжение на истоках нагрузочных транзисторов 9 падает и после того, как разность напряжений.между затвором и истоком достигает величины напряжения отсечки и нагрузочный транзистор начинает отпираться.

Таким образом, в предлагаемом устройстве необходимо выполнение соотношения крутизны ключевого и нагрузочного транзисторов, как во эсяком статическом устройстве Однако импульс напряжения предзаряда, подаваемый на затвор нагрузочного транзистора, приводит к резкому увеличению тока (пропорционален квгщрату Hanpjiжения на затворе) заряда емкости нагрузки. Причем в отличие от динамических устройств нагрузочный транзистор имеет достаточно малое время разрада адресных шини шин накопителя. Введение в устройство управляющих транзисторов позволяет свести к нулю активную мсяциость/ потебляем ЗУ в течение времени предварительно го заряда шин. Формула изобретения 1. Полупроводниковое запоминающе устройство, содержащее адресные .уси лители, выходы которых соединены с входами первого и второго дешифраторов, выходы которых соединены с соответствуищими шинами выборки, накопителя, отличающееся тем, что, с целью пошлиения быстродействия и снижения потребляемой мо ности, оно содержит ключи, одци вых да которых соединены с шиной нулево го потенциала, другие - с дополни.тельными выходами адресных усилителей первого и второго дешифраторов и исполнителя, управляющие входы кл чей являются управляющими входами устройства. 2. Устройство по п. 1,отлич а ю щ е е с я тем, что адресные

Й1 усилители содержат нагрузочные транзисторы, стоки которых подключены к шине питания, истоки соединены со стоками ключевых транзисторов и являются выходами усилителя, истоки ключевых транзисторов объединены и являются дополнительными выходами усилителей, затворов нагрузочных транзисторов являются соответствующими управляющими входами усилителя. 3. Устройство по п..1, о т л и чающееся тем, что деаифраторы содержат ключевые транзисторы, истоки которых объединены, затворы объединены и являются входами дешифраторов , стоки соединены с истоками нагрузочных транзисторов, стоки которых подк вочерд к шине питания, затворы нагрузочных транзисторов являются соответствующими управляющими входами дешифра.тора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 788176, кл. G 11 С 11/40,24.01.79. 2. Однокристсшьный микропроцессор К 586 В Е 1, КО.348.497745 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Постоянное запоминающее устройство | 1988 |

|

SU1594603A1 |

| Полупроводниковое запоминающее устройство | 1979 |

|

SU879651A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Дешифратор на МДП-транзисторах | 1983 |

|

SU1455362A1 |

Авторы

Даты

1983-01-07—Публикация

1981-01-06—Подача