(5) УСТРОЙСТВО для КОНТРОЛЯ и КОРРЕКЦИИ АДРЕСНЫХ СИГНАЛОВ ДЛЯ ПАМЯТИ ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции адресных сигналов в памяти последовательного действия | 1982 |

|

SU1023399A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Устройство поиска и контроля адреса страницы для доменной памяти | 1983 |

|

SU1095242A1 |

| Устройство для контроля накопителей | 1982 |

|

SU1048521A1 |

| Устройство для детектирования манипулированных по частоте и фазе сигналов воспроизведения цифровой магнитной записи | 1986 |

|

SU1327172A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Система числового программного управления с постоянной скоростью резания для токарно-винторезных станков | 1981 |

|

SU978102A1 |

I

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля адресных сигналов, которое содержит регистр адреса, шифратор и схему сравнения. В этом устройстве контроль правильности обращения по заданному адресу осуществляется путем сравнения контрольного кода адреса по некоторому модулю, поступающему одновременно с кодом адреса на регистр адреса, с контрольным кодом адреса, полученным на выходе шифратора кода адреса С13.

Недостатком известного устройства является большой объем аппаратуры и невозможность коррекции неправильно выбранного адреса.

Наиболее близким к предлагаемому является устройство для контроля выборки адресов, содержащее последовательно соединенные формирователь продвигающих импульсов, регистр синхроимпульсов, усилитель считывания синхроимпульсов, счетчик синхроимпульсов, блок сравнения, второй вход которого соединен с выходом регистра адреса, и блок местного управления, причем выход формирователя .продвигающих импульсов соединен также последовательно с маркерным регистром, усилителем считывания маркера и со вторым входом счетчика синхв роимпульсов С2.

Недостатком известного устройства является отсутствие контроля правильности выбора адреса и невозможность его коррекции, что снижает надежность устройства.

Цель изобретения - повышение надежности устройства.

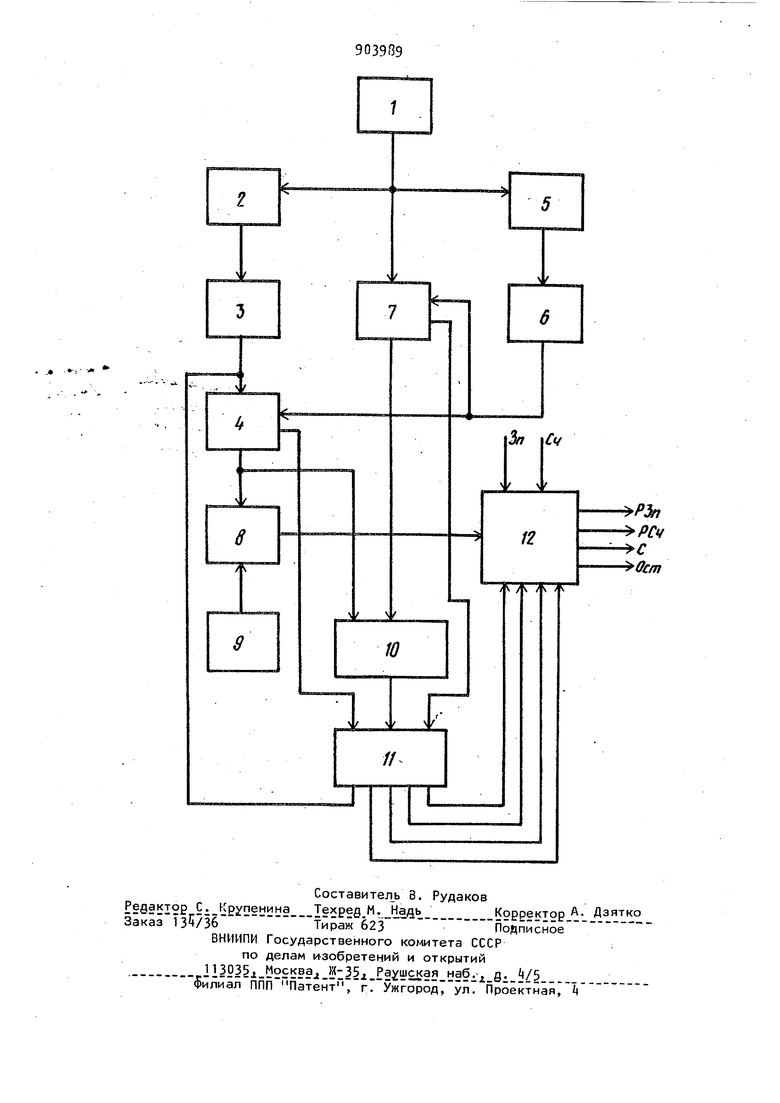

.Поставленная цель достигается тем, jQ что в устройство для контроля и коррекции адресных сигналов для памяти последовательного действия, содержащее регистр адреса, формирователь продвигающих импульсов, регистр маркера, регистр синхроимпульсов, усилитель синхроимпульсов, усилитель маркерных игчпульсов, счетмик синхроимпульсов, первую схему сравнения и блок управления, причем выход формиро вателя продвигающих импульсов подключен ко входам регистра синхроимпульсов и регистра маркеров, выходы которых подключены соответственно ко входам усилителя синхроимпульсов и усилителя маркерных сигналов, выходы которых соединены соответственно с первым и вторым входами счетчика синх роимпульсов, входы первой схемы сравнения соединены соответственно с первым выходом счетчика синхроимпульсов и выходом регистра адреса а выход подключен к одному из входов бло ка управления, введены дешифратор. вторая схема сравнения и счетчик про двигающих импульсов, входы которого подключены- соответственно к выходам усилителя маркерных импульсов и формирователя продвигающих импульсов, выходы - к первым входам второй схемы сравнения и дешифратора, второй и третий входы которого соединены соответственно с выходом второй схемы сравнения и вторым выходом счетчика синхроимпульсов, одни из выходов дешифратора являются управляющими выходами устройства, другой выход подклю чен к первому входу счетчика синхроимпульсов, первый выход которого под ключен ко второму входу второй схемы сравнения. На чертеже приведена структурная схема предлагаемого устройства. Устройство содержит формирователь 1 продвигающих импульсов, регистр 2 синхроимпульсов, усилитель 3 синхроимпульсов, счетчик k синхроимпульсов, регистр 5 маркера, усилитель 6 маркерных импульсов, счетчик продвигающих импульсов, первую схему 8 сравнения, регистр 9 адреса, вторую схему 10 сравнения, дешифратор 11 и блок 12 управления. Входы счетчика 7 подключены соответственно к выходам усилителя б и формирователя 1, а выходы - к первым входам схемы 10 сравнения и дешифратора 11, второй вход которого соединен с выходом схемы 10 сравнения, второй вход которой подключен к первому выходу счетчика , второй выход которого соединен с третьим входом дешифратора 11. Одни из выходов дешифратора 11 являютcq управляющими 90 4 выходами устройства (соединены со входами блока 12), другой выход подключен к первому входу счетчика Ц, второй вход которого соединен с выходом усилителя 6. Устройство работает следующим образом. Перед началом работы счетчики Ц и 7 находятся в нулевом состоянии, а маркер находится на выходе регистра 5- В регистре 9 хранится код адреса числа, с которого следует начать считывание (запись) . При устройства маркерный импульс через усилитель 6 поступает на одни из входов счетчиков А и 7t разрешая прохождение соответствующих импульсов на их другие (счетные) входы. Каждый синхроимпульс соответствует одной адресной позиции, так что состояние счетчика 4 совпадает с адресом числа, которое в данный момент находится в зоне считывания. Этот адрес схемой 8 сравнения сравнивается с адресом, хранимым в регистре 9. При соепадении адресов в счетчике k и регистре 9 схема 8 сравнения выдает сигнал в блок 12, который в свою очередь формирует сигнал разрешения считывания РСц или разрешения записи РЗц в зависимости от установленного режима работы запоминающего устройства (считывание Сц или запись 3ч). Кроме того, блок 12 вырабатывает сигнал С, поступающий в ЦВМ и свидетельствующий о том, что поиск заданного адреса закончен и зaпo инaющee устройство готово к обмену информацией. При.безошибочной работе устройства, описанной выше, схема 10 сравнения и дешифратор 11 не оказывают на не.го влияния. Ошибки в работе запоминающего устройства, существенные с точки зрения взаимодействия его с ЦВМ, связаны со сбоями или отказами регистра 2 или усилителя 3 что приводит, например, к пропаданию синхроимпульса, счетчика синхроимпульсов Ц, счетчика 7 продвигающих импульсов. При этом одновременные отказы нескольких элементов считаются маловероятными . В первом случае состояние счетчи«а i отличается на единицу (в сторону меньших адресов) от состояния счетчика 7 который фиксирует правильный текущий адрес. В связи с этим со схемы 10 сравнения на вход дешифратора поступает сигнал несовпадения кодов. Сигнал ч: соответствующего выхода дешифратора 11 поступает на вход счетчика i, добавляя к его содержимому единицу и тем самым корректируя ошибку.

Во втором случае,при неправильной работе собственно счетчика 4 ошибка обнаруживается схемой встроенного контроля счетчика А (.не показана) и сигнал с выхода счетчика 4 поступает на чход дешифратора 11. Кроме того, срабатывает схема 10 сравнения, сигнал с выхода которой также поступает на вход дешифратора 11 В соответствии с входны н сигнолами, возбуждается один из выходов дешифратора 11 и сигнал поступает на вход блока 12. При ошибочном срабатывании схемы встроенного контроля счетчика k (при этом собственно счетчик 4 работает нормально) схема 10 сравнения не работает и возбуждается другой выход дешифратора 11, сигнал с которого также поступает на вход блока 12.

В третьем случае работа устройства происходит аналогично второму случаю. При неправильной работе счетчи1ка 7 срабатывают схема встроенного контроля счетчика 7 (не показана) и схема 10 сравнения. При ошибочном срабатывании схемы встроенного контроля ее сигнал поступает на вход деширфатора 11. Ссютветствую14ие сигналы дешифратора М подаются в блок 12.

Неправильная работа счетчиков и 7, а также их схем встроенного контроля, не могут быть скорректированы, поэтому в таких случаях блок 12 вырабатывает сигнал останова устройства с одновременной фиксацией неисправного блока..

Таким образом, предлагаемое устройство позволяет повысить надежность выборки адресов в памяти псследова|тельного действия, так как оно не только обнаруживает и локализует ошибки , возникающие в процессе его работы, но и устраняет последствия наиболее вероятных и опасных из них ошибок в работе регистра 2 синхроимпульсов и усилителя 3 синхроимпульсов.

Формула изобретения

Устройство для контроля и коррекции адресных сигналов для памяти последовательного действия, содержащее регистр адреса, формирователь продвигающих импульсов, регистр маркера регистр синхроимпульсов, усилитель синхроимпульсов, усилитель маркерных импульсов, счетчик синхроимпульсов, первую схему сравнения и блок управления, причем выход формирователя продвигающих импульсов подключен ко входам регистра синхроимпульсов и регистра маркеров, выходы которых подключены соответственно ко входам усилителя синхроимпульсов и усилителя маркерных сигналов, выходы которых соединены соответственно с первым и вторым входаьш синхроимпульсов, входы первой схемы сравнения соединены соответственно с nepBbiM выходом счетчика синхроимпульсов и выходом регистра адреса, а выход подключен к одному из входов блока управления, отли чающее с я тем, что, с целью повышения надежности устройства, оно содержит дешифратор, вторую схему сравнения и счетчик продвигающих импульсов, входы которого подключены соответственно к выходам усилителя маркерных импульсов и формирователя продвигающих импульсов, а выходы - к первым входам второй схемы сравнения и дешифратора, второй и третий входы коiToporo соединены соответственно с выходом второй схемы сравнения и вторым выходом счетчика синхроимпульсов одни из выходов дешифратора являются управляющими выходами устройства, другой выход подключен к первому входу счетчика синхроимпульсов, первый выход которого подключен ко бторому входу второй схемы сравнения.

Источники информации, принятые во внимание при экспертизе

:. Патент США К 3270310, кл. .1, опублик. 1966.

гия,

I

v

f f

I t l V / г

t fV

Авторы

Даты

1982-02-07—Публикация

1980-01-28—Подача