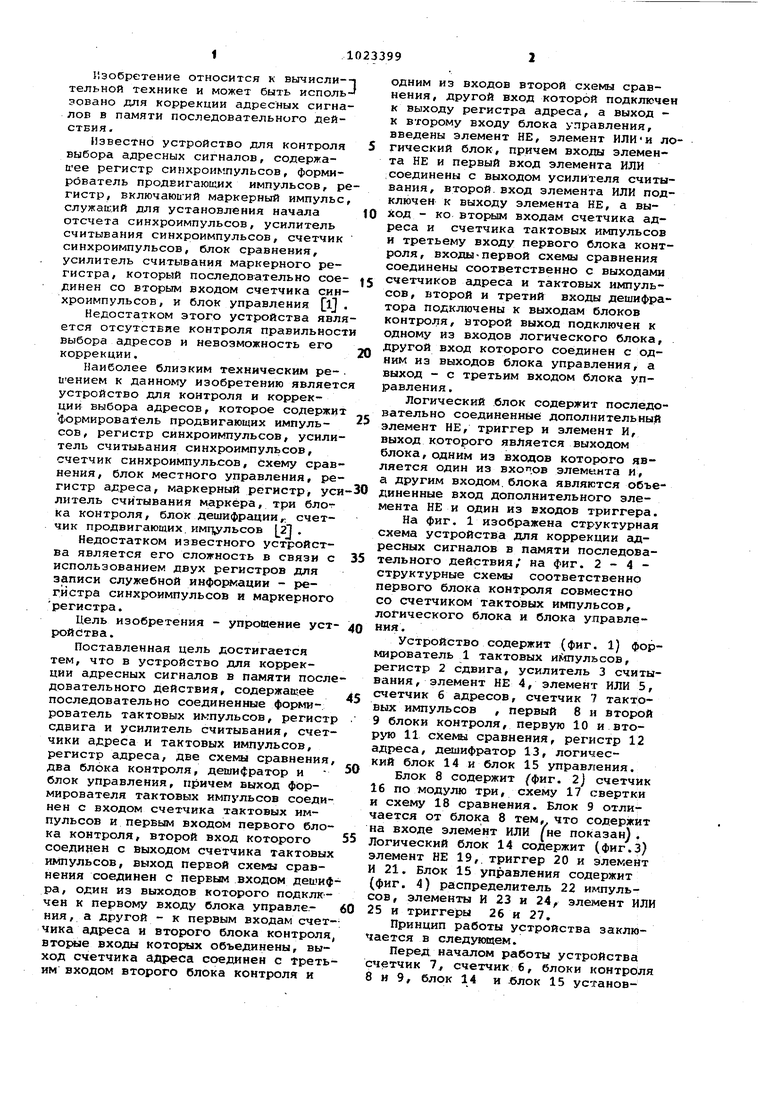

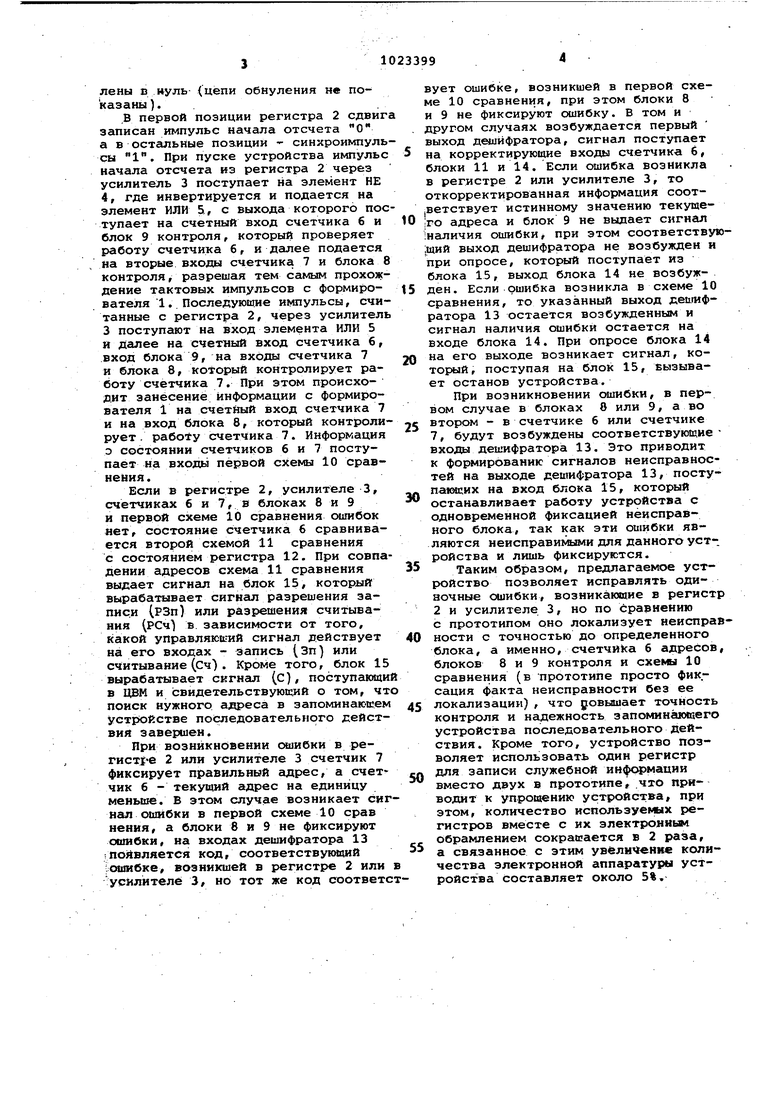

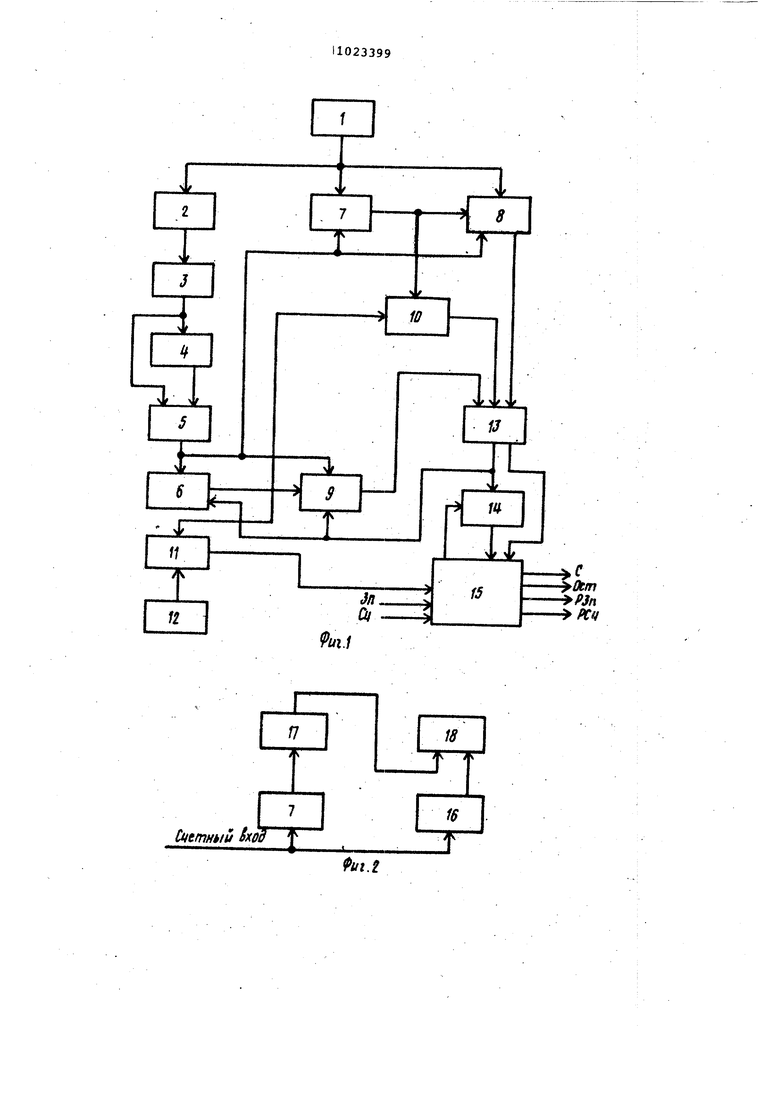

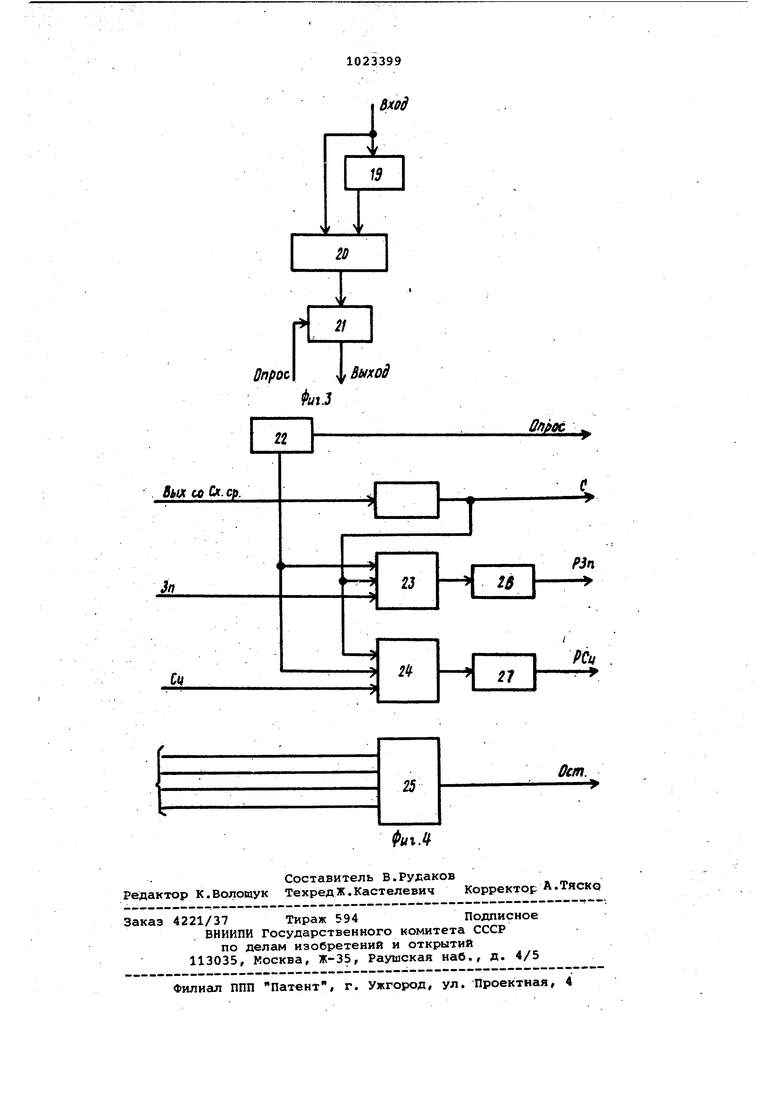

Изобретение относится к вычислительной технике и может быть исполь зовано для коррекции адресных сигна лов в памяти последовательного действия. Известно устройство для контроля выбора адресных сигналов, содержаиее регистр синхроимпульсов, формирователь продвигающих импульсов, р гистр, включаюпий маркерный импульс служащий для установления начала отсчета синхроимпульсов, усилитель считывания синхроимпульсов, счетчик синхроимпульсов, блок сравнения, усилитель считывания маркерного регистра, который последовательно соединен со вторым входом счетчика синхроимпульсов, и блок управления Щ Недостатком этого устройства явля ется отсутствие контроля правильност выбора адресов и невозможность его коррекции. Наиболее близким техническим реьением к данному изобретению являетс устройство для контроля и коррекции выбора адресов, которое содержит формирователь продвигающих импульсов, регистр синхроимпульсов, усилитель считывания синхроимпульсов, счетчик синхроимпульсов, схему сравнения, блок местного управления, регистр адреса, маркерный регистр, уси литель считывания маркёра, три бло-г ка контроля, блок дешифрации,, счетчик продвигающих. имг)ульсов 2Т , Недостатком известного устройства является его сложность в связи с использованием двух регистров для записи служебной информации - регистра синхроимпульсов и маркерного регистра. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в устройство для коррекции адресных сигналов в памяти после довательного действия, содержащее последовательно соединенные формирователь тактовых импульсов, регистр сдвига и усилитель считывания, счетчики адреса и тактовых импульсов, регистр адреса, две схемы сравнения, два блока контроля, дешифратор и блок управления, причем выход формирователя тактовых импульсов соединен с входом счетчика тактовых импульсов и первым входом первого блока контроля, второй вход которого соединен с выходом счетчика тактовых иктульсов, выход первой схемы сравнения соединен с первым входом дешиф ра, один из выходов которого подключен к первому входу блока управления, а другой - к первым входам счет чика адреса и второго блока контроля вторые входы которых объединены, выход счетчика адреса соединен с треть им входом второго блока контроля и одним из входов второй схемы сравнения, другой вход которой подключен к выходу регистра адреса, а выход к второму входу блока управления, введены элемент НЕ, элемент ИЛИи логический блок, причем входы элемента НЕ и первый вход элемента ИЛИ ; соединены с выходом усилителя считывания, второй, вход элемента ИЛИ подключен к выходу элемента НЕ, а выход - ко вторым входам счетчика адреса и счетчика тактовых импульсов и третьему входу первого блока контроля, входы-первой схемы сравнения соединены соответственно с выходами счетчиков адреса и тактовых импульсов, второй и третий входы дешифратора подключены к выходам блоков контроля, второй выход подключен к одному из входов логического блока, . другой вход которого соединен с одним из выходов блока управления, а выход - с третьим входом блока управления . Логический блок содержит последовательно соединенные дополнительный элемент НЕ, триггер и элемент И, выход которого является выходом блока, одним из входов которого является один из вхопов элемента и, а другим входом,блока являются объединенные вход дополнительного элемента НЕ и один из входов триггера. На фиг. 1 изображена структурная схема устройства для коррекции адресных сигналов в памяти последовательного действия, на фиг. 2 - 4 структурные схемы соответственно первого блока контроля совместно со счетчиком тактЬвых импульсов, логического блока и блока управления. Устройство содержит (фиг. 1) формирователь 1 тактовых иКтульсов, регистр 2 сдвига, усилитель 3 считывания, элемент НЕ 4, элемент ИЛИ 5, счетчик 6 адресов, счетчик 7 тактовых импульсов , первый 8 и второй 9 блоки контроля, первую 10 и вторую 11 схемы сравнения, регистр 12 адреса, дешифратор 13, логический блок 14 и блок 15 управления. Блок 8 содержит фиг. 2j счетчик 16 по модулю три, схему 17 свертки и схему 18 сравнения. Блок 9 отличается от блока 8 тем, что содержит на входе элемент ИЛИ pie показан . Логический блок 14 содержит (фнг.З) элемент НЕ 19,. триггер 20 и элемент И 21. Блок 15 управления содержит (фиг. 4) распределитель 22 илшульсов, элементы И 23 и 24 элемент ИЛИ 25 и триггеры 26 и 27, Принцип работы устройства заклюае тся в следукяяем. Перед началом работы устройства счетчик If счетчнк б, блоки контроля 8 и 9, блок 14 и .блок 15 установлены в нуль (цепи обнуления не показаны). ,В первой позиции регистра 2 сдвиг записан импульс начала отсчета О а в остальные поаиции - синхроилотуль сы 1, При пуске устройства импульс начала отсчета из регистра 2 через усилитель 3 поступает на элемент НЕ 4, где инвертируется и подается на элемент ИЛИ 5., с выхода которого по тупает на счетный вход счетчика 6 и блок 9 контроля, который проверяет работу счетчика б, и далее подается на вторые входы счетчика 7 и блока контроля, разрешая тем самым прохож дение тактовых импульсов с формирователя 1. Последующие импульсы, счи танные с регистра 2, через усилител 3 поступают на вход элемента ИЛИ 5 и далее на счетный вход счетчика 6, .вход блока 9, на входы счетчика 7 и блока 8, который контролирует работу счетчика 7 . При этом происходит занесение информации с формирователя 1 на счетный вход счетчика 7 и на вход блока 8, который контроли рует, работу счетчика 7. Информация э состоянии счетчиков 6 и 7 поступает на входы первой схемы 10 сравнения. Если в регистре 2, усилителе 3, счетчиках 6 и 7, в блоках 8 и 9 и первой схеме 10 сравнения сшибок нет, состояние счетчика 6 сравнивается второй схемой 11 сравнения с состоянием регистра 12. При совпа дении адресов схема 11 сравнения выдает сигнал на блок 15, который вырабатывает сигнал разрешения запис.и (РЗп) или разрешения считывания (РСч в зависимости от того, какой управляющий сигнал действует на его входах - запись (,3п) или считывание (Сч). Кроме того, блок 15 вырабатывает сигнал (С), поступающи в ЦВМ и свидетельствующий о том, чт поиск нужного, адреса в запоминающем устройстве последовательного действия завершен. При возникновении сшибки в регистре 2 или усилителе 3 счетчик 7 фиксирует правильный адрес, а счетчик 6 - текущий адрес на единицу меньше. В этом случае возникает сиг нал ошибки в первой схеме 10 срав нения, а блоки 8 и 9 не фиксируют ошибки, на входах дешифратора 13 :появляется код, соответствующий ;:ошибке, возникшей в регистре 2 илн усилителе 3, но тот же код соответс вует ошибке, возникшей в первой схеме 10 сравнения, при этом блоки 8 и 9 не фиксируют ошибку. В том и другом случаях возбуждается первый выход дешифратора, сигнал поступает на корректирующие входа счетчика 6, блоки 11 и 14. Если ошибка возникла в регистре 2 или усилителе 3, то откорректированная информация соот|Ветствует истинному значению текуще;го адреса и блок 9 не выдает сигнал :наличия ошибки, при этом соответствую,щий выход дешифратора не возбужден н при опросе, который поступает из блока 15, выход блока 14 не возбужден. Если ошибка возникла в схеме 10 сравнения, то указанный выход деь.1Ифратора 13 остается возбужденным и сигнал наличия ошибки остается на входе блока 14. При опросе блока 14 на его выходе возникает сигнал, который, поступая на блок 15, вызывает останов устройства. При возникновении сяиибки, в первом случае в блоках О или 9, а во втором - в счетчике 6 или счетчике 7, будут возбуждены соответствующиевходы дешифратора 13. Это приводит к формированию сигналов неисправностей на выходе дешифратора 13, постуnairacHX на вход блока 15, который останавливает работу устройства с одновременной фиксацией неисправного блока, так как эти ошибки являются неисправишоли для данного уст-, ройства и лишь фиксируются. Таким образом, предлагаемое устройство позволяет исправлять одиночные сшибки, возникающие в регистр 2 и усилителе 3, но по сравнению с прототипом оно локализует неисправности с точностью до определенного блока, а именно, счетчика 6 адресов, блоков 8 и 9 контроля и схемы 10 сравнения (в прототипе просто фиксация факта неисправности без ее локализации), что ровышает точность контроля и надежность запоминающего устройства последовательного действия. Кроме того, устройство позволяет использовать один регистр для записи служебной инф фмацни вместо двух в прототипе, .что приводит к упрощению устройства, при этом, количество используемых регистров вместе с их электронным Обрамлением сокращается в 2 раза, а связанное с этим увеличение количества электронной аппаратуры устройства составляет около 5%,

/7

18

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и коррекции адресных сигналов для памяти последовательного действия | 1980 |

|

SU903989A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Устройство для управления блокомпАМяТи | 1978 |

|

SU809345A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Устройство для воспроизведения псевдообъемного изображения | 1984 |

|

SU1233302A1 |

1. УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ АДРЕСНЫХ СИГНАЛОВ В ПАМЯТИ ПО:ЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ, содержащее последовательно соединенные формирователь тактовых импульсов, регистр сдвига и усилитель считывания счетчики адреса и тактовых импульсов, регистр адреса, две схемы сравнения, два блока контроля, дешифратор и блок управления, причем выход формирователя тактовых импульсов соединен с входом счетчика тактовых импульсов и первым входом первого блока контроля, вход которого соединен с выходом счетчика тактовых импульсОв, выход первой схемы сравнения соединён с первым входом дешифратора, один из выходов которого подключен к входу блока управления а другой - к первым входам счетчика адреса и второго блока контроля, вторые входы которых объединены, выход счетчика адреса соединен с третьим входом второго блока контроля и с одним из входов второй схемы сравнения, другой вход которой ; подключен к выходу регистра адреса, а выход - к второму входу блока управления, отличают е е ,с я тем, что, с целью упрощения устройства, в него введены элемент НЕ, элемент ИЛИ и логический блок, причем входы элемента НЕ и первый вход элемента ИЛИ соединены с выходом усилителя считывания, второй вход элемента ИЛИ подключен к выходу элемента НЕ, а выход - к вторым входам счетчика адреса и счетчика тактовых импульсов и третьему входу первого блока контроля, входы первой схемы сравнения соединены соответственно с выходами счетчиков адреса и тактовых импульсов, второй и третий входы СП дешифратора подключены к выходам блоков контроля, второй выход подклю F чен к одному кз входов логического блока, вход которого соединен с одним из выходов блока управления, а выход - с третьим входом блока управления. : 2. Устройство по п. 1, отлиIN: чающееся тем, что логичесCri ОС кий блок содержит последовательно соединенные дополнительный элемент НЕ, триггер и элемент И, выход которого является ьыходом блока, одним из входов которого является один из ffi входов элемента И, а другимвходом Ь блока ЯВЛЯН1ТСЯ объединенныевход дополнительн го элемента НЕ иодин из входов триггера.

Сиетнии Sxod t

ut.t

гИ 2f

Опрос

Риг.З

Вход

BbfxoS

Ост.

25

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровые вычислительные машины | |||

| М., Энергия, 1975, с | |||

| Приспособление для увеличения сцепной силы тяги паровозов и других повозок | 1919 |

|

SU355A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля и коррекции адресных сигналов для памяти последовательного действия | 1980 |

|

SU903989A1 |

Авторы

Даты

1983-06-15—Публикация

1982-02-05—Подача