(5) ЦИФРОВОЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство для контроля @ -кодов Фибоначчи | 1984 |

|

SU1203711A1 |

| Генератор последовательности @ -чисел Фибоначчи | 1983 |

|

SU1112356A2 |

| Генератор последовательности @ -чисел Фибоначчи | 1983 |

|

SU1091146A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Устройство для дешифрации команд | 1980 |

|

SU928338A1 |

| Параллельный сумматор кодов фибоначчи | 1978 |

|

SU840891A1 |

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| Сумматор кодов Фибоначчи | 1981 |

|

SU981993A1 |

| Генератор последовательности @ -чисел Фибоначчи | 1985 |

|

SU1273909A1 |

I

Изобретение относится к вычислительной технике, в частности к гибридным вычислительным машинам, цифровым дифференциальным анализаторам, и может быть применено в системах с числовым программным управлением. Предназначено для преобразования двоичного кода и кода Фибоначчи в частоту следования импульсов.

Известен цифро-частотный интегратор, содержащий регистр управляющего кода, счетчик с импульсными выходами и вентильные схемы 1 .

Недостатками такого устройства являются необходимость использования триггеров с импульсными выходами, а также невозможность работы с числами, представленными в двоичной фибоначчиевой системе счисления.

Наиболее близким к предлагаемому является цифровой интегратор, содер хаи1ий счетчик и вентильные схе.мы 2 .

Недостатком этого устройства является невозможность работы с числами, представленными в двоичной фибоначчиевой системе счисления.

Целью изобретения является расширение функциональных возможностей.

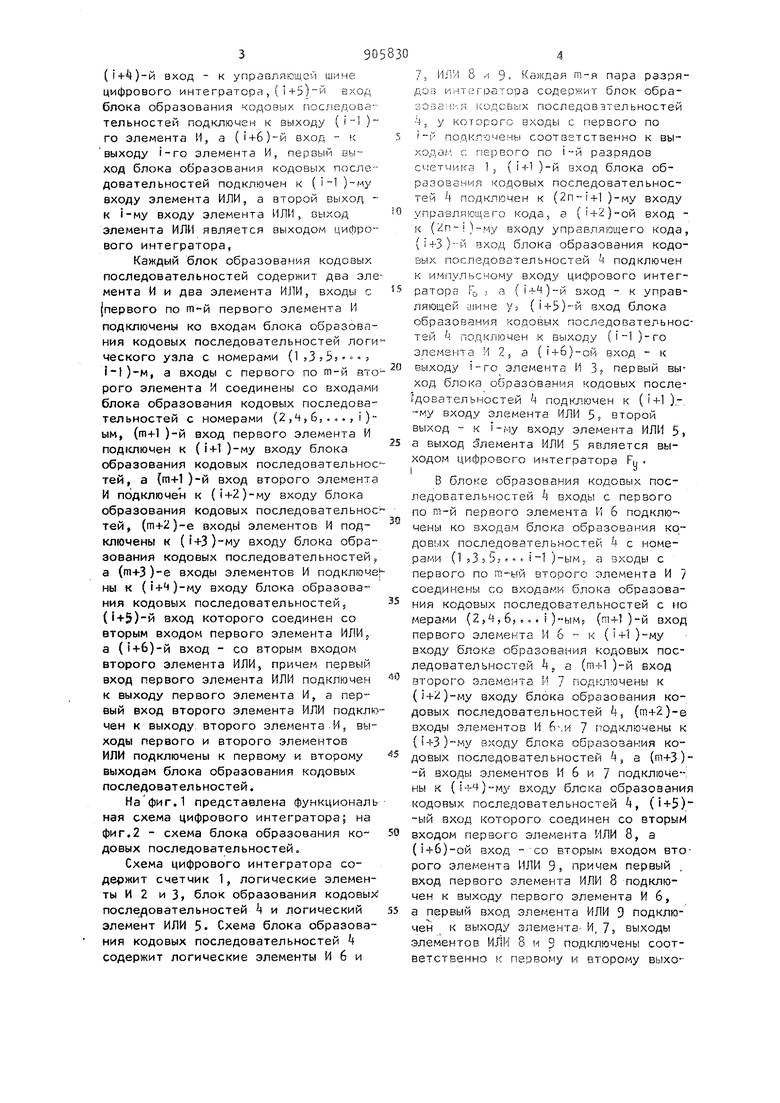

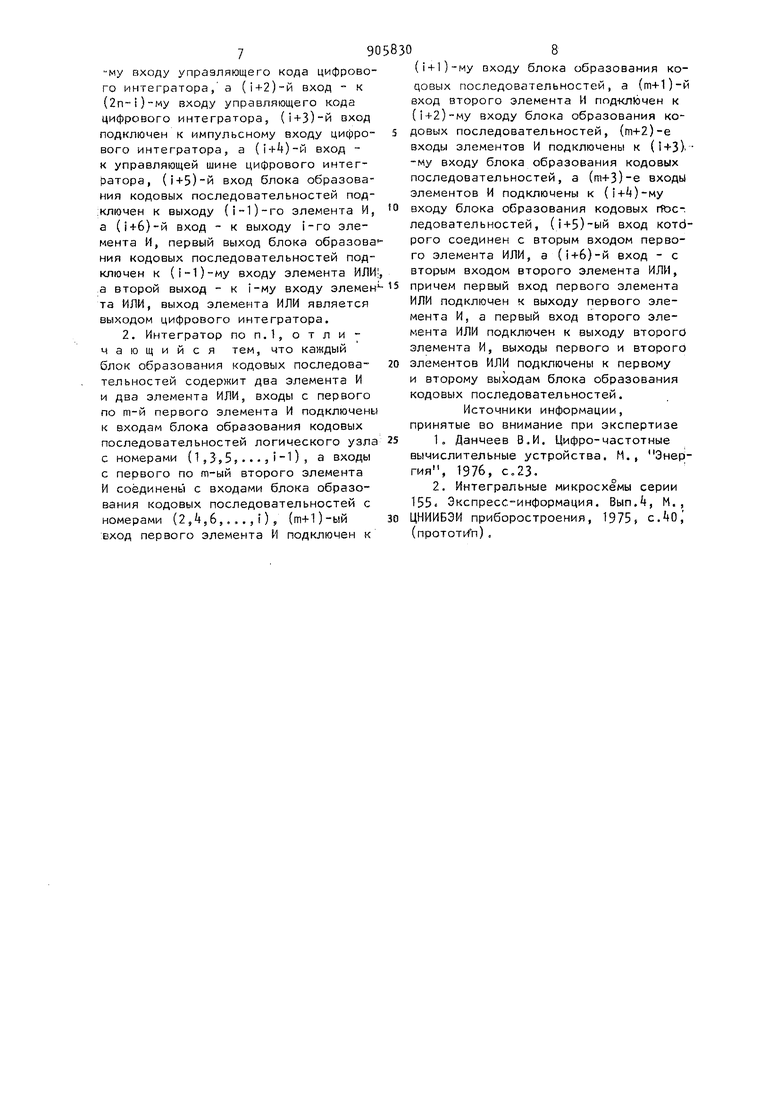

Цель достигается тем, что о цифровом интеграторе, содержащем 1-разрядный счетчик (, ,ii,...,n), а также 2п элементов И и один элемент ИЛИ, каждая т-я пара разрядов интегратора дополнительно содержит блок образования кодовых последс5Ьательностей, входы с первого по i-й которого подключены соответственно к выходам с первого по i-й разрядов счетчика, (1+1)-й вход блока образования кодовых последовательностей подключен к (2n-i+1)-му входу управля.1р1цего кода цифрового интегратора, а (|+2)-й вход -к(2п-|)-му входу управляющего кода цифрового интегратора, (|+3)-й вход подключен к импульсному входу цифрового интегратора, а 390 (1+4)-й вход к управляющей шине цифрового интегратора,(i+5)и вход блока образования кодовых последовательностей подключен к выходу (1) го элемента И, а (|+6)-й вход - к выходу i-ro элемента И, первый выход блока образования кодовых последовательностей подключен к ( )иу входу элемента ИЛИ, а второй выход к i-му входу элемента ИЛИ, оыход элемента ИЛИ является выходом цифрового интегратора, Каждый блок образования кодовых последовательностей содержит два эле мента И и два элемента ИЛИ, входы с (первого по первого элемента И подключены ко входам блока образования кодовых последовательностей логи ческого узла с номерами (1 ,3 ° } 1-|)-м, а входы с первого по пп-й вто рого элемента И соединены со входами блока образования кодовых последовательностей с номерами (2,4,6,.,., i)ым, (т+1 )-й вход первого элемента И подгслючен к (i+1 )-му входу блока образования кодовых последовательнос тей, а (т+1)-й вход второго элемента И подключен к ((+2)-му входу блока образования кодовых последовательное тей, (т+2)-е входУ элементов И подключены к ( входу блока образования кодовых последовательностей, а (т+3)-е входы элементов И подключе ны к (+)-му входу блока образования кодовых последовательностей, (1+5)-й вход которого соединен со вторым входом первого элемента ИЛИ, а (+6)-й вход - со вторым входом второго элемента ИЛИ, причем первый вход первого элемента ИЛИ подключен к выходу первого элемента И, а первый вход второго элемента ИЛИ подкль чен к выходу, второго элемента И, выходы первого и второго элементов ИЛИ подключены к первому и второму выходам блока образования кодовых последовател ьностей. Нафиг,1 представлена функциональ ная схема цифрового интегратора; на фиг.2 - схема блока образования кодовых последовательностей. Схема цифрового интегратора со держит счетчик 1, логические элементы И 2 и 3, блок образования кодовых последовательностей 4 и логический элемент ИЛИ 5. Схема блока образова™ ния кодовых последовательностей содержит логические элементы И 6 и 7- ИЛИ 8 / 9. Каждая т-я пара разрядов интягратора содержит блок образоза: ,я Ko,qoBfcix последовательностей 4. у которого входы с первого по й подкл-эчены соответственно к выходом с; первого по разрядов счетчика 1 , { i+1 )-й вхор. блока образования кодовых последовательностей А подключен к ( )-му входу упразляющаго кода, э ( +0-ой вход к (2п)-.чу входу управляюидего кода, (+3)--й вход блока образования кодовых последовательностей k подключен к импульсному входу цифрового интегратора FO ; гз (i-f)- вход - к управляющей шине УЗ (1+5)й вход блока образования кодовых последовательностей А подключен к выходу (i-1 )-го элемента И 2, а ( i+6)-oi/, вход - к выходу i-ro элемента И 3 первый выход блока образования кодовых после1довател ьностей 4 подкл.ючен к (i+1)-. -му входу элемента ИЛИ 5. второй выход - к 1-му входу элемента ИЛИ 5 а выход Элемента ИЛИ 5 является выходом цифрового интегратора Гц. i В блоке образования кодовых последовательностей k входь с первого по ш-й первого элемента И 6 подклю-цены ко входам блока образования кодовых последовательностей 4 с номерами (1 3 5 Ь i 1 )-ым, а ВХОДЬ с первого по га-ый второго элемента И 7 соединены со входами блока образования кодовых последовательностей с но мерами (, 6, ... i )ымг (m-fl )-й вход первого элемента И 6 - к (5+1)-му входу блока образования кодовых последовательностей k, а (т+1 )й вход второго элемента И 7 подключены к (+2)-ну входу блока образования кодовых последовательностей 4, (т+2)-е входы элементов И 6-.и 7 подключены к )му входу блока образования кодовых последовательностей А, а (т+З) аходы элементов И 6 и 7 подключе-; ны к {1-ьч)--му входу блока образования кодовых, последовательностей k, (i-t-S) ый вход которого соединен со вторым входом первого элемента ИЛИ 8, а (1ч-б)-ой вход - со вторым входом второго элемента ИЛИ 9 причем первый вход первого элемента ИЛИ 8 подключен к выходу первого элемента И 6, а первый вход элемента ИЛИ 9 подключен к выходу элемента- И, 7 выходы элементов ИЛИ 8 м 9 подключены соответственно к первому и второму выходам блока образования кодовых пос/те довательностей k, Устройстоо работает следующим образом. Пусть на управляющей шине у {фиг.1) находится нулевой потенциал такой же потенциал присутствует на ()-M входе блока образования кодовых исследовательностей (фиг.2)« Это приводит к отключению элементов И 6 И 7 блока k. Цифровой интеграто при том работает в чисто двоичном коде при условии, что счетчик 1 (фиг.1) осуществляет пересчет в код с весами (1 ,2,4,8,...,2) Допусти что на входах параллельного управляюще го кода с первого по 2п-ый,присутствуе код 2п-разрядного числа N« Вентильные схемы 5 состоящие из элементов И 2 и 3 и элемента ИЛИ 5, объединяют cиJ;(aлы вь1хода счетчика 1 и шин параллельного управляющего кода ТФИГ.1). Если на импульсный вход F цифрового интегратора поступают импульсы с частотой ffl 5 то на выходе устройства f будут импульсы со средней ча тотой следованиями а Для преобразования в частоту сле дования импульсов чисел, представле ных в двоичной фибоначчиевой системе омисления, на входе управляюще иины У (фиг.1) должен присутствоват единичный потенциал. Такой же потенциал присутствует на (i+4)-M входе блока образования кодовых последовательностей т (фиг.2), на первом выходе которого следуют импульсы в соответствии с функцией, реализуемой элементом И 6 .(фиг.2), независимо от функции, реа лизуемой элементом И 2 (фиг.1), а на втором выходе блока образования кодовых последовательностей следу ют импульсы в соответствии с .функц ей, реализуемой элементом И 7 (фиг, независимо от функции, реализуемой элементом ИЗ (фиг.1). Цифровой интегратор при этом работает в двоимной фибоначчиевой системе очислечия при условии, что счетчик 1 (фиг.1) осуществляет пересчет в коце Фибоначчи с весами (1,1,2 3j ), где )J. О при , Р 11 ПРИ , рГ.-р-О Р ,3,,.,,,2п, + -Fp. р- характеристический параметр Фибоаччиевых систем счисления (,2, ,..0. Допустим, что на входах параллелы-ого управляющего кода с первого по 2п-й (фиг.1) присутствует код 2п-раз ядного числа N. Вентильные схемы, состоящие из элементов И 2 и 3 эле-, мента ИЛИ 5 и блоков образования коовых последовательностей , объединяют сигналы счетчика 1 и шин параллельного управляющего кода (фиг.1). Если на вход цифрового интегратора поступают импульсы с частотой fj, , то на выходе устройства Fy следуют импульсы со средней частотой f,, . N D fp T4Предложенное устройство позволяет преобразовывать в частоту как двоичный, таки двоично- фибоначчиевый код, что является значительным расширением функциональных возможностей двоичного цифрового интегратора с последовательным переносом Известно, что устройства, работающие в Ркодах Фибоначчи, обладают ошибкообнаруживающими свойствами.Потенци-, альный коэффициент обнаружения ошибок определяется по формуле JH 2 где п разрядность устройства. Так для 16-разрядного цифрового интегратора, работающего в р -кодах Фибоначчи, 0,97. Формула изобретения . 1. Цифровой интегратор, содержащий i-разрядный счетчик (, ,2,... п) 5 а также 2п элементов И и один элемент ИЛИ,отличающийся тем, что, с целью расширения функциональных возможностей за счет возмокености преобразования в частоту следования импульсов как двоичного, так и двоично-фибоначчиевого кода, кажда т-ая пара разрядов интегратора дополнительно содержит блок образования кодовых последовательностей, входы с первого по i-и которого подключены :соответственно к выходам с первого по i-й разрядов счетчика, (+1)-й вход блока образования кодовых после довательностей подключен к (2п-1+1)-му входу упразляющего кода цифрового интегратора, а (1+2)-й вход - к ()му входу управляющего кода цифрового интегратора, (|+3)й вход подключен к импульсному входу цифрового интегратора, а )-й вход к управляющей шине цифрового интегратора, (+5)-й вход блока образования кодовых последовательностей под:ключен к выходу {i-1)-ro элемента И, а (+6)й вход к выходу i-ro элемента И, первый выход блока образова ния кодовых последовательностей подключен к (i-l)-My входу элемента ИЛИ|, а второй выход - к i-му входу элемен та ИЛИ, выход элемента ИЛИ является выходом цифрового интегратора.

905830

(i+l)-My входу блока образования коцовых последовательностей, а (т+1)-й вход второго элемента И под-кл1бчен к (1+2)-му входу блока образования кодовых последовательностей, {in+2)-e входы элементов И подключены к (1+3). -му входу блока образования кодовых последовательностей, а (т+3)-е входы элементов И подключены к (1+4)-му входу блока образования кодовых гРэс-: ледовательностей, (|+5)-ый вход котёрого соединен с вторым входом первого элемента ИЛИ, а (1+6)-й вход - с вторым входом второго элемента ИЛИ, причем первый вход первого элемента ИЛИ подключен к выходу первого элемента И, а первый вход второго элемента ИЛИ подключен к выходу второго элемента И, выходы первого и второго элементов ИЛИ подключены к первому и второму выходам блока образования кодовых последовательностей. Источники информации, принятые во внимание при экспертизе

гия.

Авторы

Даты

1982-02-15—Публикация

1979-07-04—Подача