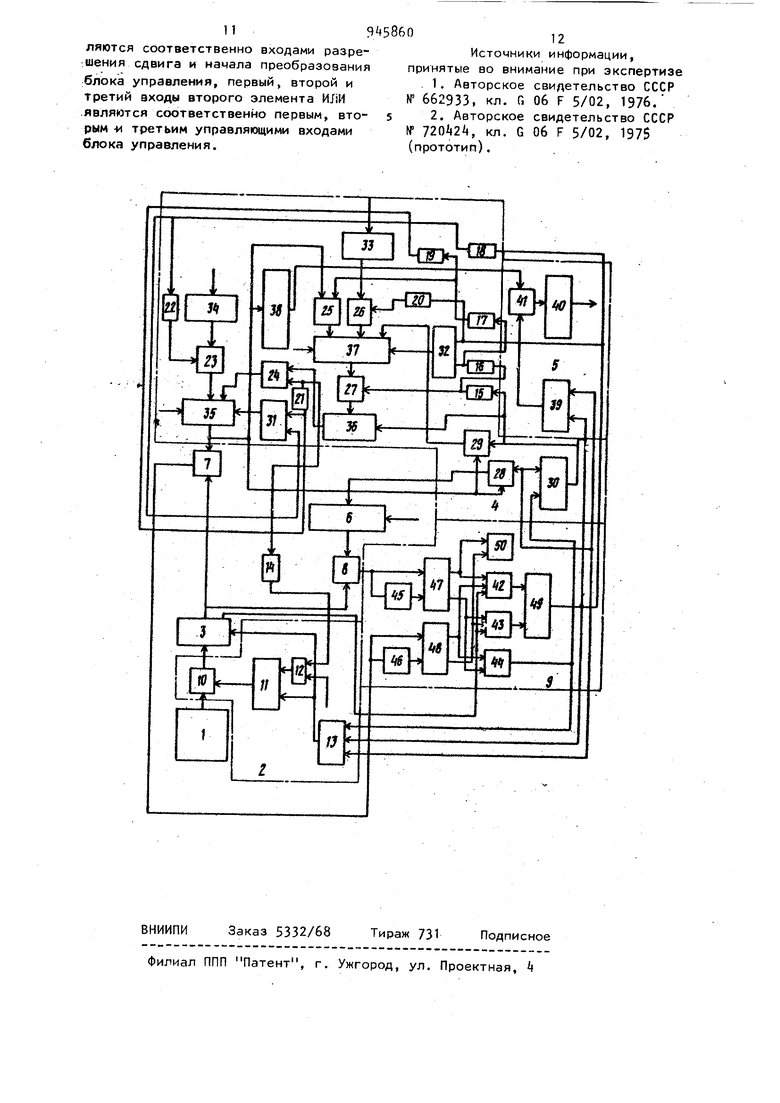

(5) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ПОЗИЦИОННЫЙ КОД СО СМЕШАННЫМ 1 Изобретение относится к автоматике и вычислительной технике и мотет быть использовано при построении преобразователей в специализированных вычислительных машинах. Известен преобразователь двоичного кода в код с основаниями, равными числам Фибоначчи, содержащий сдвиговый регистр, два сумматора, два регистра, блок управления и элемент И Недостаток известного преобразова теля состоит в низком быстродействии Наиболее близким к предлагаемому по технической сущности и схемному построению является преобразователь двоичного кода в позиционный код со смешанным основанием, содержащий сдв говый регистр, блок управления, гене ратор импульсов, формирователь эквивалентов и вычитатель С2. Недостаток известного преобразова теля, состоит в относительно низком быстродействии и невозможности преоб ОСНОВАНИЕМ разооания двоичного кода в позиционный код с весами, равными числам Фибоначчи. Целью изобретения является повышение бь1стродействия и расширения функциональных возможностей, заключакхцееся в «преобразовании двоичного кода в позиционный код с основаниями, равными числам Фибоначчи. Поставленная цель достигается тем, что в преобразователь двоичного кода в позиционный код со смешанным основанием, содержащий сдвиговый регистр, блок управления, генератор импульсов, формирователь эквивалентов и вычитатель, первый информационный вход которого соединен с первым информационным выходом формирователя эквивален- тов, второй информационный вход вычитателя является ин(юрмационным входом преобразователя, синхровход сдвигового регистра соединен с тактовым выходом блокауправления,, тактовый вход которого соединен с выходом генерато3gpa импульсов, введены шифратор выходного кода, первая и вторая группы эле ментов И и схема сравнения, первая и вторая группы информационных входов которой соединены с выходами элемеитов И первой и второй групп соответст венно, первые входы которых соединены с разрядными выходами сдвигового регистра, а вторые входы элементов И первой и второй групп соединены соответственно с разрядными выходами вычитателя и вторым информационным выхо дом сУэрмирователя эквивалентов, выход позиционного кода которого соединен с информационным входом шифратора выход ого кода, первый и второй управляющИ входыкоторого соединены соответствен но с выходами БОЛЬШЕ и РАВНО схемы сравнения, управляющий вход которой соединен с выходом старшего разряда сдвигового регистра, вход сброса которого соединен с выходом сброса блока управления, первый, второй и третий управляющие входы которого соединены соответственно с выходами БОЛЬШЕ РАВНО, МЕНЬШЕ схемы сравнения и с пер вым, вторым и третьим управляющими входами формирователя эквивалентов, выход разрешения сдвига которого соединен с входом разрешения сдвига блока управления, вход пуска которого является входом пуска преобразователя, информационный выход которого соединен с выходом шифратора выходного кода, первый и второй входы эквивален тов преобразователя соединены соответ ственно с первым и вторым входами эквивалентов формирователя эквивалентов, и тем, что в нем формирователь эквивалентов содержит четыре регистра вычитатель, семь групп элементов И, три элемента ИЛИ, элемент задержки, две группы последовательно соединенных элементов задержки из шести и дву элементов задержки соответственно и дешифратор, входы которого соединены с выхода «1 первого регистра, являющимися информационным выходом формирователя эквивалентов, и первыми входами элементов И первой, второй и третьей групп, выходы с первого по пятый элементов задержки первой группы соединены соответственно с первыми входами элементов И четвертой группы, nepiBMM входом первого элемента ИЛИ, вторыми входами элементов И первой группы, первым входом второго элемента ИЛИ, первыми входами элементов И пятой группы, выход шестого элемента 0 задержки первой группы является выходом разрешения сдвига формирователя эквивалентов, выходы первого и второго элементов задержки второй группы соединены соответственно с вторым входом второго элемента ИЛИ и первыми входами элементов И шестой группы, первый вход третьего элемента ИЛИ является первым управляющим входом форэквивалентов и соединен мирователя с вторыми входами элементов И третьей группы, выходы которых являются информационными выходами формирователя эквивалентов, второй вход первого элемента ИЛИ является вторым управляющим входом формирователя эквивалентов и соединен с входом первого элемента задержки второй группы, и через элемент задержки соединен с первыми входами элементов И седьмой группы, тре|гий управляющий вход формирователя , Эквивалентов соединен с вторым входов третьего элемента ИЛИ, выход которого соединен с входом первого элемента задержки первой группы, входом обнуления второго регистра и вторыми входами элементов И второй группы, выходы элементов И первой, второй и седьмой групп соединены соответственно с первым, вторым и третьим информационны 1и входами вычитателя,выходы которого соединены с вторыми входами элементов И четвертой группы, выходы которых соединены с.входами второго регистра, выходы второго, третьего и четвертого регистров соединены соответственно с вторыми входами элементов И пятой, шестой и седьмой групп, выходы второго и первого элементов ИЛИ соединены соответственно с входами обнуления вычитателя и первого регистра, первый и второй информационные входы которого соединены соответственно с выходами элементов И пятой и шестой групп, входы третьего И, четвертого регистров являются информационным входом формирователя эквивалентов, третий информационный вход первого регистра и информа14ионный вход третьего регистра являются первым входом эквивалента формирователя эквивалентов, четвертый информационный вход вычитателя является вторым входом эквивалента формирователя эквивалентов, а также тем, что в нем блок управления содержит два элемента ИЛИ, триггер и элемент И, первый вход которого является тактовым входом блока управления, выходом которого является выход элемента И, второй вход которого соединен с единичным выходом триггера, единичный и нулевой входы которого соединены соответственно с выходами первого и второго элементов ИЛИ, первый и второй входы перво .го элемента ИЛИ являются соответственно входами разрешения сдвига к на чала преобразования блока управления первый, второй и третий входы второго элемента ИЛИ являются соответстве но первым, вторым и третьим управляющими входами блока управления. На чертеже представлена структурная схема предлагаемого преобразователя. Она содержит генератор 1 импульсов, блок 2 управления, сдвиговый ре гистр 3, формирователь А эквиваленто шифратор 5 выходного кода, вычитатель 6, группы элементов И 7 и 8, сх му 9 сравнения. Блок 2 управления, предназначенны для управления работой регистра 3 состоит из элемента И 10, триггера 1 двух элементов ИЛИ 12 и 13. Формирователь эквивалентов k, предназначенны для формирования весов разрядов фибог наччиевой системы счисления, содержи элементы задержки Й-22, группы элементов И 23-29, три элемента ИЛИ 3032, четыре регистра 33-36, вычитатель 37, дешифратор 38. Элементы задержки сгруппированы в первую группу из шести последовательно соединенных элементов Й-17, 19 и 21 задержки, вторую группу последовательно, соединенных элементов 18 и 22 задержки и элемент 20 задержки, шифратор 5 выходного кода состоит из элемента ИЛИ 39 регистра йО и группы элементов И . Схема 9 сравнения, предназначенная для сравнения фибоначчиевого эквивалента и остатка, состоит из элементов И 42-44, двух элементов НЕ 45 .и 46, двух триггеров 47 и 48, элемен та ИЛИ 49 и элемента И 50. Преобразователь работает следующим образом. Предварительно на вычитатель 6 на капливающего типа заносится преобразуемое число, на регистры 34 и 35 за носится вес старшего фибоначчиевсГго разряда q. и на вычитатель 37 и регистр 33 вес q. фибоначчиевого разряда. Остальные регистры находятся в нулевом состоянии. При поступлении сигнала начала преобразования на элемент ИЛИ 12 триггер 11 устанав 606 ливается в единичное состояние, сигнал с генератора 1 импульсов через элемент И 10 проходит на сдвиговый регистр 3 и устанавливает старший разряд регистра в 1.. В результате этого старшие разряды преобразуемого числа и фибоначчиевого эквивалента через группы элементы И 7 и 8 поступают в схему 9 сравнения на парафазные входы триггеров 47 и 8 и устанавливают их в 1 или О. В качестве триггеров kj и 48 могут быть использованы триггеры RS-типа. Если триггер 47 в единичном состоянии, а триггер 48 в нулевом состоянии, т.е. преобразуемое число больше фибоначчиевого веса старшего разряда, то сигнал с выхода элемента И 50 через элементы ИЛИ 30 и 39 поступает в фор-, мирователь 4 эквивалентов и на шифратор 5, а также в блок управления 2. В результате триггер 11 через элемент ИЛИ 13 устанавливается в О и тем самым препятствует поступлению импульсов с генератора на сдвиговый регистр 3, а сам сдвиговый регистр обнуляется в старший разряд регистра 4 О через группу элементов И 41 с выхода дешифратора 38, на вход которого с регистра 35 поступает код фибоначчиевого веса старшего разряда, заносится 1. Одновременно с этим фибоначчиевый вес t-ro разряда г (старшего через группу элементов И 28 поступает с выхода регистра 35 в вычит.атель 6, где происходит образование остатка, а через группу элементов И 29 в вычитатель 37 для образования фибонамчиевого веса следующего (I 1) разряда. Согласно алгоритму образования весов в фибонамчиевой системе счисЛения, вес ) разряда q; q.- q. . Этим же сигналом производится обнуление регистра 36, который через группу элементов И 27 заносится код фибоначчиевого веса q. После этого через элемент ИЛИ 32 П{ Ьисходит обнуление вычитателя 37 и на него через группу элементов И 25 заносится (; ибоначчиевый вес q. , после чего через элемент ИЛИ 31 происходит обнуление регистра 35 и запись в него через группу элементов И 24 фибоначчиевого веса q,, затем через элемент ИЛИ 12 происходит установка i триггера 11 в 1 и очередной импульс с генератора проходит на регистр.3 и устанавливает в 1 старший разряд, после чего вге повторяется. Если триг79гер 7 находится в нулевом состоянии а триггер в единичном состоянии, т.е. преобразуемое число ( или остаток) меньше фибоначчиевого эквивален та, то сигнал через элемент И k поступает в формирователь эквивалентов 4 для образования следующего мла шего фибоначчиевого веса. Одновремен но сигнал поступает в блок управления, где устанавливает в О регистр и блокирует прохождение импульсов ге нератора 1. Если при сравнении одноименных разрядов остатка и Фибоначчи евого эквивалента триггеры kj и 8 находятся в одинаковом состоянии, т.е. оба или в О или в 1, то чер время, необходимое для установки в О триггера, очередной импульс с ге нератора производит сдвиг единицы в регистре 3 и таким образом происходит сравнение следующих младших разрядов. При сравнении последних младших разрядов сигнал с выхода сдвигового регистра через элементы И 2 или 3, в Зависимости от toro, в каком состоянии находятся триггеры 47 и 8 и элемент ИЛИ 49, поступает одновременно в шифратор 5 выходного кода для записи 1 в соответствующий разряд регистра kO, в результате чего на выходе регистра получаем фибоначчиевый код, в формирователь эквивалентов - для сброса в О регист ра 35 и вычитателя 37 и установки в них через группы элементов И 23 и 26 начальных значений фибоначчиевых весов q, и q. и в блок управления для обнуления сдвигового регистра и установки в О триггера 11. В результате этого преобразователь приведем в исходное состояние и готов к преобразованию нового двоичного ко да. Элементы задержки необходимы для синхронизации работы преобразователя. Таким образом, предлагаемый преоб разователь позволяет повысить скорос Преобразования кодов из двоичной сис темы счисления в фибоначчиевую систему счисления,по сравнению с известным за счет совмещения во времени процесса формирования фибоначчиевого веса q. и значения 1-го разряда фибоначчиевого кода, а также за счет использования классических двоичных вычитателей вместо фибоначчиевых сумматоров, быстродействие которых значительно ниже. 0 Так, максимальное время сложения двух кодов в двоичной системе счисления1Г ч (i + 1)i, это же время в фибоначчиевой системе счисленияи длр (i-( . -Ь , где с время сложения , Гсл.ф (1)Ч нормальных кодов, Тел 4( Отсюда для сорокаразрядных коДЬв максимальное рремя сложения в двоичной системе счисления приблизительно в 10 раз меньше, чем в фибоначчиевой системе счисления. Преимуществом предлагаемого преобразователя является также возможность совмещения во времени процессов формирования веса q|.и сравнения веса q. с преобразуемым числом, причем сравнение происходит без восстановления остатка, что также повышает .скорость преобразования по сравнению с известным устройством. Формула изобретения 1. Преобразователь двоичного кода в позиционный код со смешанным основанием, содержащий сдвиговый регистр, блок управления, генератор импульсов, формирователь эквивалентов и вычитатель, первый .информационный вход которого соединен с первым информационным выходом формирователя эквивалентов, второй информационный вход вЫчитателя является информационным входом преобразователя, синхровход сдвигового регистра соединен с тактовым выходом блока управления, тактовый вход которого соединен с выходом генератора импульсов, отличаюю щ и и с я тем, что, с целью повышения быстродействия и расширения функциональных возможностей, заключающегося в преобразовании двоичного кода в позиционный код с основаниями/, равными числам Фибоначчи, в него введены шифратор выходного кода, первая и вторая группы элементов И и схема сравнения, первая и вторая груп информационных входов которой соединены с выходами элементов И первой и второй групп соответственно, первые входы которых соединены с разрядными выходами сдвигового регистра, а вторые входы элементов И первой и второй групп соединены cooTBetcTseHно с разрядными выходами вычитателя и вторым информационным выходом формирователя эквивалентов, выход пози9ционного кода которого соединен с йьгформационным входом шифратора выходжэго кода, первый и второй управляющие входы которого соединены соответственно с выходами БОЛЬШЕ и РАВНО схемы сравнения, управляющий вход которой соединен с выходом старшего разряда сдвигового регистра, вход сброса которого соединен с выходом сброса блока управления, первый, вто- Ю рой и третий управляющие входы которого соединены соответственнос выхо дами БОЛЬШЕ, РАВНО, МЕНЬШЕ схемы дсра нения и с первым, вторым и третьим ,управляю{Цими входами формирователя Ьквивалентов, выход разрешения сдвига которого соединен с входом разрешения сдвига блока управления, вход Пуска которого является входом пуска лреобразователя, информационный зыход которого соединен с выходом ши ратора выходного кода, первый и йторой г)ходы эквивалентов преобразовате ля соединены соответственно с первым и вторым входами эквивалентов формирователя эквивалентов. 2/ Преобразователь по п. 1, от л и ч а ю щ и и с я тем, что в нем формирователь эквивалентов содержит четыре регистра, вычитатель, семь групп элементов И, три эд мента ИЛИ, .элемент задержки, две группы последовательно соединенных элементов задержки из шести jR двух элементов задержки соответственно и дешифратор, входы которого соединены с выходами первого регистра,являющимися информа ционным выходом формирователя эквива лентов и первыми входами элементов И.4о первой, второй и третьей групп, выхо ды с первого по пятый элементов задержки первой группы соединены соответственно с первыми входами элементов И четвертой группы, первым BX дом первого элемента ИЛИ, вторыми входами элементов И первой группы, первым входом второго элемента ИЛИ, первыми входами элементов И пятой группы, выход шестого элемента задержки первой группы является выходом разрешения сдвига формирователя эквивалентов, выходы первого и второ го элементов задеожки второй ГРУППЫ соединены соответственно с вторым входом второго элемента ИЛИ и первыми входами элементов И шестой груп пы, первый вход третьего элемента ИЛ является первым управляющим входом o 10 формирователя эквивалентов и соединен с вторыми входами элементов И третьей группы, выходы которых являются информационными выходами формирователя эквивалентов, второй вход первого элемента ИЛИ является вторым управляющим входом формирователя эквивалентов и соединен с входом первого элемента задержки второй группы и через элемент задержки соединен с первыми входакм элементов И седьмой группы, третий управляющий вход формирователя эквивалентов соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с входом первого элемента задержки первой группы, входом обнуления второ-. го регистра и вторыми входами элементов И второй группы, вы}соды элементов И первой, второй и седьмой групп соединены соответственно с первым, вторым и третьим информационными входами вычитателя, выходы которого соединены с вторыми входами, элементов И четвертой группы, выходы которых соединены с входами второго регистра, вьгходы второго, третьего и четвертого регистров соеда4нены соответственно с вторыми входами элементов И пятой, шестой и седьмой групп, выходы второго и первого элементов ИЛИ соединены соответственно с входами обнуления вычитателя и первого регистра, первый и второй информационные входы которого соединены соответственно с выходами элементов И пятой и шестой групп,входы претьего и четвертого регистров являются информационным входом формирователя эквивалентов, третий информационный вход первого регистра и инФормационный вход третьего регистра вляются первым входом эквивалента ормирователя эквивалентов, четвертый нформационный вход вычитателя являтся вторым входом эквивалента формиователя эквивалентов, 3. Преобразователь по пп. 1 и 2, отличающийся -тем, что, в нем блок управления содержит дв.а элемента ИЛИ, триггер и элемент К, первый вход которого является тактовым входом блока управления, выходом которого является выход элемента И, второй вход которого соединен с единичным выходом триггера, единичный и нулевой входы которого соединены соответственно с выходами первого И второго элементов ИЛИ, первый и второй входы первого элемента ИЛИ являются соответственно входами разрешения сдвига и начала преобразования блока управления, первый, второй и третий входы второго элемента ИЛИ .являются соответственно первым, вторым -и третьим управляющими входами блока управления. 9/45 012 Источники информации, принятые во внимание при экспертизе . 1. Авторское свидетельство СССР W 662933, кл. Г, Об F 5/02, 1976. 2. Авторское свидетельство СССР № 720), кл. G Об F 5/02, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1973 |

|

SU523406A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

Авторы

Даты

1982-07-23—Публикация

1980-12-02—Подача