(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

I

Изобретение относится к вычислительной технике и может быть использовано в качестве запоминающего устройства в вычислительных машинах.

Известно устройство для выборки адреса в постоянном запоминающем устройстве, содержащее дешифратор адреса, запоминающие элементы, кольцевую пересчетную схему, генератор кодов н выходные вентили. Код адреса числа, пришедший на дешифратор адреса, возбуждает одну из адресных шин, с которой сигнал поступает на соответствующий запоминающий элемент Cl .

Известны постоянные запоминающие устройства, содержащие ячейки запоминающих элементов и устройство управления, обеспечивающее поиск и считывание информации. Устройство управления состоит из регистра адреса, дешифратора и усилителей считывания. Дещифратс в соответствии с кодом адреса выбирает одну..ячейку, а усилители считывания усиливают сигнал с этой ячейки до необходимого уровня 2.

Недостаток указанных устройств заключается в том, что обращение к ячейке запоминающих элементов и считывание инфс мации одновременно может происходить только по одному адресу. При обращении по разным адресам считывание информации происходит последовательно, при этом суммарное время выбхзрки имеет

10 большое значение.

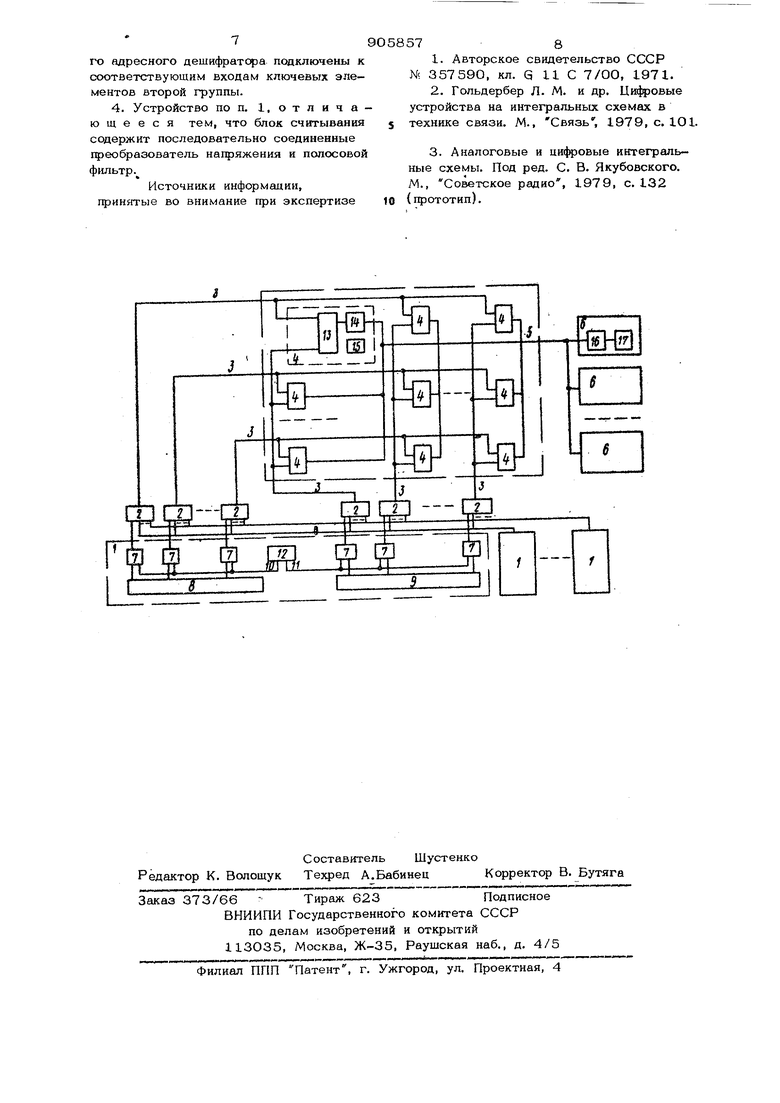

Наиболее близкой к изобретению по технической сущности является двухкоординатная матрица с двумя ступенями дешифрации, содержащая матрицу запоми15нающих элементов, блок адреса с дешифраторами адресов и адресными формирователями и блок считывания с усилителями считывания. При поступлении на дешифраторы адресов кода адресу опреде30ленного запоминающего элемента возбуждаются определенные шины дешифраторов и с помощью адресных шин по двум координатам выбирается запоминающий элемент, с которого по обшей для всех эле ментов разрядной шнне считывается его состояние з1. Однако указанное устройство обеспечивает обращеине к запоминающим элементам и считывание информации только по одному адресу. Обращаться и считывать информацию независимо и сановре- менно ло разным адресам невозможно. Таким образом, общее время выборки по разным адресам имеет большое зна чение и определяется суммой времен вы борки по каждому адресу отдельно. Цель изобретения - повышение быстродействия устройства. Указанная цель достигается тем, что в запоминающее устройство, содержащее элементы памяти, выходы которых подкл „-„. „ „„ -. чены ко входу блока считывания, и адрес „. . «„„„ „„ „ . ный сшок, введены дополингтельные адрес ные блоки, аналоговые сумматоры и допол иительные блоки счсггыванвя, входы которых подключены ко входу блока считывания, выходы аналоговых сумматоров подключены к схютветствующнм входам элементов памяти, а входы аналоговых cyMMaTqpoB подключены к соответствующим выходам а/фесных блоков. Кроме того, элемент памяти содержит триггер, ключ, согласующий элемент, выход которого подключен ко входу ключа, а управляющий вход ключа подключен к выходу триггера. Адресный блок содержит и вто рой деши4 атс ы, первую и вторую группы ключевых элементов н генератор, п вый выход которого подключен к первым входам первой группы ключевых элементов, а второй выход - к входам второй группы ключевых элементов, выходыпервого адресного дешифратора подключены к соответствующим входам ключевых элементов первой группы, а выходь второго адресного дешифратора подключены к соответствующим входам ключевых элементов второй группы. Блок считывания содержит Щ)еобразователь и полосовой фияыр, выход которо го подключен ко входу 1фео взователя. На чертеже 1федставлена схема щ)едлагаемого запоминающего устройства. Запоминающее устройство содержит адресные блоки 1, аналог&вые сумматоры 2, адресные шины 3, элементы памяти 4, общую разрядную шину 5, блоки считывания 6, включевые элементы 7, первый 8 и второй 9 адресные дешифраторы, первый 10 и второй 11 выходы генератора, генератор 12, согласующий элемент 13, ключ 14, триггер 15, полосовой фильтр 16 и преобразователь напряжения 17. Устройство работает следующим образом. Количество адресных блоков 1 равно количеству блоков считывания 6. В состав а/фесного блока 1 входит генера.- тар 12, а в состав каждого блока считывания 8 входит полосовой фильтр 18, причем в полосе щзопускания фильтров 18 находятся соответственно несущие частоты задающих генераторов 12, а значения несущих частот задающих гев аторов 12 не равны между собой. Обращение к матрице элементов памя шоисходит при подаче кодов адреса на входы адресных блоков 1, причем каждый из них обеспечивает обращение в каждый момент времени только к одному элементу памяти 4, т.е. только по одному адресу. Одновременное и независимое обращение по одному или разным адресам обеспечивается одновременным о ащением нескольких адресных блоков 1 к общей матрице элементов памяти 4, прк этом адресные блоки 1 вырабатывают сигналы oiq:oca в виде колебаний с разными несущими частотами, имеющими различный спектр, а выделение сигналов считывания из общего происходит за счет частотного разделения системой полосовых фильтров 18 в блоках считывания 6 Каждому адресному блоку 1 соответствует определенный блок считывания 6, полосовой фильтр 18 которого пропускает сигналы с частотой генератора 12 данного адресного блока 1. Рассмотрим работу устройства в режиме считывания информации более подробно. Код адреса ог ашиваемого элемента памяти 4 поступает на вход блока адреса 1, а точнее код адреса одной координаты поступает на вход первого дешифратора адреса S этой координаты, а код адреса другой координаты, поступает на вход второго дешифратора 9 другой координаты, прк этом на одном выходе дешифратора 8 и одном выходе дешифратора 9 появляются логические сигналы, которые поступают на первые входы соответствующих ключевых элементов 7. Выходной сигнал генерат чэа 12 в виде одно полярных импульсов с определенной несущей частотой действует между выходами 10 и 11, причем положительный потенциап приложен к выходу 10. Так как выход Ю присоединен ко вторым входам ключевых элементов 7 первой группы, а выход 11 гфисоединен ко вторым входам ключевых элементов 7 второй группы, то сигнал генератора 12 оказывается приложен между вторыми входами ключевых элементов 7 перчой и второй групп. Логические сигналы с дешифраторов 8 и 9 являются разрешающими для ключевых элементов 7, на которые они поступают, и сигнал генератора 12 оказывается приложенным между входами аналоговых сумматоров 2 разных координат, подключенных к выходам открытых ключевых элементов 7. Каждый аналоговый суммат э 2 обеспечивает передачу сигналов с любого входа на общий выход, 1ФИ этом обеспечивается и развяэка входных сигналов. Практически, аналоговый сумматор 2 может быть реалиаован в виде диодной c6q3KH, одинаковые электроды которой присоединены к общему выходу. Таким образом, сигнал генератора 12 оказывается приложенным между асфесвыми шинами 3, соединенными с выходами соответствующих аналого вых сумматоров 2, и поступает на входы огфашиваемого элемента памяти 4. Этот сигнал через согласующий элемент 13 поступает на вход ключа 14. В триггере 15 элемента памяти 4 хранится один бит информации. Если триггер 15 находится в нулевом состоянии, то ключ 14 закрыт и на его выход никакие сигналы не П|)оходят, а если в триггере 15 хранится логическая I, то сигнал с тригг а 15 поступает на ключ 14 и держит его в открытом состоянии. В этом случа согласующий элемент 13 обеспечивает согласование и передачу сигнала со входа через открытый ключ 14 на общую разрядную шину 5. С выхода общей разрядной шины 5 сигнал поступает на входы блоков считывания 6, гфичем входом каждого блока считывания 6 является полосовой фильтр 16. Колебание появляется на выходе только того полосового фцльтра 16, в полосе пропускания которого находится несущая частота дан кого колебания. Далее этот сигнал с выхода фильтра 16 поступает на вход преофазователя 17, на выходе которого он 1феофазуется в логический сигнал. Аналогично «фоисходит опрос и счетыван инфсфмаиин с элементов памяти 4 други ми адресными блоками 1. Использование в устройстве в качест ве сигналов огфоса переменных колебгний разных частот и их частотное разеление в блоках считывания 6 позволят одновременно обращаться к многим дресным блокам 1 и считывать информаию со многих элементов памяти 4. При том поле памяти, образованное матрией элементов 4 памяти, остается общим. меньшение общего времени выбелки стаовится значительным большом колиестве одновременно опрашиваемых адресых блоков. Пригменение предлагаемого запомннатощего устройства по сравнению с известными позволяет существенно уменьшить время выборкк, этом отпадает необходимость поочередного о ашения к общему полю памяти и установлению приоритета 1ФЯ о ашенки. Независимость Обращения в грвдлагавмом устройстве позволяет использовать его в качестве запоминающего устройства в вычвсяктельных системах с большим количеством конфликтных снтушхий 1ФИ обрашенвн в память. Формула изобретения 1.Запоминающее устройство, содержащее элементы памяти, выходы которых подключены ко входу блока считывания,, и адресный блок, отличающевс я тем, что, с целью повышения быст родействия устройства, оно содержит до полнительные адресные блоки, аналоговые сумматоры и дополнительные блоке считывания, входы подключены ко входу блока считывания, выходы аналоговых сумматоров подключены к соответствующим входам элементов памяти, а входы - к соответствующим выходам адресных блоков. 2.Устройство по П.1, отличающее с я тем, что элемент памяти содержит последовательно соединенные тригг, ключ и согласующий элемент. 3.Устройство по п. 1, отличающее с я тем, что адресный блок содержит первый и дeшифpaтqpы, первую и вторую группу ключевых элементов и генератор, первый выход которого подключен к первым входам ключевых элементов группы, а второй выход - к первым вход1М ключевых элементов втсрой группы, выходы перво-i го адресного дещк4чратора подключены к соответствующим входам ключев,тх элементов первой группы, а выходы второго адресного дешифратсзра подключены к соответствующим входам ключевых элементов второй группы.

4. Устройство поп, 1, отличающее с я тем, что блок считывания содержит последовательно соединенные греобрааователь на1фяж.ения н полосовой фильтр.

Источники информадин, гфинятые во внимание при экспертизе

О58578

1.Авторское свидетельство СССР № 357590, кл. G II С 7/00, 1971.

2.Гольдербер Л. М. и др. Цифровые устройства на интегральных схемах в

5 технике связи. М., Связь, 1979, с. 101.

3.Аналоговые и интегральные схемы. Под ред. С. В. Якубовского. М., Советское радио, 1979, с. 132

10 (гфототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU894789A1 |

| Программируемый генератор импульсов | 1984 |

|

SU1248029A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для отображения информации | 1985 |

|

SU1328840A2 |

| Программируемый генератор импульсов | 1985 |

|

SU1298869A2 |

| Устройство для распознавания образов | 1986 |

|

SU1361589A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Адаптивное телеметрическое устройство | 1979 |

|

SU858060A1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

Авторы

Даты

1982-02-15—Публикация

1980-05-08—Подача