(5) УСТРОЙСТВО для КЛАССИФИКАЦИИ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Оперативное запоминающее устройство | 1976 |

|

SU733019A1 |

| "Устройство для морфологического анализа слов естественных языков и языков "деловой прозы" | 1989 |

|

SU1837327A1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2021 |

|

RU2768543C1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1988 |

|

SU1575231A1 |

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для классификации двоичныхчиСЕл | 1979 |

|

SU802958A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

I

Изобретение относится к автоматике и вычислительной технике и может быть использовано при технической реализации специализированных устройств обработки данных.

Известно устройство для классификации двоичных чисел, содержащее сдвиговый регистр, буферные запоминающие блоки, управляемый элемент задержки, двоичный счетчик, элементы И, триггеры, элемент задер хки и формирователь импульсов t

К недостаткам этого устройства следует отнести малое быстродействие, которое связано с тем, что при классификации каждое п-разрядное двоичное числЬ анализируется за п тактов.

Наиболее близкое к предлагаемому устройство, содержащее регистр текущего значения, буферные запоминающие блоки, коммутатор, элементы И, регистр адреса и элемент HEtzJ.

Недостатком известного устройства является то, что его нельзя использовать там, где требуется классификация двоичных слов по значению кода признака, содержащегося в двух или более разрядах, т.е. по совокупному признаку.

Цель изобретения - расширение функциональных возможностей устройства за счет классификации чисел по совокупным признакам.

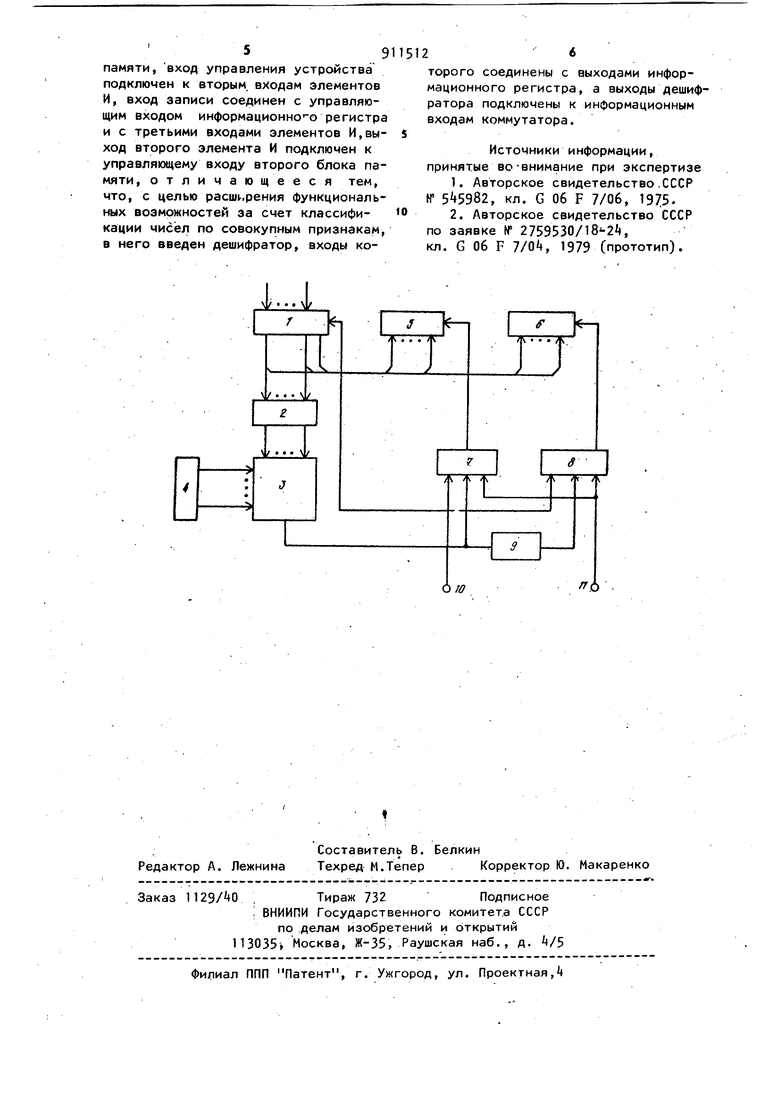

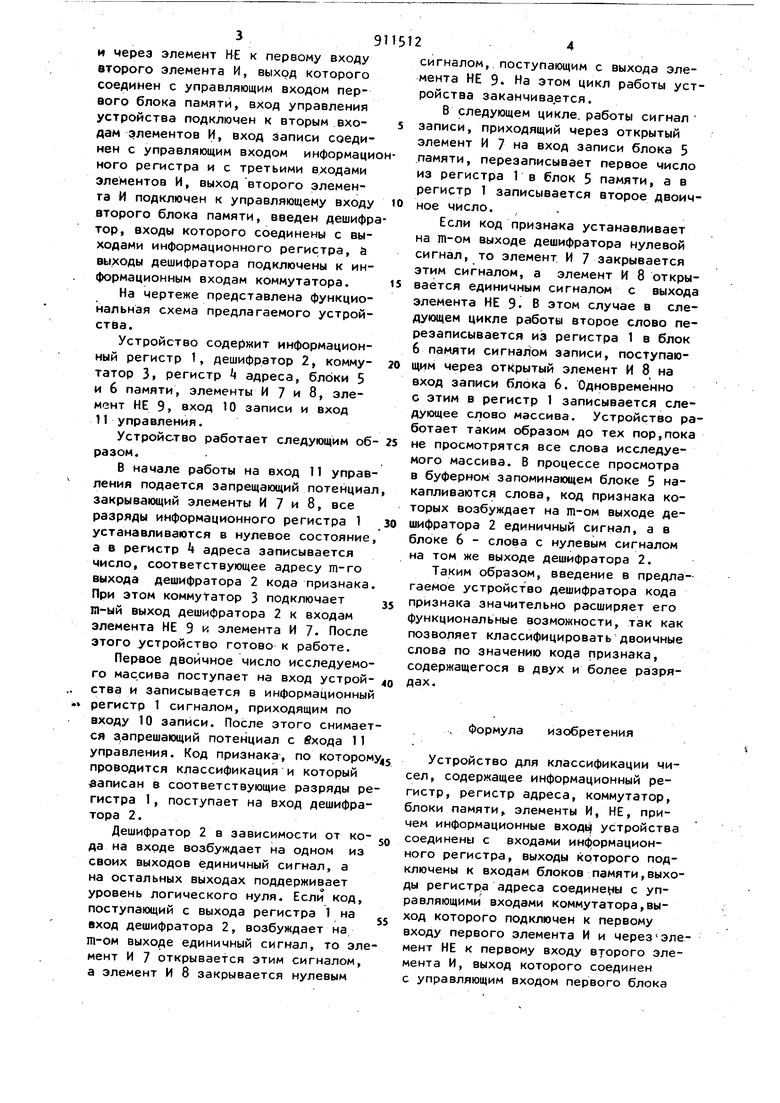

Поставленная цель достигается тем, что в устройство для классификации двоичных чисел, содержащее информационный регистр, регистр адреса, коммутатор, блоки памяти,элементы И, НЕ, причем информационные входы устройству соединены с входами информационного регистра,выходы которого подключены к входам блокрв памяти, выходы регистра адреса соединены с управляющими входами коммутатора, выход которого подключен к первому входу первого элемента И и через элемент НЕ к первому входу второго элемента И, выход которого соединен с управляющим входом первого блока памяти, вход управления устройства подключен к вторым входам элементов И, вход записи соединен с управляющим входом информацио ного регистра и с третьими входами элементов И, выход второго элемента И подключен к управляющему входу второго блока памяти, введен дешифра тор, входы которого соединены с выходами информационного регистра, а выходы дешифратора подключены к информационным входам коммутатора. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит информационный регистр t, дешифратор 2, коммутатор 3f регистр адреса, блбки 5 и 6 памяти, элементы И 7 и 8, элемент НЕ 9, вход 10 записи и вход 11 управления. Устройство работает следующим образом. В начале работы на вход 11 управления подается запрещающий потенциал закрывающий элементы И 7 и 8, все разряды информационного регистра 1 устанавливаются в нулевое состояние а в регистр k адреса записывается число, соответствующее адресу т-го выхода дешифратора 2 кода признака При этом коммутатор 3 подключает ia-ый выход дешифратора 2 к входам элемента НЕ 9 и элемента И 7. После этого устройство готово к работе. Первое двоичное число исследуемого массива поступает на вход устрой ства и записывается в информационный регистр 1 сигналом, приходящим по входу 10 записи. После этого снимае ся з,апрешающий потенциал с бхода 11 управления. Код признака, по котором проводится классификация и который написан в соответствующие разряды р гистра 1, поступает на вход дешифра тора 2. Дешифратор 2 в зависимости от ко да на входе возбуждает на одном из своих выходов единичный сигнал, а на остальных выходах поддерживает уровень логического нуля. Если код, поступающий с выхода регистра 1 на вход дешифратора 2, возбуждает на т-ом выходе единичный сигнал, то эл мент И 7 открывается этим сигналом, а элемент И 8 закрывается нулевым 9 сигналом, поступающим с выхода элемента НЕ 9. На этом цикл работы устройства заканчивается. В следующем цикле, работы сигнал записи, приходящий через открытый элемент И 7 на вход записи блока 5 памяти, перезаписывает первое число из регистра 1 в блок 5 памяти, а в регистр 1 записывается второе двоичное число. Если код признака устанавливает на т-ом выходе дешифратора нулевой сигнал, то элемент И 7 закрывается этим сигналом, а элемент И 8 открывается единичным сигналом с выхода элемента НЕ 9. В этом случае в следующем цикле работы второе слово перезаписывается из регистра 1 в блок 6 памяти сигналом записи, поступающим через открытый элемент И 8 на вход записи блока 6. Одновременно с этим в регистр 1 записывается следующее слово массива. Устройство работает таким образом до тех пор,пока не просмотрятся все слова исследуемого массива. В процессе просмотра в буферном запоминающем блоке 5 накапливаются слова, код признака которых возбуждает на т-ом выходе дешифратора 2 единичный сигнал, а в блоке 6 - слова с нулевым сигналом на том же выходе дешифратора 2. Таким образом, введение в предлагаемое устройство дешифратора кода признака значительно расширяет его функциональные возможности, так как позволяет классифицировать двоичные слова по значению кода признака, содержащегося в двух и более разрядах. . Формула изобретения Устройство для классификации чисел, содержащее информационный регистр, регистр адреса, коммутатор, блоки памяти, элементы И, НЕ, причем информационные входЦ устройства соединены с входами информационного регистра, выходы которого подключены к входам блоков памяти,выходы регистр,а адреса соедине ы с управляющими входами коммутатора,выход которого подключен к первому входу первого элемента И и черезэлемент НЕ к первому входу второго элемента И, выход которого соединен с управляющим входом первого блока

591

памяти, вход управления устройства подключен к вторым, входам элементов И, вход записи соединен с управляющим входом информационно о регистра и с третьими входами элементов И,выход второго элемента И подключен к управляющему входу второго блока памяти, отличающееся тем, что, с целью pacш.peния функциональных возможностей за счет классификации чисел по совокупным признакам, в него введен дешифратор, входы ко1512«

торого соединены с выходами информационного регистра, а выходы дешифратора подключены к информационным входам коммутатора.

S

Источники информации, принятые во-внимание при экспертизе

О 2, Авторское свидетельство СССР по заявке (f 2759530/18-2, кл. G 06 F , 1979 (прототип).

гт

/Г .6

Q Ш

Авторы

Даты

1982-03-07—Публикация

1980-03-07—Подача