I

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам.

Известно запоминающее устройство, содержащее регистр адреса, дешифратор адреса, блок разрядных цепей, блок контро ля, блок управления и блок памяти 1. Запоминающие элементы памяти в данном устройстве резервируются либо блоком постоянной памяти, который исправляет неисправные запоминающие элементы, либо блокам ассоциативной памяти, который производит переадресацию неисправных чисел оперативного запоминающего устройства.

Наиболее близким по технической сущности является запоминающее устройство, содержащее регистр адреса, дещифратор, блок разрядных цепей, блок контроля, блок управления, а также ассоциативный блок памяти, состоящий из признаковой и информационной частей. Выходы регистра адреса соединены с дещифратором и со входами признаковой части ассоциативного блока памяти, который соединен с блоком управления. В признаковой части ассоциативного блока памяти записываются адреса отказавщих слов оперативного запоминающего устройства, а в информационной части записывается содержимое этих отказавщих слов. В случае обращения к отказавшему слову, адрес которого записан в признаковой части, обращение осуществляется к информационной части ассоциативного блока памяти 2

Недостаток такого устройства - излишняя избыточность, обусловленная тем, что при наличии отказа хотя бы одного какоголибо слова производится замена всего слова, т. е. разрядность слова информационной части ассоциативного блока памяти равна разрядности слова оперативного запоминаюц его устройства.

Цель изобретения - упрощение устройства и повышение его надежности.

Цель достигается тем, что в оперативное запоминающее устройство, содержащее регистр адреса, подключенный, через блок памяти ассоциативных признаков к соединенным последовательно блоку управления и 20 блоку контроля, а через дешифратор - к накопителю, к которому подключен блок разрядных формирователей, введены дополнительный дешифратор и коммутаторы, один из входов которых соединен с выходом дополнительного дешифратора, вход которого соединен с одним выходом блока .памяти ассоциативных нризнаков, соответствующий вход которого соединен с выходом первого коммутатора, вход которого подключен к соответствуюш,ему выходу блока разрядных формирователей, выход которого соединен с одним из входов второго коммутатора, другой вход которого соединен с другим выходом блока памяти ассоциативных признаков, а выход второго коммутатора подключен к блоку контроля.

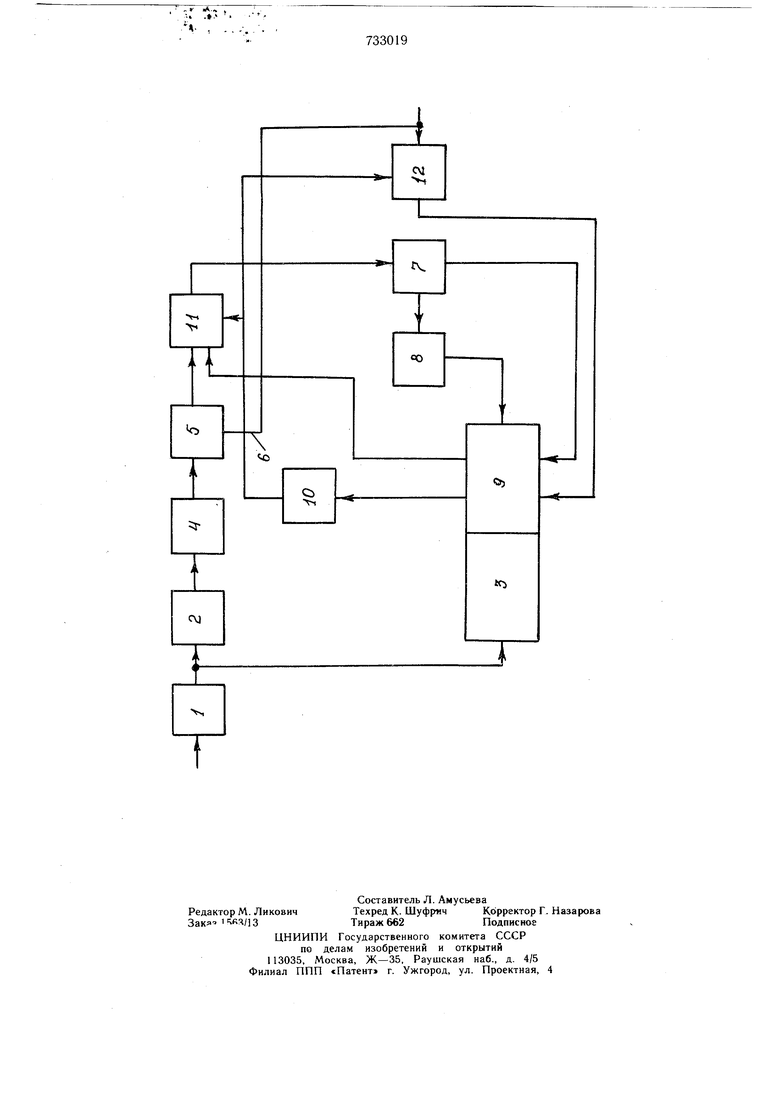

На чертеже представлена блок-схема оперативного запоминающего устройства.

Оперативное, запоминающее устройство содержит регистр 1 адреса, на вход которого подается код адреса. Выход регистра соединен со входами первого дешифратора 2 и со входами признаковой части ассоциативного блока 3 памяти. Выходы первого дешифратора 2 соединены с соответствующими входами накопителя 4, выходы которого соединены с блоком 5 разрядных формирователей на информационный вход 6 которого подается код числа, записываемый в оперативное запоминающее устройство. Кроме того, выход блока 7 контроля соединен со входом блока 8 управления и с информационной частью ассоциативного блока 9 памяти, соединенной с выходом блока 8 управления. Устройство дополнительно содержит второй дешифратор 10 и коммутаторы 11 и 12. Вход второго дешифратора 10 соединен с информационной частью ассоциативного запоминающего устройства 9, а выходс управляющими входами коммутаторов 11 и 12, причем одни входы выходных коммутаторов 11 соединены с выходами блока разрядных формирователей 5, а другие входы соединены с информационной частью ассоциативного блока 9 памяти, причем выходы выходных коммутаторов 11 соединены с блоками 7 контроля, при этом выход входного коммутатора 12 соединен с информационной частью ассоциативного блока 9 памяти, а его вход соединен с информационным входом 6 блока 5 разрядных формирователей. Устройство работает следующим образом. В режиме «запись или «считывание код адреса запрашиваемого слова накопителя 4 подается в регистр 1 адреса. Код адреса с выхода регистра 1 адреса подается на первый дешифратор 2 и на признаковую часть ассоциативного блока 3 памяти. Первый дешифратор 2 выбирает требуемое слово в накопителе 4. При этом в режиме «запись на информационный вход 6 блока 5 разрядных формирователей подается код числа, который записывается в выбранное слово накопителя 4, а в режиме «считывание, если блок 7 контроля не обнаружил ошибки, информация считывается из выбранного слова накопителя 4 через блок 5 разрядных формирователей и появляется на выходах коммутаторов И.

В случае наличия отказавших запоминающих элементов в каком-либо слове накопителя 4 при считывании информации блок 7 контроля обнаруживает ошибку и определяет номер байта слова (в двоично.м коде), в котором обнаружен отказ. При обнаружении отказа блок 7 контроля вырабатывает сигнал для блока 8 управления, который, в свою очередь, выдает сигнал на запись кода адреса слова, в котором обнаружен отказ, из регистра 1 адреса в признаковую часть ассоциативного блока 3 памяти (признаковая часть заполняется адресами неисправных слов последовательно). Кроме этого блок 8 управления выдает сигнал на запись из блока 7 контроля номера неисправного байта в информационную часть ассоциативного блока 3 памяти. Таким образом производится запоминание кода адреса слова и номера одного из его байтов, в котором обнаружен отказ.

В дальнейшем при обращении к какомулибо слову оперативного запоминающего устройства код адреса с выхода регистра 1 адреса подается одновременно во все слова признаковой части ассоциативного блока 3 памяти. Если ни один из кодов адресов, хранящихся в признаковой части ассоциативного блока памяти, не совпадает с пришедшим кодом адреса (это означает, что производится обращение к исправному слову), то первый дешифратор 2 выбирает соответствующее слово в накопителе 4 и происходит обычная работа оперативного запоминающего устройства. Если в одном из слов признаковой части ассоциативного блока 3 памяти хранящийся код адреса и пришедший код адреса совпадают, это означает, что производится обрашение к неисправному слову. При совпадении этих кодов в режиме записи из слова информационной части ассоциативного блока 9 памяти, соответствующего слову признаковой части блока 3, в котором произошло совпадение кодов, производится считывание номера байта в двоичном коде, в котором обнаружен отказ. Информация, которую необходимо записать в накопитель 4, подается на информационный вход 6 блока 5 разрядных формирователей. Двоичный код номера байта, в котором обнаружен отказ, подается на вход второго дешифратора 10, с выхода которого подается сигнал на управляюший вход коммутатора 12. Под действием этого сигнала коммутатор выбирает из входной информации, подаваемой на информационный вход 6, байт информации под тем номером, который совпадает с номером байта, в котором обнаружен отказ. Этот байт информации с выхода коммутатора записывается в то слово информационной части ассоциативного блока 9 памяти, которое соответствует слову признаковой части блока 3, в котором произошло совпадение кодов, при этом вся входная информация, поданная

на информационный вход 6, записывается в то слово накопителя 4, к которому производилось обращение по записи. Таким образом, в режиме записи при обращении к слову, в котором обнаружен отказ, входная информация записывается в это слово и наряду с этим в информационную часть ассоциативного запоминающего устройства 9 записывается тот байт входной информации, который соответствует тому байту, в котором имеется отказ.

При совпадении прощедшего и хранящегося в признаковой части 3 кодов в режиме считывания (то есть при обращении в режиме считывания к неисправному слову накопителя 4) из соответствующего слова информационной части блока 9 считывается номер байта, в котором обнаружен отказ, а также записанный в режиме записи байт информации, номер которого совпадает с номером байта, в котором имеется отказ, при этом происходит считывание информации из накопителя 4. Через блок разрядных цепей 5 информация, считанная из накопителя 4, подается на входы коммутаторов 11 (количество коммутаторов равно количеству байтов в слове накопителя 4 - по одному коммутатору на один байт). Считанный из информационной части блока 9 двоичный код номера неисправного байта подается на второй дешифратор 10, который, в свою очередь, выдает сигнал на управляющий вход одного из коммутаторов 11, который соответствует тому байту информации, в котором обнаружен отказ. При этом из информационной части блока 9 считывается и подается на вход коммутаторов 11 байт информации, который предназначен для замены того байта информации, считанного из накопителя 4, в котором обнаружен отказ.

Таким образом, вся информация, считанная из слова накопителя 4, проходит через коммутатор 11 за исключением того байта, в котором имеется отказ. Этот байт с помощью соответствующего коммутатора (одного из коммутаторов 11) заменяется байтом информации из информационной части ассоциативного запоминающего устройства 9, в результате чего на вы.ходе оперативного запоминающего устройства присутствует только правильная информация.

Формула изобретения

Оперативное запоминающее устройство, содержащее регистр адреса, подключенный через блок памяти ассоциативных признаков к соединенным последовательно блоку

5 управления и блоку контроля, а через дещифратор - к накопителю, к которому подключен блок разрядных формирователей. отличающееся тем, что, с целью упрощения устройства и повышения его надежности, оно содержит дополнительный дещифратор и коммутаторы, один из входов которых соединен с выходом дополнительного дещифратора, вход которого соединен с одним из выходов блока памяти ассоциативных признаков, соответствующий вход которого соеS динен с выходом первого коммутатора, вход которого подключен к соответствующему выходу блока разрядных формирователей, выход которого соединен с одним из входов второго коммутатора, другой вход которого соединен с другим выходом блока памяти ассоциативных признаков, а выход второго коммутатора подключен к блоку контроля.

Источники информации, принятые во внимание при экспертизе

1.Патент США Л 3501748, кл. 340-172.5 17.03.70.

2.Патент ФРГ Л 1290973, кл. 21 а 37/66, 13.11.69.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1975 |

|

SU653624A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU970479A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

Авторы

Даты

1980-05-05—Публикация

1976-12-08—Подача