.- 25

ИзобрЕ -тение относится к средствам реобразования информации и может ыть использовано при построении раионавигационных систем.

Целью изобретения является повы- ение точности преобразования и расирение класса решаемых задач за счет обеспечения возможности изменения веса единицы младшего разряда и возможности обеспечения начальной ус-fO тановки.

На фиг. 1 приведена блок-схема предлагаемого преобразователя; на фиг. 2 - функциональная схема корректирующего формирователя задержки; на 5 фиг. 3 - функциональные схемы преобразователя временного интервала в код и управляемого элемента задержки; на фиг. 4 - временные диаграммы работы предложенного преобразова- 20 теля.

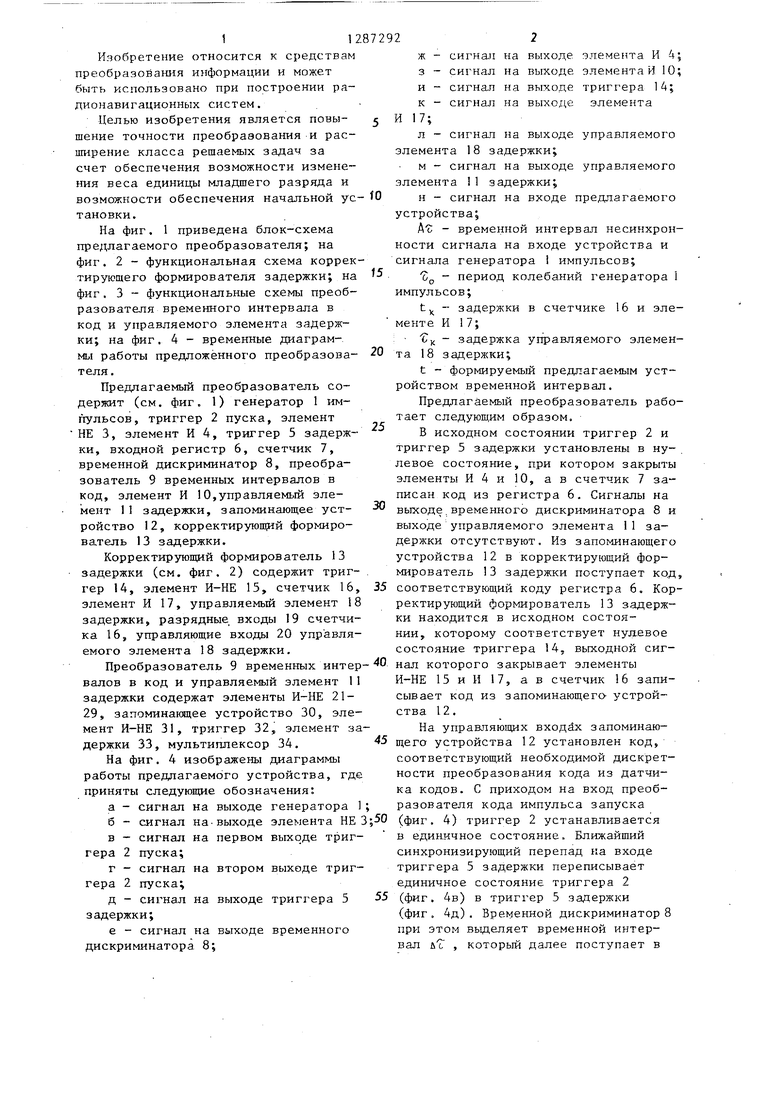

Предлагаемый преобразователь содержит (см. фиг. 1) генератор 1 импульсов, триггер 2 пуска, элемент НЕ 3, элемент И 4, триггер 5 задерж ки, входной регистр 6, счетчик 7, временной дискриминатор 8, преобразователь 9 временных интервалов в код, элемент И 10,управляемый элемент 1 1 задержки, запоминающее уст- -30 ройство 2, корректирующий формирователь 13 задержки.

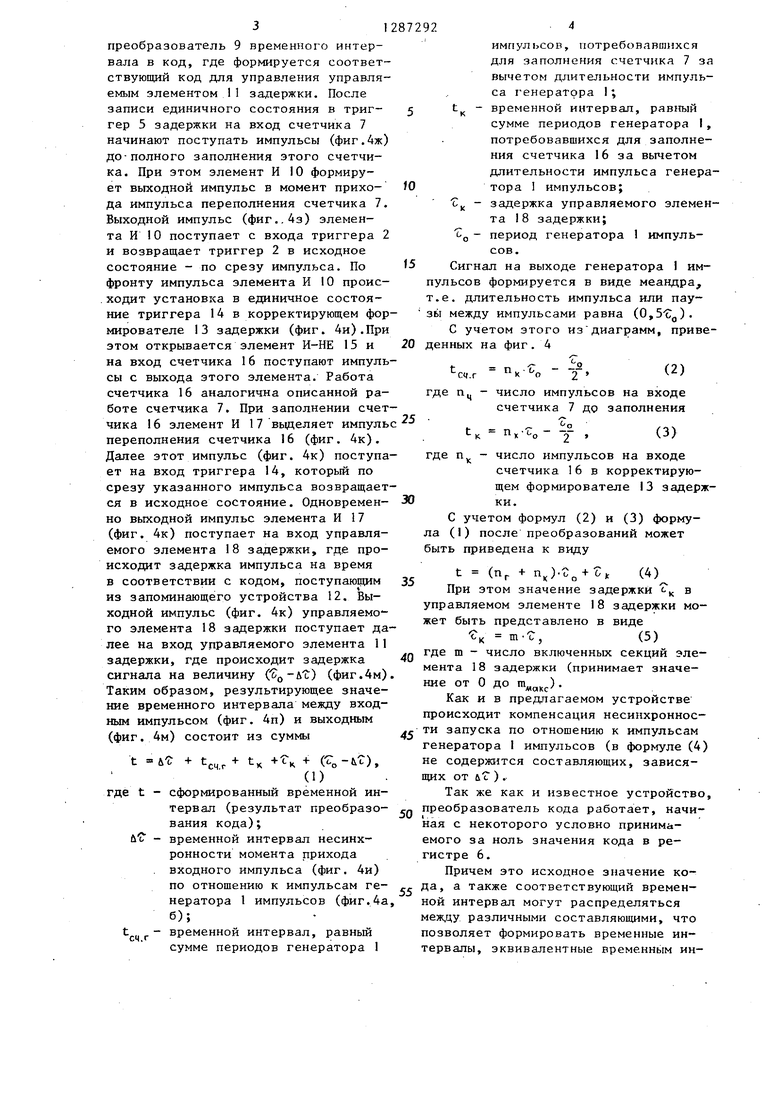

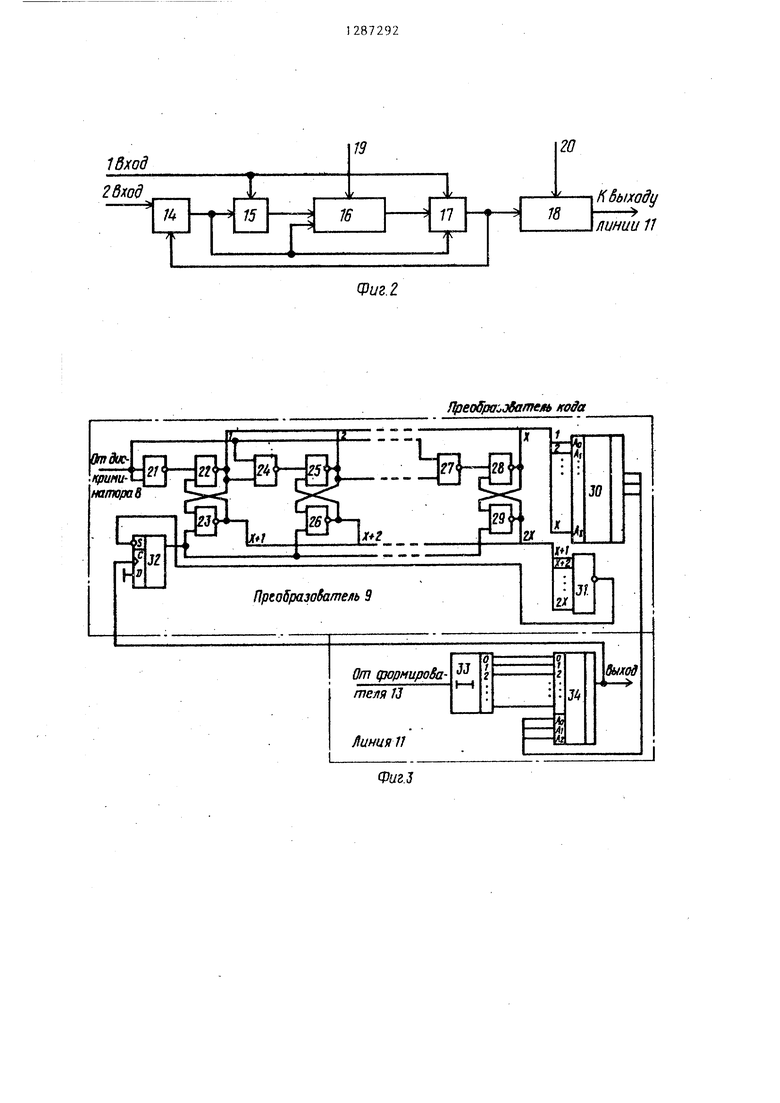

Корректирующий формирователь 13 задержки (см. фиг. 2) содержит триггер 14, элемент И-НЕ 15, счетчик 16, 35 элемент И 17, управляемый элемент 18 задержки, разрядные входы 19 счетчика 16, управляющие входы 20 управляемого элемента 18 задержки.

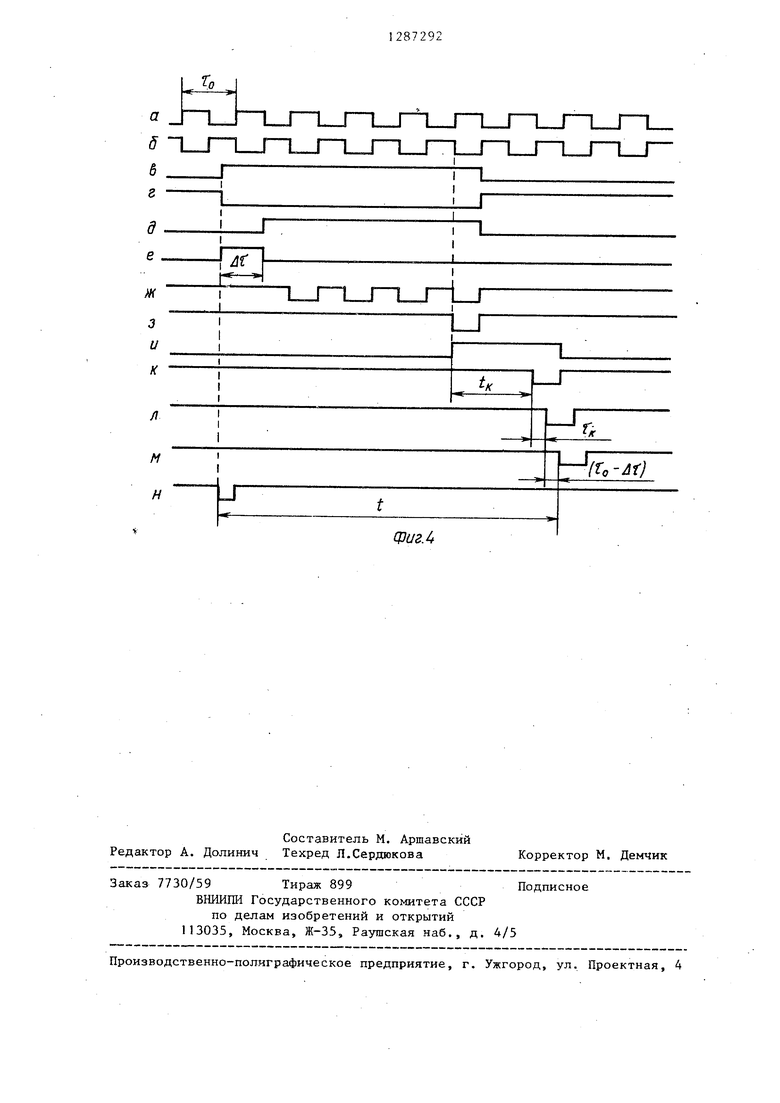

Преобразователь 9 временных интер- 0 валов в код и управляемый элемент 1I задержки содержат элементы И-НЕ 21- 29, запоминакядее устройство 30, элемент И-НЕ 31, триггер 32, элемент задержки 33, мультиплексор 34.

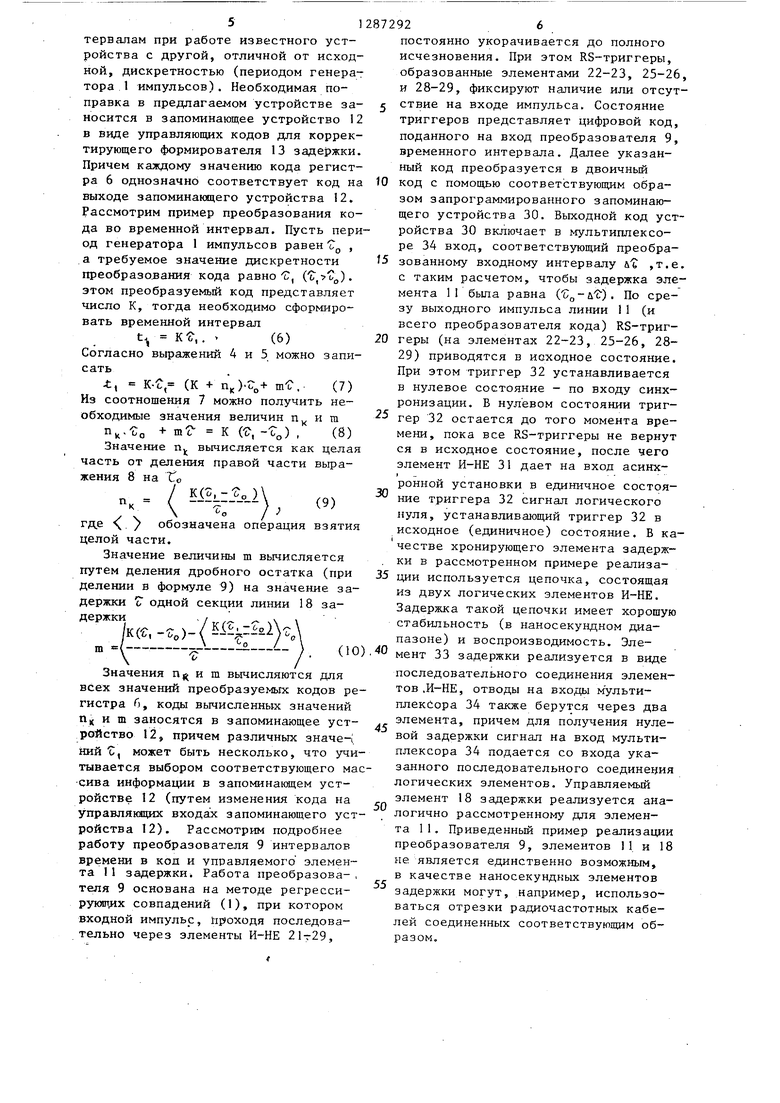

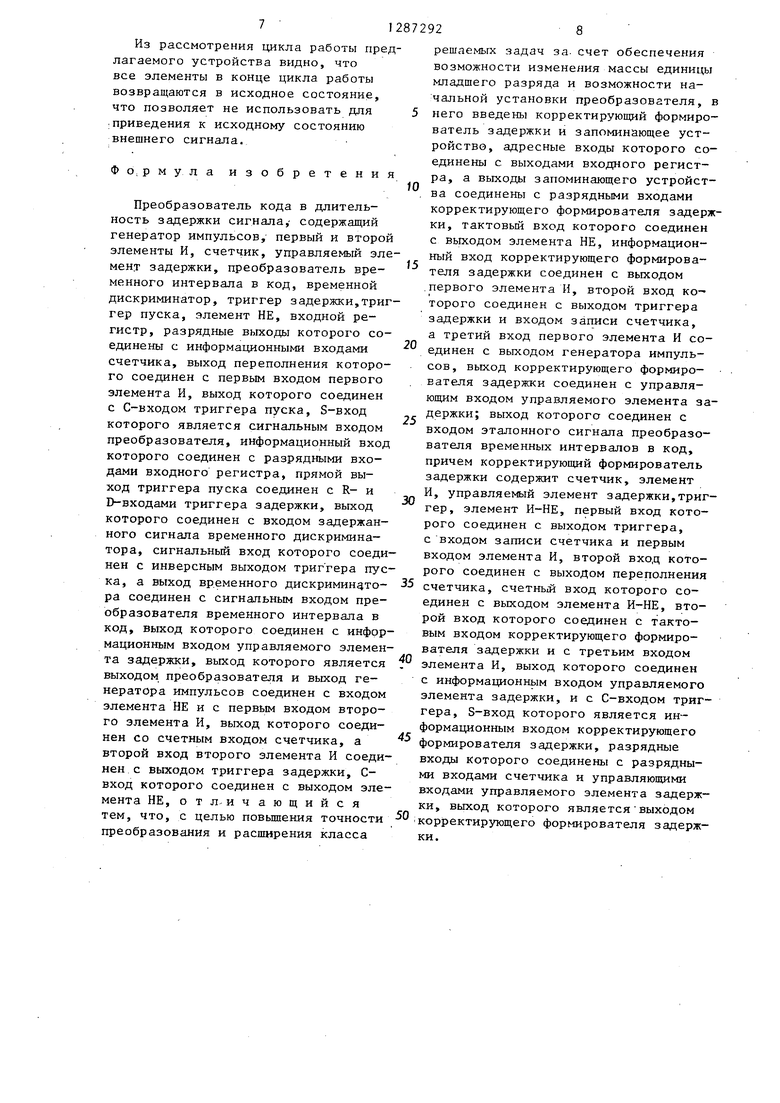

На фиг. 4 изображены диаграммы работы предлагаемого устройства, где приняты следуюпще обозначения:

а - сигнал на выходе генератора 1; б - сигнал на-выходе элемента НЕ 3;50 в - сигнал на первом выходе триггера 2 пуска;

г - сигнал на втором выходе триггера 2 пуска;

д - сигнал на выходе триггера 5 55 задержки;

е - сигнал на выходе временного дискриминатора 8;

45

25

fO

520

-30

35

; ;50 55

45

ж - сигнал на выходе злемеята И 4;

3 - сигнал на выходе элемента И 10;

и - сигнал на выходе триггера 14;

к - сигнал на выходе элемента И 17;

л - сигнал на выходе управляемого элемента 18 задержки;

м - сигнап на выходе управляемого элемента 11 задержки;

н - сигнал на входе предлагаемого устройства;

А о - временной интервал несинхронности сигнала на входе устройства и сигнала генератора i импульсов;

Ор - период колебаний генератора 1 импульсов;

t - задержки в счетчике 16 и элементе И 17;

Си - задержка управляемого элемента 18 задержки;

t - формируемый предлагаемым устройством временной интервал.

Предлагаемый преобразователь работает следующим образом.

В исходном состоянии триггер 2 и триггер 5 задержки установлены в нулевое состояние, при котором закрыты элементы И 4 и 10, а в счетчик 7 записан код из регистра 6. Сигналы на выходе,временного дискриминатора 8 и выходе управляемого элемента 11 задержки отсутствуют. Из запоминающего устройства 12 в корректирующий формирователь 13 задержки поступает код, соответствующий коду регистра 6. Корректирующий формирователь 13 задержки находится в исходном состоянии, которому соответствует нул.евое состояние триггера 14. выходной сигнал которого закрывает элементы И-НЕ 15 и И 17, а в счетчик 16 записывает код из запоминающего- устройства 12.

На управляющих входйх запоминающего устройства 12 установлен код, соответствующий необходимой дискретности преобразования кода из датчика кодов. С приходом на вход преобразователя кода импульса запуска (фиг. 4) триггер 2 устанавливается в единичное состояние. Ближайший синхронизирующий перепад на входе триггера 5 задержки переписывает единичное состояние триггера 2 (фиг. 4в) в триггер 5 задержки (фиг, 4д). Временной дискриминатор В при этом вьщеляет временной интервал дТ , который далее поступает в

31

преобразователь 9 временного интервала в код, где формируется соответствующий код для управления управляемым элементом 11 задержки. После записи единичного состояния в триг- гер 5 задержки на вход счетчика 7 начинают поступать импульсы (фиг.4ж) до-полного заполнения этого счетчика. При этом элемент И 10 формирует выходной импульс в момент прихода импульса переполнения счетчика 7. Выходной импульс (фиг..4з) элемента И 10 поступает с входа триггера 2 и возвращает триггер 2 в исходное состояние - по срезу импульса. По фронту импульса элемента И 10 происходит установка в единичное состояние триггера 14 в корректирующем формирователе 13 задержки (фиг. 4и).При этом открывается элемент И-НЕ 15 и на вход счетчика 16 поступают импульсы с выхода этого элемента. Работа счетчика 16 аналогична описанной работе счетчика 7, При заполнении счетчика 16 элемент И 17 выделяет импуль переполнения счетчика 16 (фиг. 4к). Далее этот импульс (фиг. 4к) поступает на вход триггера 14, который по срезу указанного импульса возвращается в исходное состояние. Одновремен- но выходной импульс элемента И 17 (фиг. 4к) поступает на вход управляемого элемента 18 задержки, где происходит задержка импульса на время в соответствии с кодом, поступающим из запоминающего устройства 12. Выходной импульс (фиг. 4к) управляемого элемента 18 задержки поступает далее на вход управляемого элемента 11 задержки, где происходит задержка сигнала на величину () (фиг.4м) Таким образом, результирующее значение временного интервала между входным импульсом (фиг. 4п) и выходным (фиг. 4м) состоит из суммы

&-

+ сч.. +

+ К + (0-Ь), (1)

де t - сформированный временной интервал (результат преобразования кода);

й - временной интервал несинхронности момента прихода . входного импульса (фиг. 4и) по отношению к импульсам генератора 1 импульсов (фиг.4а, б);

временной интервал, равный сумме периодов генератора 1

сч.г

импульсов, потребовавшихся для заполнения счетчика 7 за вычетом длительности импульса генератора 1; t - временной интервал, равный

сумме периодов генератора I, потребовавшихся для заполнения счетчика 16 за вычетом длительности импульса генератора I импульсов;

Cj, - задержка управляемого элемента 18 задержки;

- период генератора 1 импульсов.

Сигнал на выходе генератора 1 импульсов формируется в виде меандра, т.е. длительность импульса или паузы между импульсами равна (O.Sirg).

С учетом этого из диаграмм, приведенных на фиг. 4

-сч.г

п,

о

(2)

где Пц - число импульсов на входе счетчика 7 др заполнения

п,

(3)

где п - число импульсов на входе

счетчика 16 в корректирующем формирователе 13 задержки.

С учетом формул (2) и (3) формула (I) после преобразований может быть приведена к виду

5 20 30

35

t (п + nJ. (4) При этом значение задержки управляемом элементе 18 задержки жет быть представлено в виде

- m

(5)

где m - число включенных секций элемента 18 задержки (принимает значе- ние от О до га„„,р.

Как и в предлагаемом устройстве происходит компенсация несинхроннос- ти запуска по отношению к импульсам

генератора I импульсов (в формуле (4) не содержится составляющих, зависящих от ьТ ).

Так же как и известное устройство, преобразователь кода работает, начиная с некоторого условно принимаемого за ноль значения кода в регистре 6.

Причем это исходное значение коа, а также соответствующий временной интервал могут распределяться еж,цу различными составляющими, что позволяет формировать временные интервалы, эквивалентные временным интервалам при работе известного устройства с другой, отличной от исходной, дискретностью (периодом генератора 1 импульсов). Необходимая поправка в предлагаемом устройстве заносится в запоминающее устройство 12 в виде управляюгцих кодов для корректирующего формирователя 13 задержки. Причем каждому значению кода регистра 6 однозначно соответствует код на выходе запоминающего устройства 12. Рассмотрим пример преобразования кода во временной интервал. Пусть период генератора 1 импульсов равен o , а требуемое значение дискретности преобразования кода равной, ( сГ,). этом преобразуемьш код представляет число К, тогда необходимо сформировать временной интервал

(6) 5 можно запиt К -с,.

Согласно выражений 4 сать

Л, К-С (К + п..

) +

Из соотношения 7 можно

(7)

получить неп„

(9)

обходимые значения величин п и m п.-оо + т К С, --г:.,) , (8) Значение п вычисляется как целая

часть от деления правой части вьфажения 8 на

К(о,)

- - ) .

гд.е . / обозначена операция взятия целой части.

Значение величины m вычисляется путем деления дробного остатка (при делении в формуле 9) на значение задержки сГ одной секции линии 18 задержки - / vf K(€.-irj-(

О /

m

(10

Значения п и m вычисляются для всех значений преобразуемых кодов регистра 5, коды вычисленных значений П)( и m заносятся в запоминающее уст- ройство 12, причем различных значе-(, НИИ о, может быть несколько, что учи

тывается выбором соответствующего массива информации в запоминающем устройстве 12 (путем изменения кода на управляющих входах запоминающего устройства 12). Рассмотрим подробнее работу преобразователя 9 интервалов времени в код и управляемого элемента 1I задержки Работа преобразова- , теля 9 основана на методе регресси- рукяцих совпадений (1), при котором входной импульс, проходя последовательно через злементы И-НЕ ,

10

15

20

ле872926

постоянно укорачивается до полного исчезновения. При этом RS-триггеры, образованные элементами 22-23, 25-26, и 28-29, фиксируют наличие или отсут5 ствие на входе импульса. Состояние триггеров представляет цифровой код, поданного на вход преобразователя 9, временного интервала. Далее указанный код преобразуется в двоичный код с помощью соответствующим образом запрограммированного запоминающего устройства 30. Выходной код устройства 30 включает в мультиплексоре 34 вход, соответствующий преобразованному входному интервалу л ь ,т.е. с таким расчетом, чтобы задержка элемента II бьша равна (). По срезу выходного импульса линии 11 (и всего преобразователя кода) RS-триггеры (на элементах 22-23, 25-26, 28- 29) приводятся в исходное состояние. При этом триггер 32 устанавливается в нулевое состояние - по входу синхронизации. Б нулевом состоянии триг 5 гер 32 остается до того момента времени, пока все RS-триггвры не вернут ся в исходное состояние, после чего элемент И-НЕ 31 дает на вход асинхронной установки в единичное состоя-

ние триггера 32 сигнал логического нуля, устанавливающий триггер 32 в исходное (единичное) состояние. В ка- честве хронирующего элемента задерж- . ки в рассмотренном примере реализа35 ции используется цепочка, состоящая из двух логических элементов И-НЕ. Задержка такой цепочки имеет хорошую стабильность (в наносекундном диапазоне) и воспроизводимость. Элемент 33 задержки реализуется в виде последовательного соединения элементов ,И-НЕ, отводы на входы 1ульти- плекСора 34 также берутся через два элемента, причем для получения нулевой задержки сигнал на вход мультиплексора 34 подается со входа указанного последовательного соединения логических элементов. Управляемый элемент 18 задержки реализуется аналогично рассмотренному для элемента 11. Приведенный пример реализации преобразователя 9, элементов 11 и 18 не является единственно возможным, в качестве наносекундных элементов задержки могут, например, использоваться отрезки радиочастотных кабелей соединенных соответствующим образом.

,40

50

55

7 1287292

Из рассмотрения цикла работы предагаемого устройства видно, что се элементы в конце цикла работы озвращаются в исходное состояние, то позволяет не использовать для риведения к исходному состоянию нешнего сигнала.

ре во мл ча не ва ро ед ра ва ко ки с ны те .пе то за а ед со ва ющ де вх ва пр за И, ге ро с вх ро сч ед ро вы ва эл с эл ге фо фо вх ми вх ки

Фо.рмула изобретения

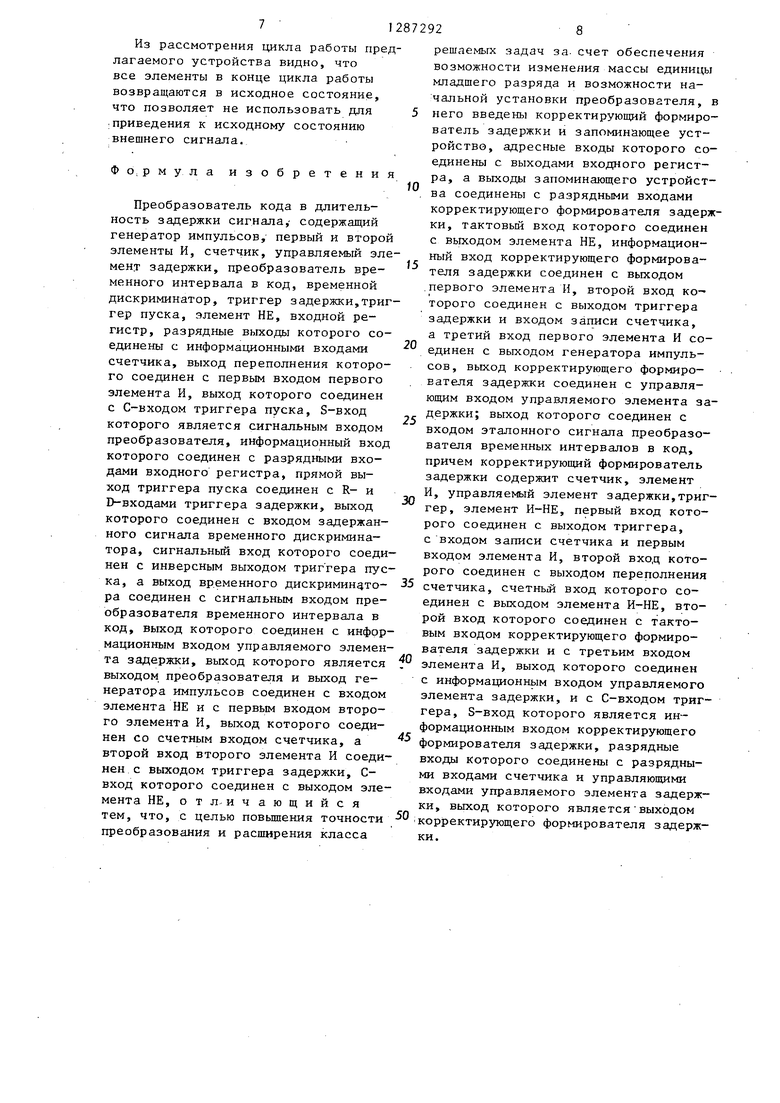

Преобразователь кода в длительность задержки сигнала,- содержащий генератор импульсов, первый и второй элементы И, счетчик, управляемый элемент задержки, преобразователь временного интервала в код, временной дискриминатор, триггер задержки,триггер пуска, элемент НЕ, входной регистр, разрядные выходы которого соединены с информационными входами счетчика, выход переполнения которого соединен с первым входом первого элемента И, выход которого соединен с С-входом триггера пуска, S-вход которого является сигнальным входом преобразователя, информационный вход которого соединен с разрядными входами входного регистра, прямой выход триггера пуска соединен с R- и D-входами триггера задержки, выход которого соединен с входом задержанного сигнала временного дискриминатора, сигнальный вход которого соединен с инверсным выходом триггера пуска, а выход временного дискримин то- ра соединен с сигнальным входом преобразователя временного интервала в код, выход которого соединен с информационным входом управляемого элемента задержки, выход которого является выходом преобразователя и выход генератора импульсов соединен с входом элемента НЕ и с первым входом второго элемента И, выход которого соединен со счетным входом счетчика, а второй вход второго элемента И соединен с выходом триггера задержки, С- вход которого соединен с выходом элемента НЕ, отл-ичающийся тем, что, с целью повьшения точности преобразования и расширения класса

8

O

5

0

5

0

5

0

5

0

решаемых задач за. счет обеспечения возможности изменения массы единицы младшего разряда и возможности начальной установки преобразователя, в него введены корректирующий формирователь задержки и запоминающее устройстве, адресные входы которого соединены с выходами входного регистра, а выходы запоминающего устройства соединены с разрядными входами корректирующего формирователя задержки, тактовый вход которого соединен с выходом элемента НЕ, информационный вход корректирующего формирователя задержки соединен с выходом .первого элемента И, второй вход которого соединен с выходом триггера задержки и входом записи счетчика, а третий вход первого элемента И соединен с выходом генератора импульсов, выход корректирующего формирователя задержки соединен с управляющим входом управляемого элемента задержки; выход которого соединен с входом эталонного сигнала преобразователя временных интервалов в код, причем корректирующий формирователь задержки содержит счетчик, элемент И, управляемый элемент задержки,триггер, элемент И-НЕ, первый вход которого соединен с выходом триггера, с входом записи счетчика и первым входом элемента И, второй вход которого соединен с выходом переполнения счетчика, счетньгй вход которого соединен с выходом элемента И-НЕ, второй вход которого соединен с тактовым входом корректирующего формирователя задержки и с третьим входом элемента И, выход которого соединен с информационнь1м входом управляемого элемента задержки, и с С-входом триггера, S-вход которого является информационным входом корректирующего формирователя задержки, разрядные входы Которого соединены с разрядными входами счетчика и управляющими входами управляемого элемента задержки, выход которого является ВЫХОДОМ

корректирующего формирователя задержки.

КЬыходу линии П

VuB.Z

еоУра: о8ате/ кода

nptoSpajoSame/ib 9

5

6 , г

д - е

ж

3

и к

л

м н

Г,

Редактор А. Долинич

Составитель М. Аршавский Техред Л.Сердюкова

Заказ 7730/59 Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская яаб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.

Корректор М. Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Система стабилизации задержки | 1981 |

|

SU957422A1 |

| Устройство задержки импульсов | 1980 |

|

SU917326A1 |

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1255984A2 |

| Способ преобразования кода угла в напряжения,пропорциональные синусу и косинусу угла, и устройство для его осуществления | 1985 |

|

SU1345346A1 |

| Преобразователь угол-код | 1988 |

|

SU1596461A1 |

| Преобразователь кода во временной интервал | 1980 |

|

SU1007054A1 |

| Формирователь импульсов | 1986 |

|

SU1383468A1 |

| ПЛКЙТНО-ИХШЕСЙА*ЬИБ;1ИО'^ЕКАГ. Л. Биланов | 1972 |

|

SU342297A1 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

Изобретение относится к средствам преобразования информации и может быть использовано при построе- нии радионавигационных систем. Целью изобретения является повьшение точности преобразования и расширение класса решаё№,1х задач за счет обеспечения возможности изменения веса единицы младшего разряда и обеспечения начальной установки. Поставленная цель достигается тем, что в преобразователь кода, содержащий счетчик 7, управляемый элемент задержки II, преобразователь 9 временного интервала в код, временной дискриминатор 8, входной регистр 6, введены корректирующий формирователь задержки I 3 и запоминающее устройство 12, выход которого соединен с входом корректирующего формирователя задержки, выход которого соединен со входом управляемого элемента задержки. 4 ил. i (Л С ue.f

| Преобразователь интервалов времени в цифровой код | 1980 |

|

SU930217A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Преобразователь кода во временной интервал | 1980 |

|

SU1007054A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-01-30—Публикация

1985-09-11—Подача