(54) ЦИФРОВОЙ СЛЕДЯЩИЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ЧАСТОТЫ И ВРЕМЕННОЙ ЗАДЕРЖКИ РАДИОСИГНАЛА | 1992 |

|

RU2048683C1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Умножитель частоты | 1986 |

|

SU1332316A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Устройство различения сигналов на фоне произвольной помехи | 1988 |

|

SU1596469A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

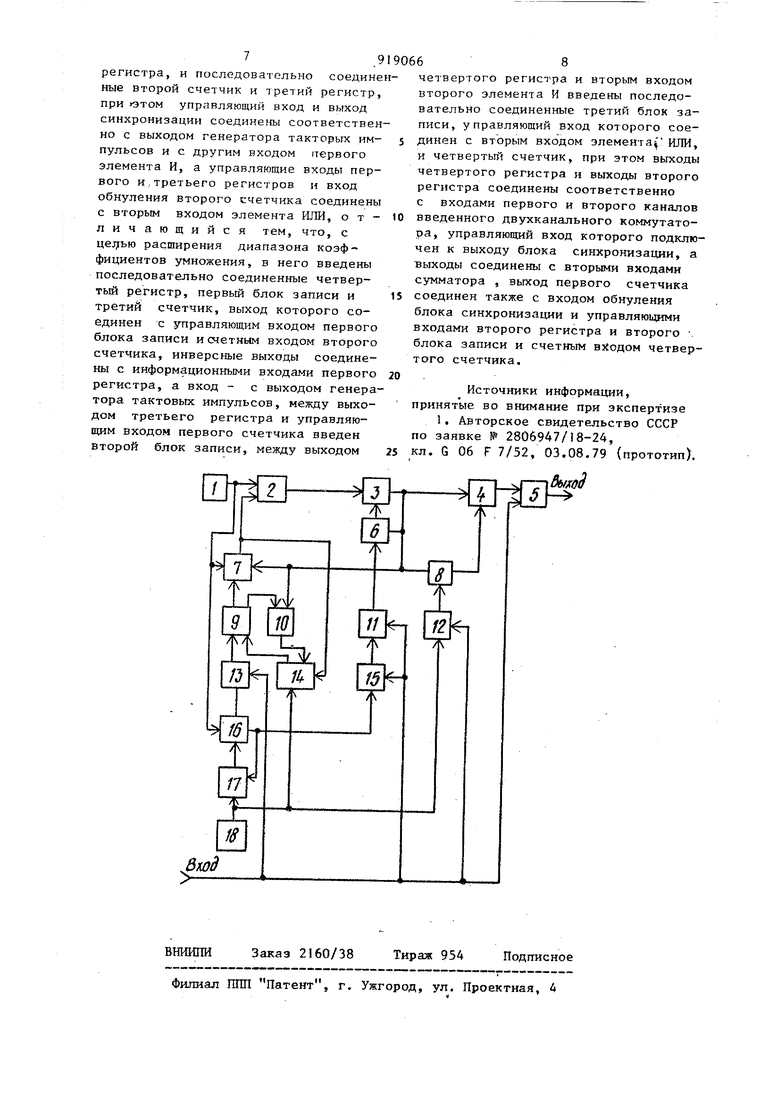

Изобретение относится к информаци онно-измерительной технике и может использоваться в качестве синхронизирующего устройства, управляющего аналого-цифровыми преобразователями в бесфильтровых анализаторах спектра, функциональных цифровых ге- нераторах и т.д. Известен цифровой следящий умно житель частоты, содержащий последова тельно соединенные генератор тактевых импульсов у первый элемент И, пер вьй счетчик, второй элемент И и элемент ИЛИ, второй вход которого яв ляется входом, а выход- выходом цифрового следящего умножителя частоты, а также последовательно соединенные первый регистр и сумматор, выход старшего разряда которого соединен с информационным входом блока синхронизации, а выходы остальных ра рядов - с информа1Ц1онны }и входами второго регистра, и последовательно, соединенные второй счетчик и третий регистр, при этом управляющий вход и выход блока синхронизации соединены соответственно с выходом генератора тактовых импульсов и с другим входом первого элемента И, а управляющие входы первого и третьего регистров и вход обнуления второго счетчика соединены с вторым входом элемента ИЛИ о Однако известный цифровой следящий умножитель частоты имеет недостаточно широкий диапазон коэффициентов умножения, так как структура входяц,его в него сумматора однознач- но определяется величиной коэффициента умножения. Цель изобретения - расширение дна- пазона коэффициентов умножения. Для достижения указанной цели в цифровой следящий умножитель частоты, содержащий последовательно соединеннь1е генератор тактовых импульсов, первый элемент И, первый счет.чик, второй элемент И и элемент ИЛИ, второй вход которого является вход а гзыход - выходом цифрового следящ го умножи еля частоты, а также пос ледовательно соединенные первьш ре гистр и С 1матор, вьгход старшего разряда которого соедине1-г с информацт-гоиным входом блока синхронизац а выходы остальных разрядов - с ин формаилопными вxoдa fи второго регистра, и последовательно соединен ные второй счетчик и третий реги при этом управляющий вход и выход блока синхронизации соединены соответс1венно с выходом генератора актовых импульсов и с другим входе - первого элемента И, а управля ои.-и;е первого и третьего ретистров н вход oGHy.neHvifi второго счетц{)ка соединень с вторым входом КРМ, г ведены последовательно соед, четвертый регистр, первь Й блок зяписи и третий счетчик 5 выход которого соедигген с управляющим входом первого блока записи и счетным вxoдo 5 второго счетчика, инверсные выходы соединены с информационными входами пер вого регистра, а вход - с выходом генератора тактовых импульсов, ме;вд выходом третьего регистра и управ- jiHfoauiM входом первого счетчика введен второй блок santiCH, между выхо лом четвертого регистра и вторым вх дом Hioporo элемена а И введеньл последов а т ель но с о еди н е иные т р е т ий блок aaiiHCi-f, управляющий вход которс го соединен с вторьм входом элемента ИЛИ, и четвертый счетчик, при это:- зьзходы четвертого регистра н выхода второго регис1ра соединень соответственно с входаш первого is Lvroporo каналов введенного двзКкааального коммутатора, управля о:щ й вход которого подключен к вьгходу блока синхрон зации а гзыходы соеди нега-; с. вторы -т входами c..iaTOipa „ выкод первого счетчика соединен так же с з:%О1,ом обнуления блока с:иихррMH3aiU H нчттравллющими входами втор го регистра н второго блока записи и счетным входом четвертого счетчика. На чертеже представлена структур ная электрическая схема предд1агае T-ioro устройства, 11ифровой следя .пий л нош-утель час тоты содерзсит генератор тактовых ь:мпуяьсов 5первь й элемент И 2, пе вый счетчик 3, второй элемент И 4,, 4 элемент ИЛИ 5, второй блок записи 6, блок 7 синхронизации, четвертый счетчик 8, сумматор 9, второй регистр 10, третий регистр 11, третий блок 12 записи, первый регистр 3, двухканлльмзш коммутатор . 14, второй счетчик 15 третий счетчик 16, первый блок 17 записи и четвертый регистр )8„ Цифровой следящий умножитель частоты работает следующим образом. От генератора I тактовых импульг,ов импульсы частотой f поступают на вход счетчика 15 через счетчик 6 н на вход счетчика 3 через элемент И 2, который пропускает практически все импульсы .Спустя промежуток времени, равный периоду исходной последовательности Т,, на вход счетчика 16 поступает определенное число имупльсов Vf В регистре 18 предварительно записьшается требуемый коэффициент умножения с Когда на выходе счетчика 16 появ ляется импульс переполнения, то дополнителыгый код шсла k переписывается через блок 17 записи в счетесли счетчик 16 разрядчнк, т, е, неге З 1писано число 2 1с ньш, то в Тогда при постуш-гении на вход счетчика 16 k импульсов он переполняется, и на его выходе появляется импульс. То е, счетчик 16 совместно с регистром 18 и блоком 17 записи выполняет функции делителя с переменньш коэффициентом деления k. Таким образоНг в счетчике 15 через промежуток време и записывается число, равное целсй части числа -у. обозначим ее 6 . находится дополниВ счетчике тельный код остатка aNik , С точ Г-ЮСТЬЮ до :f: 1 . DaBHbii завный дробной части, М С S обозначается 1 , числа --J7--5 о. По окончании первого периода вход него сиг}1ала результат дМ из счатчика 6переносится в регистр 13, а Г « 1 результат Т переносится из счетчика 5 Е регистр « В этот же --юмент обнуляется счетчик 15, Во второй период счетчик 1 5 считает аналогично ,, а результат -т- s , , L it J записанньв-т в регистр 1 , переписывается в дополнительном коде н счетчик 3 всякий раз, когде на его выходе появляется импульс. Таким образом, счетчик 3 совместно с блоко 6 записи и регистром 11 вьтолняет фу цию кодоуправляемого делителя с ко эф(1)ициентом деления . Если на вход счетчика 3 проходят все импульсы с генератора 1, то импульс на выходе его появляется каж 1дый раз через промежуток времени ,.11. Для умножения без погрешностей этот промежуток времени должен быт Г Значит, на выходе устройства i-ый импульс появляется с опережением на время ш. ut I Устранение указанной погрешности осуществляется следующим образом. Каждый импульс выхода счетчика поступает на управляющий вход регистра 10. При этом, если на выход блока 7 синхронизации нет импульса то регистр 10 подключен через коммутатор 14 ко вторым входам сумматора 9. Б сумматоре 9 при этом про водится вычисление суммь: содержимо го регстра 10 и регистра 13. В начале работы, а затем каждый раз, когда на выходе старшего разр да сумматора 9 появляется импульс, коммутатор 14 подключает.регистр 1 ко вторым входам сумматора 9. При этом в сумматоре 9 суммируется дополнительный код числа k , т.е. k , где q - количество разрядо сумматора, и число ( Импульс на выходе сумматора 9 появляется тогда, когда содержимое его превы шает 2 , т.е. сумма остатков дМ, превышает k. Этот сигнал поступае на информационный вход блока 7 син ронизации, приведенного в исходное состояние импульсом с выхода счетчика 3 и управляемого импульсами нератора 1 тактовых импульсов чере вход управления. Блок 7 синхрониза ции вырабатывает импульс длительно стью Т(з , который, приходя на один из входов элемента И 2, закрывает его на время TQ. Это прнво66дит к тому, что один импульс с выхода генератора 1 такчовых импульсов не проходит на счетный вход счетчика 3, т.е. импульс на выходе счетчика 3 появляется с задержкой Тд, Подобным образом, устраняется полностью или в большей мере опережение i,t-,, и чмпульсы появляются на выходе устройства с опережением не более, чем на Т,. С целью синхронизации и привязки пос-чеднего выходного импульса к концу периода Т„ в устройстве применен счетчик 8, который с блоком 12записи и регистром 18 представляет собой кодоуправляеьшр делитель с коэффициентом деления k Перепись дополнительного кода k производится входным 1мпульсом. Если на вход счетчнкл 8 пр1 ходит k импульсов, то на выходе счетчика 8 появляется импульс переполнения, который закрывает элемент И 4 и прекращает подачу импульсов на выход устройства., Приходящий затем импульс входной последовательности вновь устанавлкрает все элементы устройства в исходнос; положение и цикл повторяется снова. Так как независимо от величины коэс1х| Г;циента таножеии.я сумматор 9 считает до 2 , где q - количество разрядов cyм iaтopa, то устройство работоспособно при любых величинах коэффициента умножения. Таким образом, предлагаемое устройство имеет стабильный коэф-Л нц ент умноження и широкий диапазон кэменения его ве., при этом обеспечивается сравнительно простая реализаиия устройст за. Формула изоСретення Ш Фровой следпозий у июнитель част тоты, содержащий последовательно соелкненные генаратор тактовых нм пульсов, первый элемент ii, первый счетчик, второй элемент И и элемент ШШ, второй вход которого является входом, а выход - выходом цифрового следящего умножителя частоты, а также последовательно соединенные первый регистр н су.;маор, вьтход старшего разряда которого соединен с ин формацйоннкгм входом блока синхронизации, а выходы остапъны.х разрпдорс информаиионнымн вкодани второго

регистра, и последовательно соединеные второй счетчик и третий регистр, при ЭТОМ управляющий вход и выход синхрони:зации соединены соответственно с выходом генератора такторых импульсов и с другим входом первого элемента И, а управляющие входы первого и,третьего регистров и вход обнуления второго счетчика соединены с вторым входом элемента ИЛИ, о т личающийся тем, что, с расширения диапазона коэффициентов умножения, в него введены последовательно соединенные четвертый регистр, первый блок записи и третий счетчик, выход которого соединен с управляющим входом первого блока записи нечетным входом второго счетчика, инверсные выходы соединены с информационными входами первого регистра, а вход - с выходом генератора тактовых импульсов, между выходом третьего регистра и управляющим входом первого счетчика введен второй блок записи, между выходом

четвертого регис1 ра и вторым входом второго элемента И введены последовательно соединенные третий блок записи, управляющий вход которого соединен с вторым входом элемента ИЛИ, и четвертьШ счетчик, при этом выходы четвертого регистра и выходы второго регистра соединены соответственно с входами первого и второго каналов введенного двухканального коммутатора, управляющий вход которого подключен к выходу блока синхронизации, а выходы соединены с вторыми входами сумматора , выход первого счетчика соединен также с входом обнуления блока синхронизации и управляюьщми входами второго регистра и второго , блока записи и счетным входом четвертого счетчика.

Источники информации, принятые во внимание при экспертизе

1 Авторское свидетельство СССР по заявке № 2806947/18-24, кл. G 06 F 7/52, 03.08.79 (прототип).

Авторы

Даты

1982-04-07—Публикация

1980-06-30—Подача