Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих устройств аналого-цифрового преобразования частоты в код.

Цель изобретения - повьппение помехозащищенности умножителя,

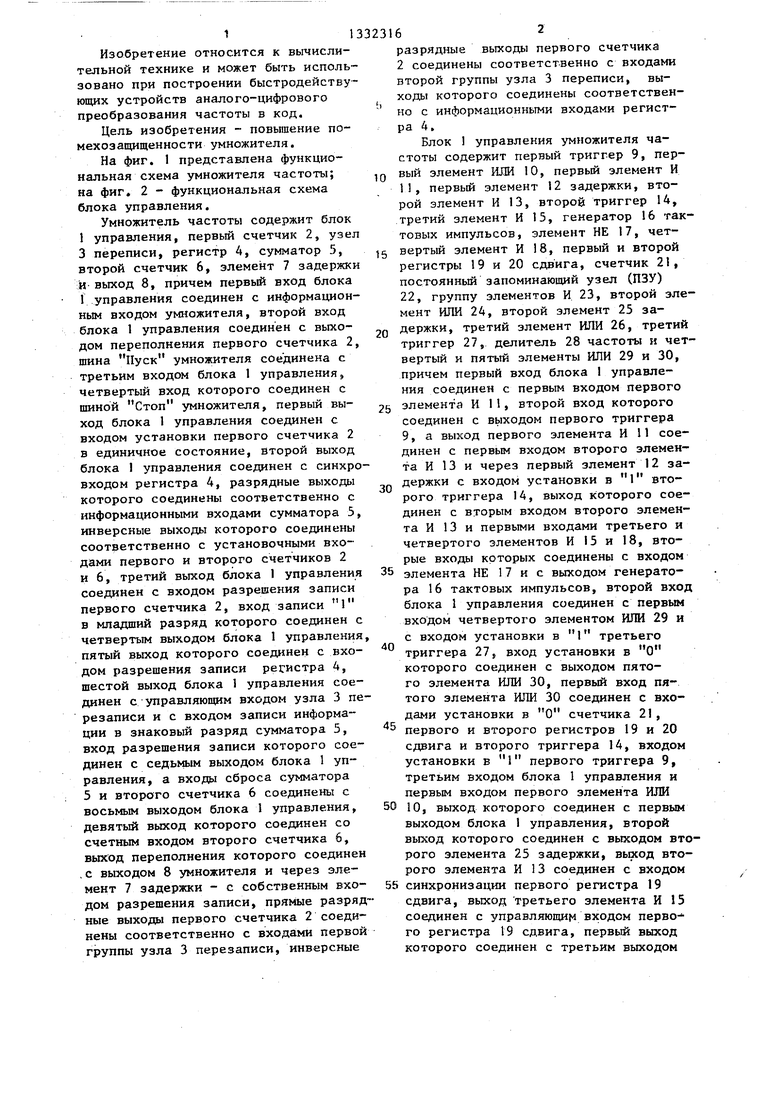

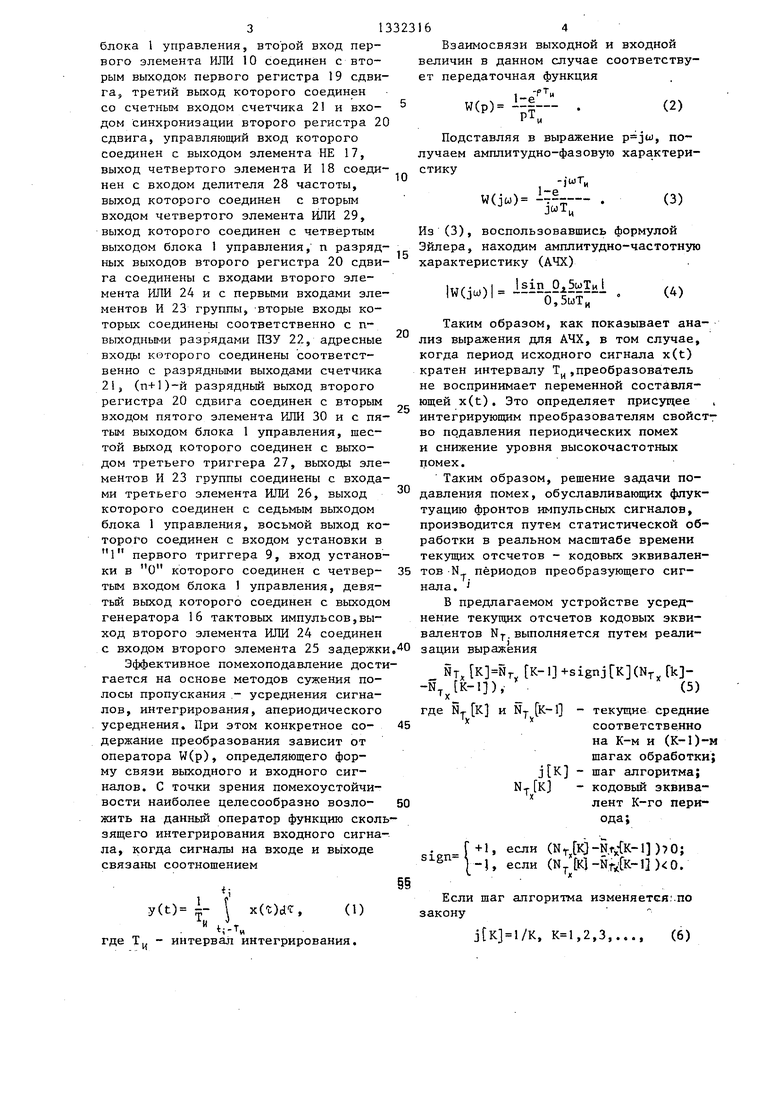

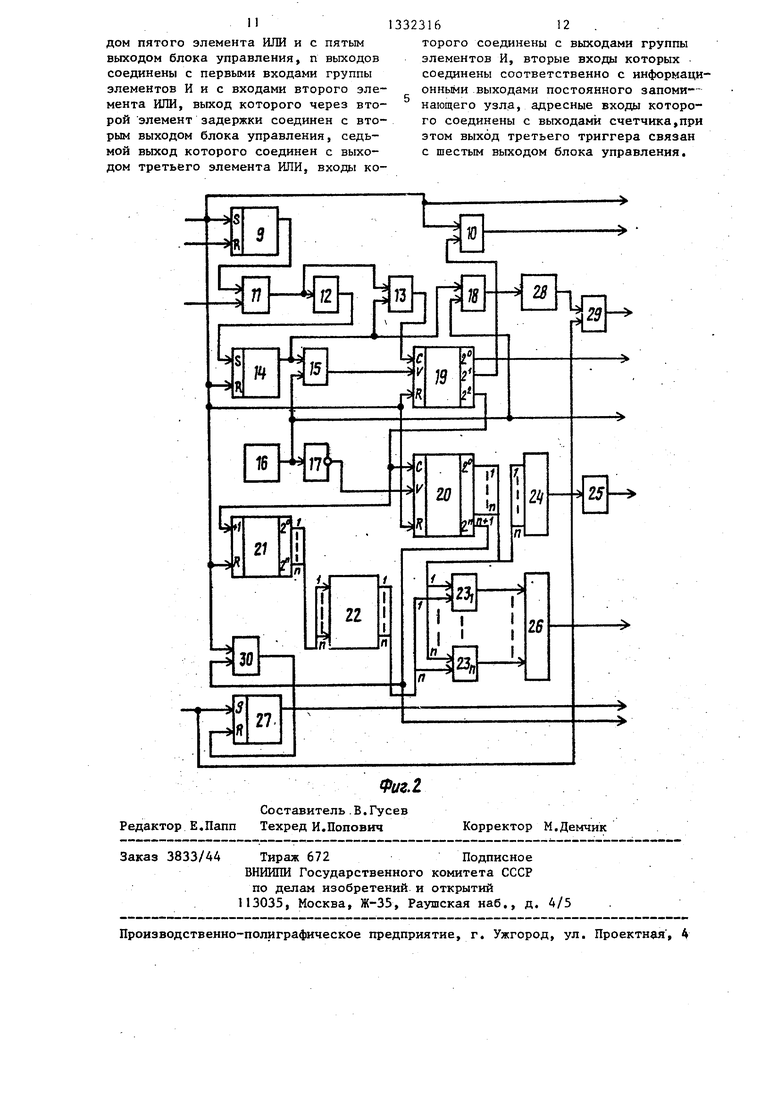

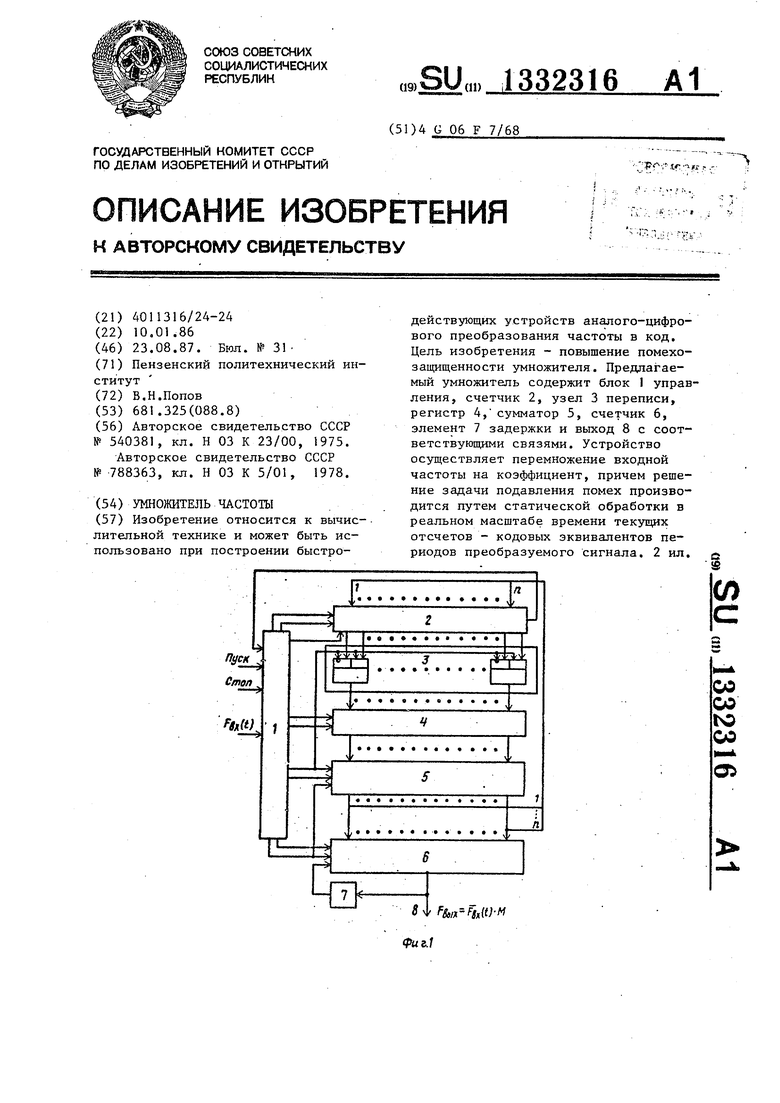

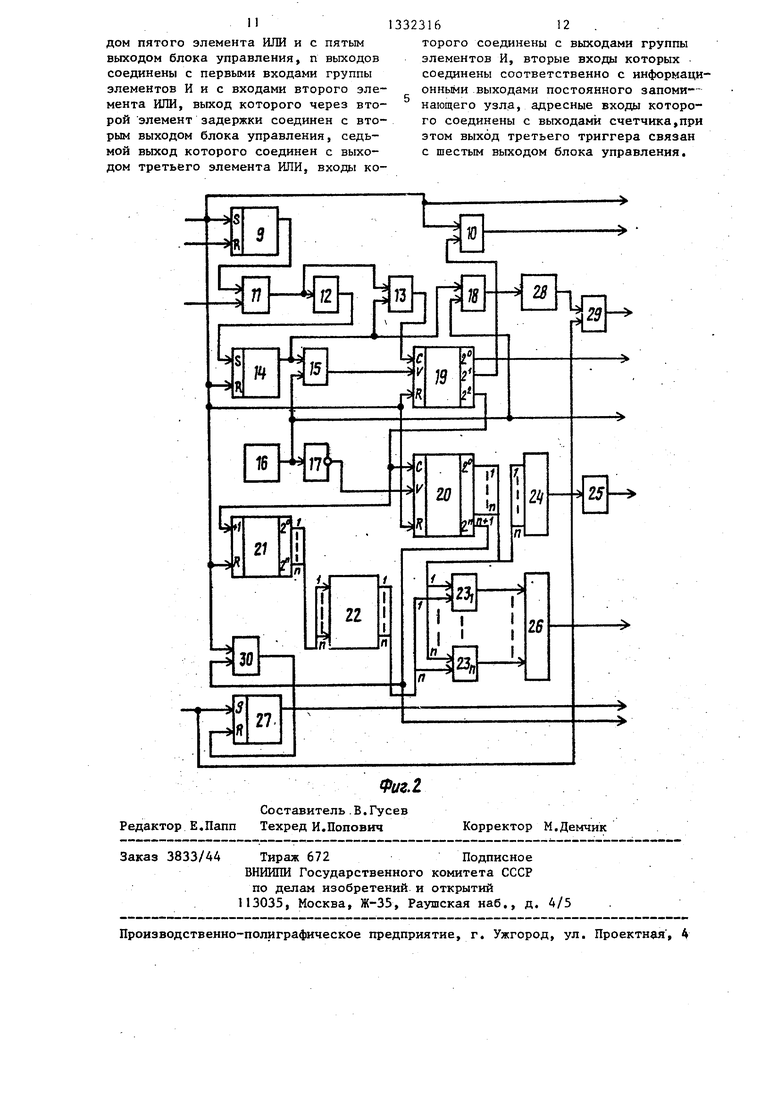

На фиг. 1 представлена функциональная схема умножителя частоты; на фиг. 2 - функциональная схема блока управления.

Умножитель частоты содержит блок 1 управления, первый счетчик 2, узел 3 переписи, регистр 4, сумматор 5, второй счетчик 6, элемент 7 задержки И вьпсод 8, причем первый вход блока 1 управления соединен с информационным входом умножителя, второй вход блока 1 управления соединен с выходом переполнения первого счетчика 2, шина Пуск умножителя соединена с третьим входом блока 1 управления, четвертый вход которого соединен с шиной Стоп умножителя, первый выход блока 1 управления соединен с входом установки первого счетчика 2 в единичное состояние, второй выход блока 1 управления соединен с синхро входом регистра 4, разрядные выходы которого соединены соответственно с информационными входами сумматора 5, инверсные выходы которого соединены соответственно с установочными входами первого и второго счетчиков 2 и 6, третий выход блока 1 управления соединен с входом разрешения записи первого счетчика 2, вход записи 1 в младший разряд которого соединен с четвертым выходом блока 1 управления пятый выход которого соединен с входом разрешения записи регистра 4, шестой выход блока 1 управления соединен с управляющим входом узла 3 перезаписи и с входом записи информации в знаковый разряд сумматора 5, вход разрешения записи которого соединен с седьк1ым выходом блока 1 управления, а входы сброса сумматора 5 и второго счетчика 6 соединены с восьмым выходом блока 1 управления, девятый выход которого соединен со счетным входом второго счетчика 6, выход переполнения которого соединен ,с выходом 8 умножителя и через элемент 7 задержки - с собственным входом разрешения записи, прямые разрядные выходы первого счетчика 2 соеди нены соответственно с входами первой группы узла 3 перезаписи, инверсные

0

разрядные выходы первого счетчика 2 соединены соответственно с входами второй группы узла 3 переписи, выходы которого соединены соответствен но с информационными входами регистра 4.

Блок управления умножителя частоты содержит первый триггер 9, перQ вый элемент ИЛИ 10, первый элемент И 11, первый элемент 12 задержки, второй элемент И 13, второй триггер 14, третий элемент И 15, генератор 16 тактовых импульсов, элемент НЕ 17, чет5 вертый элемент И 18, первый и второй регистры 19 и 20 сдвига, счетчик 21, постоянный запоминающий узел (ПЗУ) 22, группу элементов И 23, второй элемент ИЛИ 24, второй элемент 25 заQ держки, третий элемент ИЛИ 26, третий триггер 27, делитель 28 частоты и четвертый и пятый элементы ИЛИ 29 и 30, причем первый вход блока 1 управления соединен с первым входом первого

5 элемента И 11, второй вход которого соединен с выходом первого триггера 9, а выход первого элемента И И соединен с первым входом второго элемента И 13 и через первый элемент I2 задержки с входом установки в 1 второго триггера 14, выход которого соединен с вторым входом второго элемента И 13 и первыми входами третьего и четвертого элементов И 15 и 18, вторые входы которых соединены с входом

5 элемента НЕ 17нс выходом генератора 16 тактовых импульсов, второй вход блока 1 управления соединен с первым входом четвертого элементом ИЛИ 29 и с входом установки в I третьего триггера 27, вход установки в О которого соединен с выходом пятого элемента ИЛИ 30, первый вход пятого элемента ИЛИ 30 соединен с входами установки в О счетчика 21, первого и второго регистров 19 и 20 сдвига и второго триггера 14, входом установки в 1 первого триггера 9, третьим входом блока 1 управления и первым входом первого элемента ИЛИ

0 10, выход которого соединен с первым выходом блока 1 управления, второй выход которого соединен с выходом второго элемента 25 задержки, вьпсод второго элемента И 13 соединен с входом

5 синхронизации первого регистра 19 сдвига, вьпсод третьего элемента И 15 соединен с управляющим входом перво- го регистра 19 сдвига, первый выход которого соединен с третьим выходом

0

5

31

блока 1 управления, второй вход первого элемента ИЛИ 10 соединен с вторым выходом первого регистра 19 сдвига, третий выход которого соединен со счетным входом счетчика 2 и вхо- дом синхронизации второго регистра 20 сдвига, управляющий вход которого соединен с выходом элемента НЕ 17, выход четвертого элемента И 18 соединен с входом делителя 28 частоты, выход которого соединен с вторым входом четвертого элемента ИЛИ 29, выход которого соединен с четвертым выходом блока 1 управления, п разрядных выходов второго регистра 20 сдвига соединены с входами второго элемента ИЛИ 24 и с первыми входами элементов И 23 группы, -вторые входы которых соединены соответственно с п выходными разрядами ПЗУ 22, адресные входы которого соединены соответственно с разрядными выходами счетчика 21J (п+1)-й разрядный выход второго регистра 20 сдвига соединен с вторым входом пятого элемента ИЛИ 30 и с пятым выходом блока 1 управления, шестой выход которого соединен с выходом третьего триггера 27, выходь элементов И 23 группы соединены с входами третьего элемента ИЛИ 26, выход которого соединен с седьмым выходом блока 1 управления, восьмой выход которого соединен с входом установки в 1 первого триггера 9, вход установки в О которого соединен с четвер- тым входом блока 1 управления, девя- тьй выход которого соединен с выходом генератора 16 тактовых импульсов,выход второго элемента ИЛИ 24 соединен с входом второго элемента 25 задержки

Эффективное помехоподавление достигается на основе методов сужения полосы пропускания - усреднения сигналов, интегрирования, апериодического усреднения. При этом конкретное со- держание преобразования зависит от оператора W(p), определяющего форму связи выходного и входного сигналов. С точки зрения помехоустойчивости наиболее целесообразно возло- жить на данный оператор функцию скользящего интегрирования входного сигнала, когда сигналы на входе и выходе связаны соотношением

1 V

y(t) -- х(г)ае,

11 о

(1)

4:-Т„

где Т - интервал интегрирования.

164

Взаимосвязи выходной и входной величин в данном случае соответствует передаточная функция

1-е

:р

РТ.

(2)

Подставляя в выражение , поучаем амплитудно-фазовую характеристику

„(j,) ... . (3)

5

0

5

5 0

5 0

§

Из (3), воспользовавшись формулой Эйлера, находим амплитудно-частотную характеристику (АЧХ)

|«(з)|- о:5йг--

Таким образом, как показывает анализ выражения для АЧХ, в том случае, когда период исходного сигнала x(t) кратен интервалу Т, преобразователь не воспринимает переменной составляющей x(t). Это определяет присущее интегрирующим преобразователям свойство подавления периодических помех и снижение уровня высокочастотных помех.

Таким образом, решение задачи подавления помех, обуславливающих флуктуацию фронтов импульсных сигналов, производится путем статистической обработки в реальном масштабе времени текущих отсчетов - кодовых эквивалентов -N периодов преобразующего сигнала. J

В предлагаемом устройстве усреднение текущих отсчетов кодовых эквивалентов Nf.выполняется путем реализации выражения

NT, . К- 1 +signj К(NT, ),(5)

где Ny к и Nj К-1 - текущие средние соответственно

на К-м и (К-1)-м шагах обработки; - шаг алгоритма; NT к - кодовый эквивалент К-го периода;

,.,,+1. если (Nr,K)-Nr -CK-l)0; |-}, если (N Kl-Nr K-13)0.

Если шаг алгоритма изменяется;.по закону

, ,2,3,..., (6)

51332316

является оптимальным, так как текущего среднего совпадает с , определяемой в виде

жи га во пе та чи об ра

(с

КГк i И N . к J.1 J

Данный алгоритм известен как дискретный аналог интегратора.

Если jCK. в выражении (5) прини- мает постоянные значенияр начиная с г-го отсчета, то выходной сигнал связан с входным сигналом соотношением (1). При этом АЧХ данного эвена определяется как (4), что определяет помехоустойчивые свойства алгоритма (5).

Умножитель частоты работает следующим обраэом,

В начальный момент времени сигналом Пуск обеспечивается установка в исходное состояние триггеров 9, 14 и 27, счетчика 21, регистров 19 и 20 сдвига блока 1 управления. Данный сигнал сбрасывает в нулевое состояние также сумматор 5 и второй счетчик 6. Триггер 9 блока 1 управления устанавливается в единичное состояние. Затем сигнал проходит через элемент ИЛИ 10 блока 1 управления и поступает на вход установки счетчика 2 в единичное состояние.

Импульс входной последовательности Fj, поступая на первый вход блока 1 управления, проходит через открытый элемент И 11 и через элемент 12 эадержки поступает на S-вход триггера 14, который открывает элемент И 15. Так реализуется начальная синхронизация работы устройства с входной последовательностью. Каждый импульс входной последовательности, начиная с второго, через открытый элемент И 13 обеспечивае т запись 1 в младший разряд регистра 19 сдвига, мпульсы с выхода генератора 16 импульсов (опорной часто ты) через элеент И 15, после того как триггер 14 установится в единичное состояие, начинают поступать на управляюий вход регистра 19 сдвига. При этом единица начинает. последовательно продвигаться импульсами опорной астоты по разрядам регистра 59 сдвига, что обеспечивает формирование а его выходах последовательности сигналов управления, Сигнал с первого выхода регистра 19 сдвига, постуая на третий выход блока 1 управения, обеспечивает перепись содержимого счетчика 2 в регистр 4 (сдвига). Второй импульс управления с первого выхода блока 1 управления обеспечивает через элемент ИЛИ 10 установку в единичное состояние счетчика 2. Третий импульс управления обеспечивает запись 1 в младший разряд регистра 20 сдвига (по входу

синхронизации) и увеличивает содержимое счетчика 21 (импульсов) на единицу. Счетчик 21 вьтолняет функцию счетчика числа отсчетов, выходы которого подключены к адресным входам

ПЗУ 22, где хранятся значения шага алгоритма , представленные двоичными кодами, Дня первого отсчета, что следует из (6), , для второго отсчета ,5; для третьего ,333 и т.д. Каждый из , K(l,m), аппроксимируется двоичным рядом, т.е. представляется в виде суммы нормирующих множителей, кратных степеням двойки

, Г- -1)j. а..

1Г1

где а. - коэффициент участия двоичной дискреты в формирова- НИИ заданного значения .

Таким образом, каждый отсчет определяет соответствующую комбинацию единиц и нулевой на выходе ПЗУ 22, При этом единичные выходы открлшают

соответствующие элементы группы элементов И . Единица, эаписанная в младший разряд регистра 20 сдвига, начинает последовательно продвигаться по всем разрядам (число которых

на один больше числа разрядных выходов ПЗУ 22) импульсами опорного генератора j поступающими на управляющий вход через элемент НЕ 17, что обеспечивает исключение сбоев по фронтам

импульсов при работе обоих регистров сдвига. Каждый из импульсов, появивихся на выходе регистра 20 сдвига, поступает на второй вход соответствующего элемента И 23,-23 и одновреенно через многовходовой элемент ИЛИ 24 на вход элемента 25 задержки. В том случае;, если i-й элемент И 23- открыт по первому входу, то импульс с соответствующего выхода регистра 20

сдвига проходит через элемент ИЛИ 26 и поступает с седьмого выхода блока 1 управления на управляющий Вход суматора 5, обеспечивая подсуммирова- ние к его содержимому текущее содер71

жимое регистра 4. Элемент 25 задержки обеспечивает задержку импульсов на время, достаточное для надежной переписи (подсуммирования) из регистра А в сумматор 5. Каждый импульс с выхода элемента 25 задержки (второй выход блока 1 управления) осуществляет сдвиг содержимого регистра 4 на один разряд вправо, что обеспечива- ет деление содержимого регистра 4 на коэффициенты 2°, , 2,...,2. Посл того, как регистр 20 блока 1 управления сформирует п импульсов, к содержимому сумматора 5 добавляется содержимое регистра 4, умноженное на соответствующий шаг алгоритма. Процесс умножения на состоит в последовательном сдвиге содержимого регистра 4 и выборе на подсуммирова- ние в сумматор 5 каждого частного

л .

(NT.-NI. ) , для которого а- 1. (п+ +1)й импульс регистра 20 блока управления обеспечивает установку в нулевое состояние триггера 27 и пере пись содержимого сумматора 5 в счетчик 2 в обратном коде. В счетчике 2 реализуется операция (N.-N-p. ) и определение знака данной разности. В течение интервала времени, равно- го текущему периоду входной последовательности, через открытый элемент И 18, делитель 28 частоты и элемент ИЛИ 29 на счетньй вход счетчика 2 поступают импульсы опорной часто- ты FJ . Коэффициент деления делителя 28 импульсов равен коэффициенту М умножения устройства. Если имеет место случай NT T--FJ NT , то счетчик

м 1 3 111 2 не переполняется и триггер 27 бло-

ка 1 управления своего состояния не изменяет. Содержимое счетчика 2 (импульсов) при этом переписывается в регистр 4 через узел 3 переписи в обратном коде. В случа е, если NT T, , то к моменту окончания периода IV счетчик 2 переполняется, и импульс, формирующийся на выходе его старшего разряда, поступает на второй вход блока 1 управления, ус- танавливает триггер 27 в противоположное состояние и, кроме того, проходит через элемент ИЛИ 29 и четвертый выход блока 1 управления на счетньй вход счетчика 2. Это обеспечива- ет исключение погрешности, которая имеет место в случае использования обратного кода вместо дополнительно го.

16 ,8

Таким образом, в момент окончания очередного периода Т. входного сигнала Fg в счетчика 2 фиксируется модуль разности IN , а знак разности определяется сигналом на выходе триггера 27, Затем содержимое счетчика 2 переписывается в регистр 4, где осуг ествляется умножение I на соответствующее значение шага алгоритма j Г Результат выполнения данной операции суммируется с соответствующим знаком к содержимому сумматора 5,

Описанная последовательность операций, выполняемых в процессе работы устройства, обеспечивает вычисление текущего среднего кодового эквивалента периода входного сигнала в следующем виде: Nr,CK NTjK-ll+j K sign(NT,),

которое совпадает с выражением (5). Затем усредненное значение кодового эквивалента N периода входного сигнала подается в счетчик 6, где обеспечивается его преобразование. При этом на выходе умножителя частота следования импульсов определяется в виде

f k Ь:: где усредненньш период преобразуемого сигнала.

Таким .образом, частота следования импульсов выходного сигнала в предлагаемом устройстве пропорциональна усредненному за заданный интервал времени значению частоты входного сигнала,

Если шаг алгоритма после j-ro отсчета (период входного сигнала Fg) принять постоянным, то взаимосвязь входного и выходного сигналов определяется выражением (3). Следовательно, АЧХ предлагаемого устройства имеет нули в определенных точках оси частот, что и определяет способ- ность предлагаемой структуры подавлять периодические помехи, характеризующиеся линейчатым спектром, а также снижение уровня высокочастотных помех в высокочастотной части спектра полезного сигнала.

Формула изобретения

Умножитель частоты, содержащий первый и второй счетчики, узел пере

913

писи, регистр, сумматор, элемент за- держки и блок управления, первый вход которого соединен с информадионньм входом умножителяS первый вход блока управления соединен с входом установки первого счетчика в единичное состояние, второй выход блока управления соединен с синхровходом регистра, разрядные выходы которого соединены соот ветственно с информационньми входами сумматора, отличающий- с я тем, что, с целью повышения помехозащищенности умножителя, прямые разрядные выходы первого счетчика соединены соответственно с входами первой группы узла переписи, инверсные разрядные выходы первого счетчика соединены соответственно с входами второй группы узла переписи, выходы которо.го соединены соответственно с информационными входами ре1 истра5ин-- версные выходы сумматора соединен) соответственно с установочными входами первого и второго счетчиковj выход переполнения второго счетчика соединен с выходом умножителя и с входом элемента задержки, выход которого соединен с входом разрешения записи второго счетчика, третий выход блока управления соединен с входом разрешения записи первого счетчика, вход записи единицы в младший разряд которого соединен с четвертым выходом блока управления, пятый выход которого соединен с входом разрешения за- писи регистра, шестой выход блока управления соединен с управляющим входом узла переписи и с входом записи информации в знаковых разрядах сумматора, вход разрешения записи кото рого соединен с выходом блока управления, а входа сброса сумматора и второго счетчика соединены с восьмым выходом блока удразления, девятый выход которого сое,цинен со счетным входом второго счетчика, выход переполнения первого счетчика соединен с вторым входом блока управления, третий вход которого соединен с шиной Пуск умножителя, шина Стоп которого соединена с четвертым входом блока управления, который содержит первый, второй и третий .триггеры, первый, второй, третий, четвертый и пятый элементы ИЛИ, пер- вый, второй, третий и четвертый элементы И, первый и второй элементы задержки, генератор тактовых импуль-- сов, элемент НЕ, первый и второй ре

-,

20

323

. -Qjc354550 55 30

40

1610

гистры сдвига,, счетчик делитель частоты, постоянный запоминающий узел, группу элементов И, причем третий и четвертый входы блока управления соединены соответственно с входами установок в 1 и в О первого триггера, вход установки в которого соединен с первым входом первого элемента ИЛИ,, с восьмым выходом блока управления, с входами установок в нулевое состояние первого и второго ре гистров сдвига, входами установок в О второго триггера и счетчика, первым входом пятого элемента ИЛИ, выход которого соединен с входом установки в О третьего триггера, вход установки в l которого соединен с вторьм входом блока управления, объединенным с первым входом четвертого элемента ИЛИ, выход которого соединен с четвертым выходом блока управления, второй вход четвертого элемента ИЛИ соединен с выходом делителя частоты, вход которого, соединен с выходом четвертого элемента И, первьш вход которого соединен с первьами входами второго и третьего элементов И и выходом второго триггера 5 вход установки в которого соединен с выходом первого элемента задержки, вход которого соединен с вторым входом второго элемента И, выходом первого элемента И, первый вход которого соединен с выходом первого триггера, второй вход первого элемента И соединен с первым входом блока управления, первый выход которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с вторым выходом первого регистра сдвига, первый выход которого соединен с третьим выходом блока управления, третий выход первого регистра сдвига соединен со счетным входом счетчика и входом синхронизации второго регистра сдвига, вход синхронизации первого регистра сдвига соединен с выходом второго элемента И, управляющий вход первого регистра сдвига соединен с выходом третьего элемента И, второй вход которого соединен с вторым входом четвертого элемента И, девятым выходом блока управления, выходом генератора тактовых импульсов и входом элемента НЕ 5 выход которого соединен с управляющим входом второго регистра сдвига, выход старшего (п+1)-го разряда которого соединен с вторым вхо11

дом пятого элемента ИЛИ и с пятым выходом блока управления, п выходов соединены с первыми входами группы элементов И и с входами второго эле мента ИЛИ, выход которого через второй элемент задержки соединен с вторым выходом блока управления, седьмой выход которого соединен с выходом третьего элемента ИЛИ, входы коРедактор Е,Папп

Фиг.1

Составитель.В.Гусев Техред И.Попович

Заказ 3833/44 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная , 4

133231612 .

торого соединены с выходами группы элементов И, вторые входы которых соединены соответственно с информационными выходами постоянного запоми - нающего узла, адресные входы которого соединены с выходами счетчика,при этом выход третьего триггера связан с шестым выходом блока управления.

Корректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор широкополосных случайных процессов | 1980 |

|

SU881743A1 |

| Устройство для измерения частоты | 1988 |

|

SU1550434A1 |

| Измеритель девиации частотных сигналов | 1985 |

|

SU1352389A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Умножитель-нормализатор частотныхСигНАлОВ | 1979 |

|

SU847505A1 |

| Умножитель частоты | 1988 |

|

SU1562908A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстро/7y«f Степ fh(t) действующих устройств аналого-цифрового преобразования частоты в код. Цель изобретения - повышение помехозащищенности умножителя. Предлагаемый умножитель содержит блок 1 управления, счетчик 2, узел 3 переписи, регистр 4, сумматор 5, счетчик 6, элемент 7 задержки и выход 8 с соответствующими связями. Устройство осуществляет перемножение входной частоты на коэффициент, причем решение задачи подавления помех производится путем статической обработки в реальном масщтабе времени текущих отсчетов - кодовых эквивалентов периодов преобразуемого сигнала. 2 ил. с S (Л 00 со ю оо сз

| Умножитель частоты следования импульсов | 1975 |

|

SU540381A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-08-23—Публикация

1986-01-10—Подача