Изобретение относится к радиотехнике и может использоваться в аппаратуре передачи цифровой информации импульсно-кодовой модуляцией и дельтамодуляцией. Известен регенератор цифрового сиг нала, содержащий последовательно соединенные усилитель-корректор, блок вычитания, решающий блок, другой вход которого соединен с выходом усилителя-корректора через блок тактовой синхронизации, и формирователь выходных импульсов, а также пороговой детектор, включенный между выходом усилителя-корректора и входом опорного сигнала блока вычитания ll. Однако данный регенератор цифрового, сигнала обладает недостатком, заключающимся в низкой помехоустойчивости , который обусловлен несовершенством схемы формирования порогового напряжения. Величина этого напряжения зависит от статистики входного цифрового сигнала регенератора, и при нера новероятном появлении единиц и нулей меняется, что приводит к снижению помехоустойчивости регенератора цифровых сигналов. Цель изобретения - повышение поме хоустойчивости регенератора цифрового сигнала. Для достижения поставленной цели в регенератор цифрового сигнала, содержащий последовательно соединенные усилитель-корректор, блок вычитания, решающий блок, другой вход которого соединен с выходом усилителя-корректора через блок тактовой синхронизации, и формирователь выходных импульсов, введены компаратор, блок анапи-. за, реверсивный счетчик и резистивная матрица, которые соединены последовательно, и счетчик импульсов, при этом один из входов компаратора соединен с выходом блока вычитания, а другой объединен со входом опорного сигнала блока вычитания и соединен с выходом резистивной матрицы, выход

.{j-:W(ifii4ercj ( подсоединен ; стробируадцему входу компаратора и через счетчЬК 1и.1пульсо8 ко входу сброса блока зизлиза.

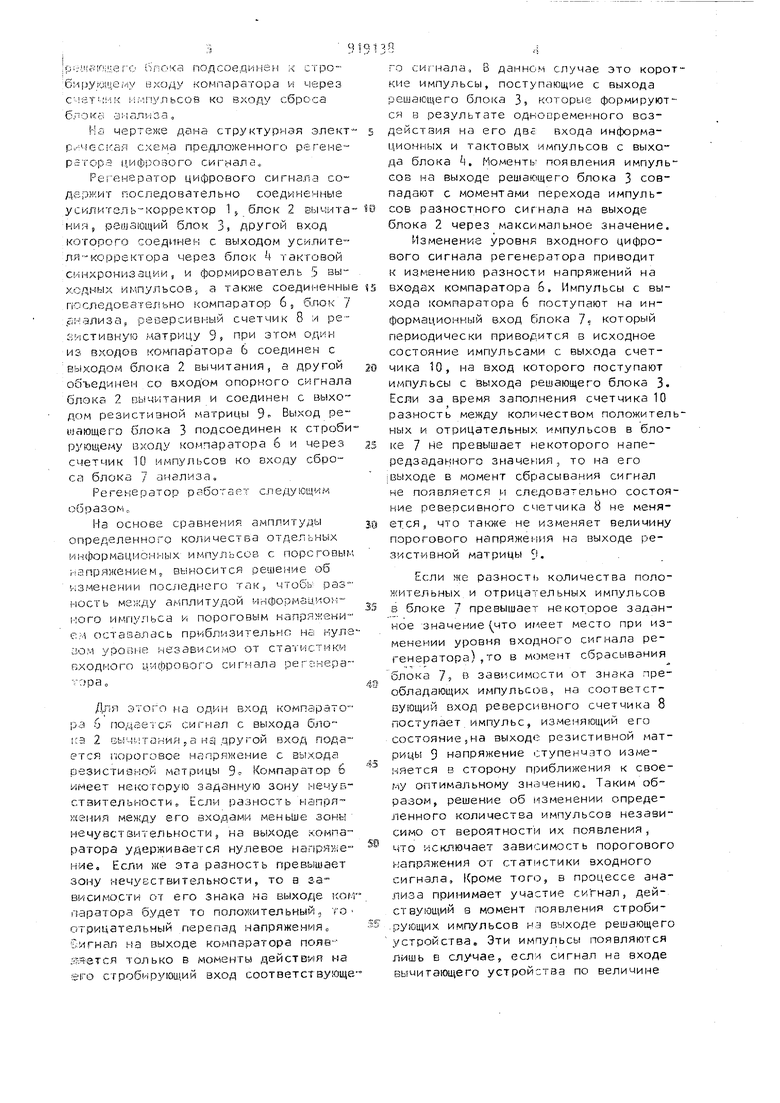

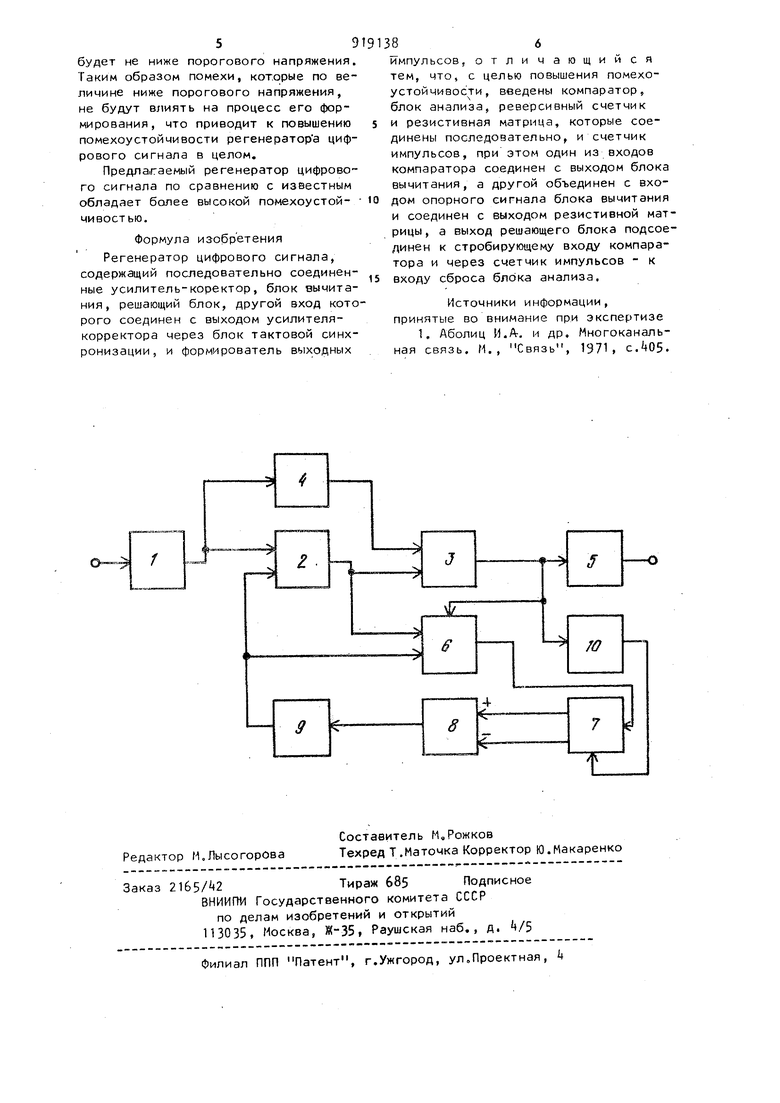

На чертеже дана структурная элеку рическая схема предложенного регенв pSTOpa | ифрозого сигнала.

Регенератор цифрового сигнала содержит последовательно соединенные усилитель-корректор 1 блок 2 вычита ния, решающий блок 3, другой вход которого соединен с выходом усилителя-корректора через блок ч тактовой синхронизации, и формирователь 5 выходных импульсов, а также соединенны последовательно компаратор бэ блок 7 анализа, реверсивный счетчик 8 и резистивную матрицу 9; при этом один из входов компаратора 6 соединен с выходом блока 2 вычитания, а другой объединен со входом опорного сигнала блока 2 Езычитания и соединен с выходом резистизной матрицы 9 Выход решающего блока 3 подсоединен к стробирующему входу компаратора 6 и через счетчик 10 импульсов ко входу сброса блока 7 анализа.

Регенератор работает следующим образом„

На основе сравнения амплитуды

определенного количества отдельных ин рормзционных импульсов с пороговым напряжением, выносится решение об (-сзменении последнего так, чтобк разность между амплитудой информационного импульса и пороговым напряжением оставалась приблизительно на нулезом уровне независимо от статистики входного цифрового сигнала реганера эра„

Д/1я этого на один вход компаратора б подается сигнал с выхода бло ica 2 вычитания .а HS другой вход подается rioporoBoe напряжение с выхода резистизной матрицы 9 Компаратор 6 имеет некоторую заданную зону ыечувствительиости, Если разность напряжения между его входами меньше зоны нечуаст-зительиости э на выходе компаратора удерживается нулевое напряжв ние. Если же эта разность гфевышает зону нечувствительности, то а зависимости от его знака на выходе компаратора будет то положительный 5 то отрицательный перепад напряжения„Еигнал на выходе компаратора появкается только в моменты действия на его стробирующий вход соответствующе

го сигтнала, В данном случае это корокие импульсы, поступающие с выхода решающего блока 3, которые формируются в результате однооременного воздейстаия на его двг входа информационных и тактовых импульсов с выхода блока , Моменть появления импульсов на выходе решающего блока 3 совпадают с моментами перехода импульсов разностного сигнала на выходе блока 2 через максимальное значение. Изменение уровня входного цифрового сигнала регенератора приводит к изменению разности напряжений на входах компаратора 6. Импульсы с выхода компаратора 6 поступают на информационный вход блока 7. который периодически приводится в исходное состояние импульсами с выхода счетчика 10, на вход которого поступают импульсы с выхода решающего блока 3. Если за время заполнения счетчика 10 разность между количеством положителных и отрицательных импульсов в бло1се 7 не превышает некоторого напередзаданного значения, то на его Выходе в момент сбрасывания сигнал не появляется и следовательно состояние реверсивного счетчика 8 не меняется, что также не изменяет величину порогового напряже1- ия на выходе резистивной матрицы 9.

Если же разность количества положительных и отрицательных импульсов в блоке 7 превышает некоторое заданное значение (цто и.еет место при изменении уровня входного сигнала регенератора) ,то в момент сбрасывания блока 7 в зависимости от знака преобладающих импульсов, на соответствующий вход реверсивного счетчика 8 поступает,импульс, изменяющий его состояниегна выходе резистивной матрицы 9 напряжение ступенчато изменяется в сторону приближения к своему оптимальному значению. Таким образом решение об изменении определенного количества импульсоа независимо от вероятности их появления, что исключает зависиглость порогового напряжения от стат11стики входного сигнала. Кроме того, в процессе анализа принимает участие сигнал, действующий в момент появления стробирующих импульсов на выходе решающего устройства Эти импульсы появляются лишь в случае, если сигнал на входе вычитагоц его устройства по величине

59

будет не ниже порогового напряжения. Таким образом помехи, которые по величине ниже порогового напряжения, не будут влиять на процесс его формирования, что приводит к повышению помехоустойчивости регенератора цифрового сигнала в целом.

Предлагаемый регенератор цифрово™ го сигнала по сравнению с известным обладает более высокой помехоустойчивостью.

Формула изобретения Регенератор цифрового сигнала, содержащий последовательно соединенные усилитель-коректор, блок вычитания, решающий блок, другой вход которого соединен с выходом усилителякорректора через блок тактовой синхронизации, и формирователь выходных

386

Импульсов, отли чающийся тем, что, с целью повышения помехоустойчиаос;ти, введены компаратор, блок анализа, реверсивный счетчик и резистивная матрица, которые соединены последовательно, и счетчик импульсов, при этом один из входов компаратора соединен с выходом блока вычитания, а другой объединен с входом опорного сигнала блока вычитания и соединен с выходом резистивной матрицы, а выход решающего блока подсоединен к стробирукнцему входу компаратора и через счетчик импульсов - к входу сброса блЬка анализа.

Источники информации, принятые во внимание при экспертизе

1, Аболиц И.А-. и др. Многоканальная связь. М. , Связь, 1971, с.05.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регенератор цифрового сигнала | 1984 |

|

SU1239881A1 |

| Устройство для адаптивной настройки корректора межсимвольных искажений | 1977 |

|

SU743212A1 |

| Регенератор цифрового сигнала | 1982 |

|

SU1083351A1 |

| Регенератор цифрового сигнала | 1981 |

|

SU987838A1 |

| Регенератор цифрового сигнала | 1986 |

|

SU1381728A1 |

| Регенератор цифрового сигнала | 1986 |

|

SU1390792A1 |

| Регенератор бинарных сигналов | 1987 |

|

SU1467773A1 |

| Устройство тактовой синхронизации | 1987 |

|

SU1540019A1 |

| Резервированный усилитель | 1987 |

|

SU1434568A1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛОВ | 2009 |

|

RU2422982C2 |

Авторы

Даты

1982-04-07—Публикация

1980-07-25—Подача