N

О5

|

оо

Изобретение относится к радиотехнике и .связи и может быть использовано в качестве регенеративных трансляторов в цифровых системах передачи данных.

Целью изобретения является повышение точности регенерации.

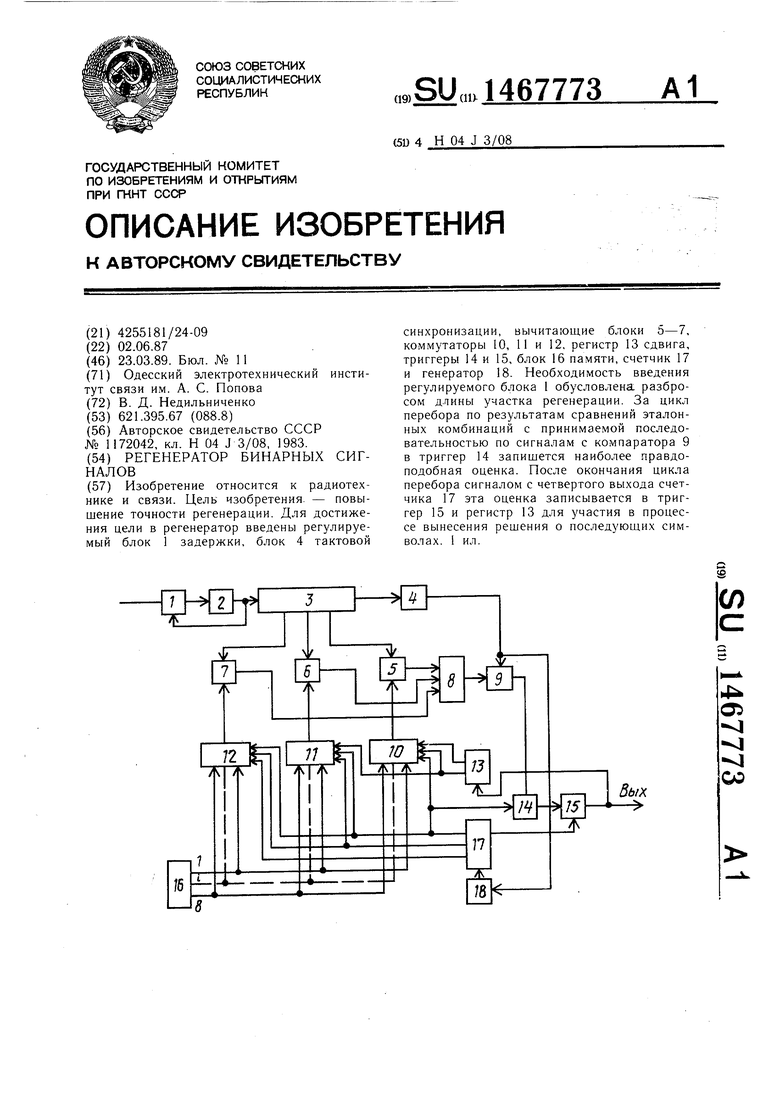

На чертеже приведена структурная электрическая схема регенератора бинарных сигналов.

Регенератор содержит регулируемый блок 1 задержки, корректирующий усилитель 2, блок 3 задержки, блок 4 тактовой синхронизации, первый 5, второй 6 и третий 7 вычитающие блоки, сумматор 8, компаратор 9, первый 10, второй 11 и третий 12 коммутаторы, регистр 13 сдвига, первый 14 и вто рой 15 триггерь, блок 16 памяти, счетчик 17 и генератор 18.

Регенератор бинарных сигналов работает следующим образом.

Принимаемые отсчеты сигнала, пройдя регулируемый блок 1 и корректирующий усилитель 2, поступают в блок 3. Необходимость введения регулируемого блока 1 обусловлена разбросом длины участка регенерации. Отсчеты сигнала с отводов блока 3, изменения в которых осуществляются на границе тактовых интервалов, поступают

на первые входы первого 5, второго 6 и третьего 7 вычитающих блоков, на входы которых поступают эталонные сигналы. С выходов вычитающих блоков 5-7 сигналы разности поступают на сумматор 8, на выходе которого образуется мера отклонения между принимаемой и эталонной последовательностями сигналов. В качестве меры отклонения может быть взят, к примеру, модуль разности или квадрат разности соответствующих сигналов.

За время, не превышающее длительность тактового интервала, принимаемая последовательность должна сравниться с эталонными последовательностями, число которых определяется длиной блока 3 и длиной отклика. Число возможных значений эталонных сигналов определяется длиной отклика. Их значения хранятся в блоке 16, выходы которого соединены с информационными входами первого 10, второго 11 и третьего 12 коммутаторов. В начале тактового интервала сигналом с блока 4 запускается генератор 18, который генерирует последовательность импульсов, поступающих на вход счетчика 17 с соответствующим коэффициентом пересчета. С помощью счетчика 17 и регистра 13 реализуется прием с обратной связью по решению. В этом случае принимаемая последовательность сигналов сравнивается не с всевозможными комбинациями эталонных сигналов, а лищь с частью из них, так как в регистре 13 хранятся оценки принятых сигналов, считающиеся известными переданными символами.

Таким образом, принимаемая последовательность сигналов сравнивается с комбинациями эталонных сигналов, которые определяются значениями счетчика 17 и регистра 13. Одновременно с запуском генератора 18 сигнал из блока 4 в начале тактового интервала устанавливает в исходное состояние компаратор 9. После вычитания из принимаемой последовательности сигналов первой эталонной комбинации

образованная мера отклонения записывается в элемент памяти компаратора 9, а на его выходе появляется сигнал, которым через управляющий вход первого триггера 14 значение с первого отвода счетчика 17

записывается в первый триггер 14. Через определенное время на выходе сумматора образуется мера отклонения следующей эталонной комбинации сигналов, которая сравнивается с мерой, хранящейся в элементе памяти компаратора 9. Если мера отклонения, полученная на данном шаге, меньще меры, записанной в элементе памяти, то на выходе компаратора 9 появляется сигнал, которым эта меньшая мера записывается в элемент памяти компаратора 9, а в первый триггер 14 - более правдоподобная оценка с первого отвода счетчика 17. Если мера отклонения, полученная на данном шаге, больше той, что записана в элементе памяти, никаких изменений не происходит. Таким образом, за цикл перебора по

результатам сравнений эталонных комбинаций с принимаемой последовательностью по сигналам с компаратора 9 в первый триггер 14 запишется наиболее правдоподобная оценка. После окончания цикла перебора сигналом с четвертого выхода

четчика 17 эта оценка записывается во второй триггер 15 и регистр 13 для участия в процессе вынесения решения о последующих символах.

Форм1 ла изобретения Регенератор бинарных сигналов, содержащий сумматор и последовательно соединенные корректирующий усилитель и блок задержки, отличающийся тем, что, с целью повышения точности регенерации, введены регулируемый блок задержки, три вычитающих блока, три коммутатора, блок памяти, регистр сдвига, компаратор, последовательно соединенные блок тактовой синхронизации, генератор и счетчик и последовательно соединенные первый триггер и второй триггер, выход которого подключен к вхоДУ- регистра сдвига, первый и второй выходы которого подключены к первому и второму управляющим входам первого коммутатора, второй выход регистра сдвига подключен к первому управляющему входу вто рого коммутатора, второй и третий

управляющие входы которого попарно объединены с первым и вторым управляющими входами третьего коммутатора и подключены к соответствующим первому и вто

рому выходам счетчика, первый выход которого подключен к первому входу первого триггера и третьему управляющему входу первого коммутатора, третий выход счетчика подключен к однолинейному управляющему входу третьего коммутатора, а четвертый выход счетчика соединен с вторым входом второго триггера, одноименные информационные входы первого, второго и третьего коммутаторов объединены и подключены к соответствующим выходам блока памяти, выходы первого, второго и третьего коммутаторов подключены к первым входам соответствующих первого, второго и третьего вычитающих блоков, вторые входы которых подключены к соот

ветствующим первому, второму и третьему выходам блока задержки, четвертый выход которого соединен с входом блока тактовой синхронизации, выход которого подключен к первому входу компаратора, второй вход которого соединен с выходом сумматора, первый, второй и третий входы которого подключены к выходам соответствующих первого, второго и третьего вычитающих блоков, причем выход компаратора подключен к второму входу первого триггера, а выход регулируемого блока задержки подключен к входу корректирующего усилителя, выход которого соединен с управляющим входом регулируемого блока задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема бинарных сигналов | 1986 |

|

SU1385320A1 |

| Регенератор бинарных сигналов | 1987 |

|

SU1434553A1 |

| УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ С ИСПОЛЬЗОВАНИЕМ МНОГОМЕРНЫХ МЕТРИЧЕСКИХ ПРОСТРАНСТВ | 2005 |

|

RU2288498C1 |

| Устройство для декодирования сверточного кода | 1991 |

|

SU1839281A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1990 |

|

RU2010455C1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1564693A1 |

Изобретение относится к радиотехнике и связи. Цель изобретения. - повышение точности регенерации. Для достижения цели в регенератор введены регулируемый блок 1 задержки, блок 4 тактовой синхронизации, вычитающие блоки 5-7, коммутаторы 10, II и 12. регистр 13 сдвига, триггеры 14 и 15, блок 16 памяти, счетчик 17 и генератор 18. Необходимость введения регулируемого блока 1 обусловлена разбросом длины участка регенерации. За цикл перебора по результатам сравнений эталонных комбинаций с принимаемой последовательностью по сигналам с компаратора 9 в триггер 14 запишется наиболее правдоподобная оценка. После окончания цикла перебора сигналом с четвертого выхода счетчика 17 эта оценка записывается в триггер 15 и регистр 13 для участия в процессе вынесения решения о последующих символах. 1 ил.

| Устройство для регенерации цифрового сигнала с компенсацией межсимвольных искажений | 1984 |

|

SU1172042A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-03-23—Публикация

1987-06-02—Подача